很多人可能觉得PCB信号速率越高,如25Gbps,56G/112G-PAM4信号等调试上发现的问题会越多,其实不然。我们收到最多的调试问题还是DDR3、DDR4等,不是跑不到额度速率,就是识别不到

2026-01-05 15:46:16

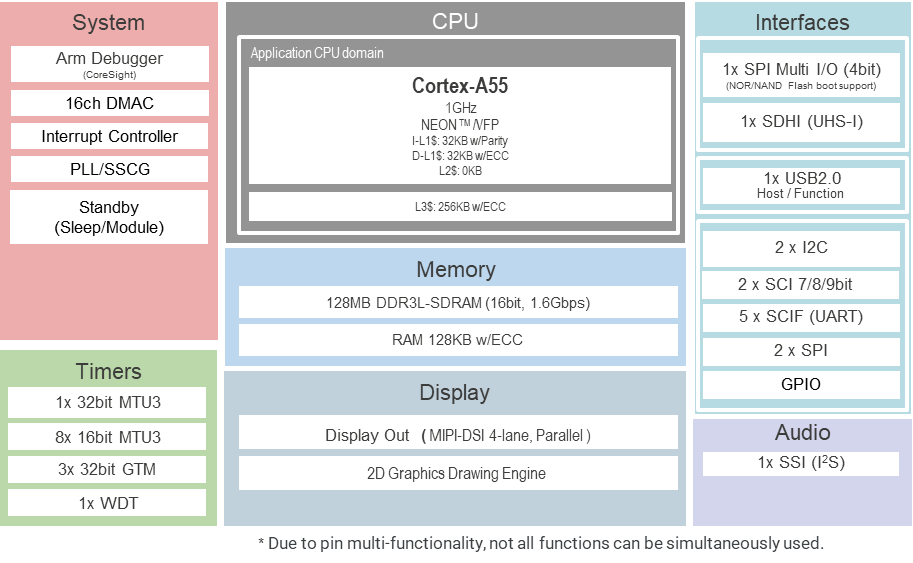

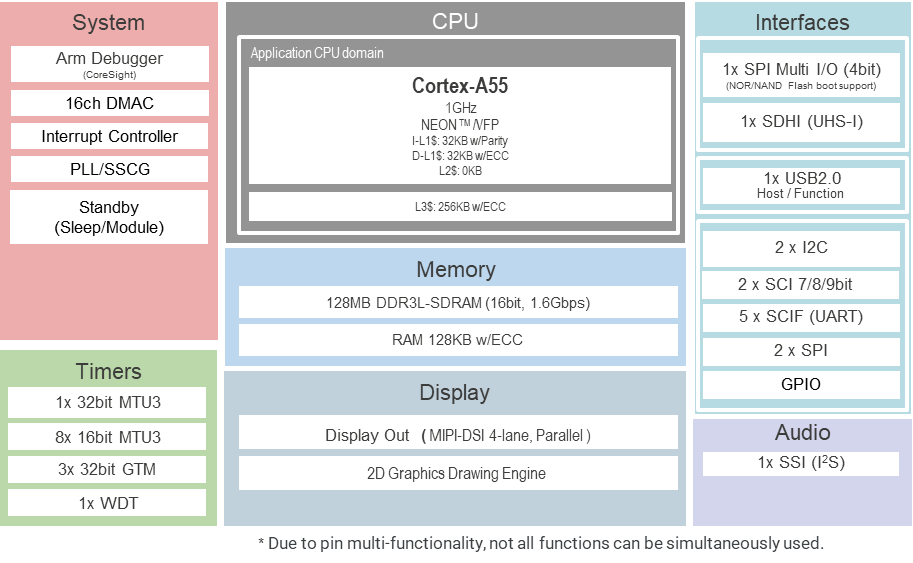

RZ/A3MHMIMPU对于高质量图形显示的应用要求,用户通常采用功能强大及搭载DDR高速接口的MPU来实现更多功能和更流畅的画面。但在开发过程会遇到DDR高速总线设计的难题,同时Linux系统

2025-12-24 12:06:10 300

300

在现代高速数字通信系统中,眼图分析是评估信号完整性和传输质量的核心工具。泰克示波器凭借其高精度和丰富的分析功能,成为工程师进行眼图测试的首选设备。本文将详细介绍使用泰克示波器进行眼图分析的完整流程,涵盖基础操作步骤、关键参数设置及高级分析技巧,帮助用户高效获取信号质量评估结果。

2025-12-10 17:26:53 938

938

Nikon SLM Solutions使用CADENAS解决方案迁移了8600多个零部件并优化了设计工程流程

Nikon SLM Solutions公司依靠3Dfindit企业版实现了高效、高质量

2025-11-25 10:06:10

本章的实验任务是在 PL 端自定义一个 AXI4 接口的 IP 核,通过 AXI_HP 接口对 PS 端 DDR3 进行读写测试,读写的内存大小是 4K 字节。

2025-11-24 09:19:42 3467

3467

DDR 作为 RK 平台数据传输的 “主动脉”,其稳定性与性能直接决定产品体验。尤其在内存颗粒迭代快、多场景应用普及的当下,一套通用且精准的 DDR 测试方法,能有效规避兼容性问题、提前发现隐性故障

2025-11-19 07:08:56 291

291

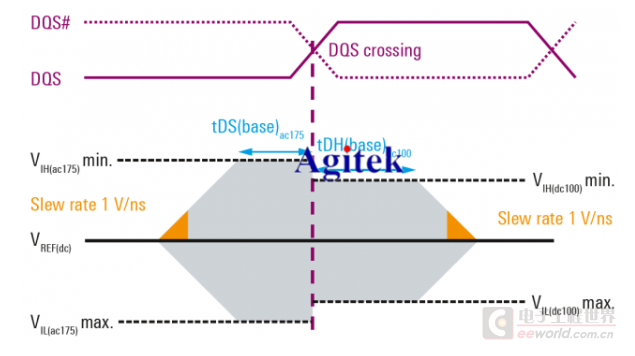

失真,影响数据的正确传输。DDR training通过自适应的机制来补偿这些信号完整性问题,确保数据链路的可靠性。

2025-11-17 10:25:33 3397

3397

下面是HummingBird EV Kit给的版图,其中DDR3_D0对应的应该是板子上的FPGA的C2引脚:

不过我在配置MIG的时候,通过读入ucf文件的方式配置DDR3 SDRAM的引脚

2025-11-06 07:57:09

电子发烧友网站提供《DDR3 SDRAM参考设计手册.pdf》资料免费下载

2025-11-05 17:04:01 4

4 )

MM2S_LENGTH0x0028DMA写数据长度(字节为单位)

具体连接图如下,由于本次使用的总线为50MHz,DMA时钟为50M;DDR3 ui_clk为100MHz;e203这里使用了10MHz。时钟的转换完全

2025-10-29 08:21:10

,如果用ARM处理器或上位机来实现这个过程会十分耗时,利用FPGA的并行处理技术可以轻易实现这个功能,整理后的数据传输形式会为之后的设计产生便利。模块用了20块片内双口RAM来实现数据的缓存,同时完成数据

2025-10-29 08:09:01

10MHz,并通过AXI-Inerconnect进行跨时钟处理,具体连接如下

其中ui_clk连接到M01_ACLK端口,clk_16M连接到S00_ACLK。测试程序如下,

本程序向MIG写入100个数据,再将其读出,如果写入与读出一致,则打印正确标识。经过测试,DDR3工作正常。

2025-10-29 07:16:34

文件夹内,打开文件夹。阅读readme说明文档,我们能够知道,原作者采用了vivado MIG IP来控制开发板上的DDR3,由于芯来科技的E203平台系统片内总线是icb总线,所以我们需要做跨时钟域

2025-10-28 07:25:32

DDR使用

在我们的项目中,我们使用的是芯来科技的DDR200T开发板,我们通过调用板上的DDR3 IP核完成如下表的配置,配置完成后例化该DDR3,然后利用DMA和VDMA作为数据的缓冲模块,将

2025-10-28 07:24:01

Tektronix提供针对PCIe 6.0 CEM测试的 比特误码率测试仪 (BERT) 接收端 (RX) 受限眼图自动校准。该软件名为TekRXTest,并支持额外的功能,例如RX表征与裕量测试

2025-10-24 16:16:54 3828

3828

数据的从icb协议转到axi协议。axi_interconnect实现了数据的跨时钟域和位宽转换,并将转换后的数据传给mig模块进而实现对DDR3的控制。

简单阅读蜂鸟的代码发现,蜂鸟本身提供了外部

2025-10-24 08:12:53

的S00_AXI_ACLK、M00_AXI_ACLK,分别接系统顶层时钟hfextclk、mig产生的用户时钟ui_clk,以此来实现跨时钟域。

(2)例化DDR3模型(仿真的时候需要用,vivado

2025-10-24 07:25:00

环境:Vivado2021.1、NucleiStudio_IDE_202102-win64

内容:简单讲解下利用vivado来调用控制模块,以实现ov7725摄像头的视频数据流传输。

首先设计顶层

2025-10-24 06:53:17

] correct : %drn”,i,rd_data);

ddr_offset += 0x00000004;

}

(2)测试效果,读数正确

vivado综合:

注意:(1)综合不需要例化ddr3模型,将

2025-10-23 06:16:44

本篇将详细介绍如何利用Verilog HDL在FPGA上实现SRAM的读写测试。SRAM是一种非易失性存储器,具有高速读取和写入的特点。在FPGA中实现SRAM读写测试,包括设计SRAM接口模块

2025-10-22 17:21:38 4118

4118

DDR控制协议

DDR3读写控制器主要用于生成片外存储器DDR3 SDRAM进行读写操作所需要的时序,继而实现对片外存储器的读写访问。由摄像头采集得到的图像数据通常数据量较大,使用片内存储资源

2025-10-21 14:30:16

IP DDR3控制器 RISC-V

基于DDR200T开发板原理图,找到所需要使用的DDR引脚,制成DDR.ucf文件方便在添加管脚约束时使用。在使用MIG IP核时,为了方便使用DDR产生的时钟

2025-10-21 12:43:40

蜂鸟DDR200T中DDR3的ip配置案列,提供DDR3引脚配置。具体参数可更具项目实际更改。

这里选用的axi接口

在赛灵思的IP配置中没有MT41K28M6JT-125K内存的信息,因此选用

2025-10-21 11:19:08

DDR3读写控制器主要用于生成片外存储器DDR3 SDRAM进行读写操作所需要的时序,继而实现对片外存储器的读写访问。由摄像头采集得到的图像数据通常数据量较大,使用片内存储资源难以实现大量图像数据

2025-10-21 10:40:28

DDR3读写控制器主要用于生成片外存储器DDR3 SDRAM进行读写操作所需要的时序,继而实现对片外存储器的读写访问。由摄像头采集得到的图像数据通常数据量较大,使用片内存储资源难以实现大量图像数据

2025-10-21 08:43:39

回收DDR2,回收DDR3,收购DDR2,收购DDR3 DDR4 DDR5长期现金高价回收DDR,回收三星DDR,回收海力士DDR,回收南亚DDR,回收尔必达DDR,回收美光DDR,回收DDR

2025-10-09 14:15:34

速率6400Mbps时数据信号写眼图从仿真结果可以看出,速率提升到6400Mbps时,长stub的L14层走线信号眼图急剧变差,眼高和眼宽都明显小于短stub的L5层走线,说明DDR5的数据信号还是要

2025-09-28 11:25:04

电能质量在线监测装置重启前的安全防护检查与日常运行时的检查,核心差异源于 检查目标、时机、操作场景的本质不同 : 重启前检查是 “ 事前预防性检查 ”,聚焦 “避免重启操作引发安全事故(如触电、设备

2025-09-23 14:38:47 339

339

EasyGo DeskSim是一款配置型的实时仿真软件,它允许用户将 Simulink 算法程序快速部署到 EasyGo 实时仿真机上。实时仿真机支持选配不同的 FPGA 芯片和 IO 模块,能够处理高速信号,并通过 IO 模块输出真实的仿真结果,可满足用户在科研、教学或工业测试中的多样化需求。

2025-09-10 17:48:49 740

740

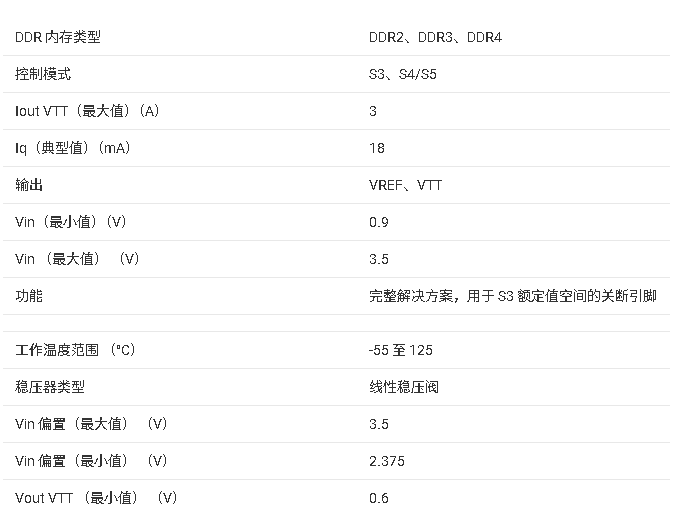

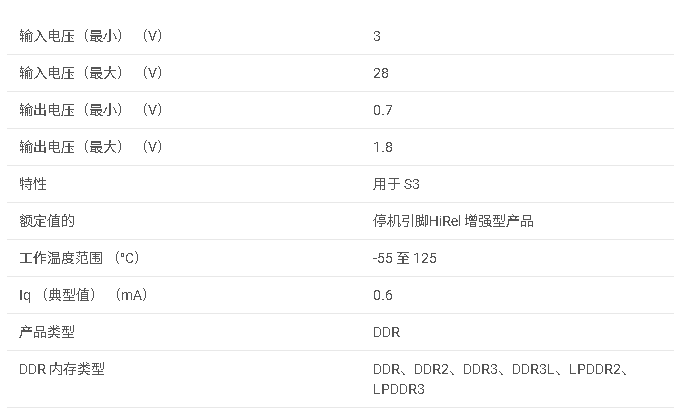

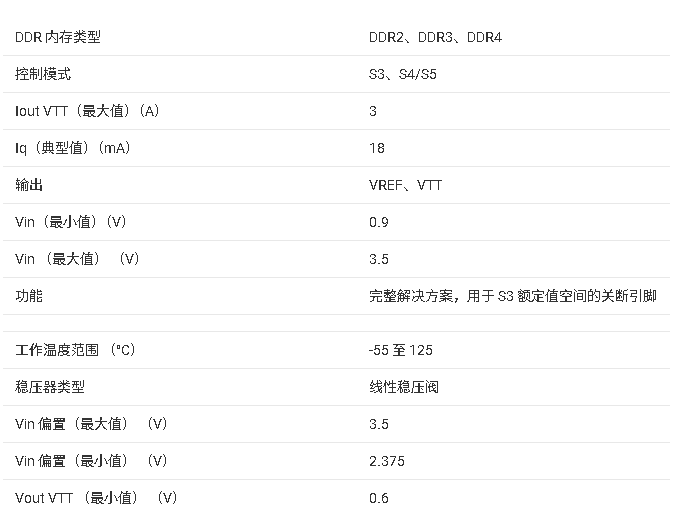

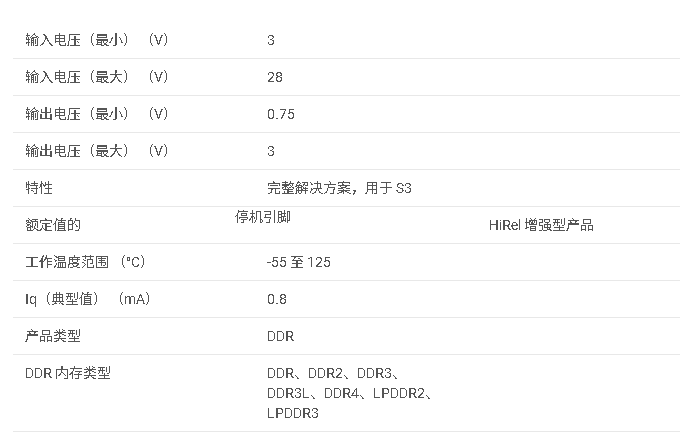

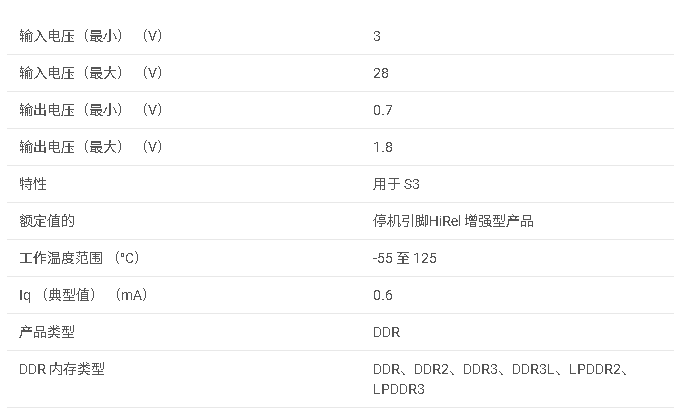

TPS7H3301-SP 支持使用 DDR、DDR2、DDR3、DDR4 的 DDR VTT 端接应用。TPS7H3301-SP VTT 稳压器的快速瞬态响应允许在读/写条件下提供非常稳定的电源。在

2025-09-09 14:45:15 719

719

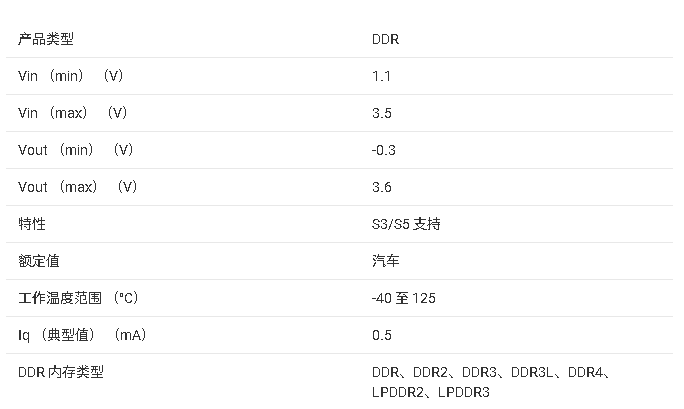

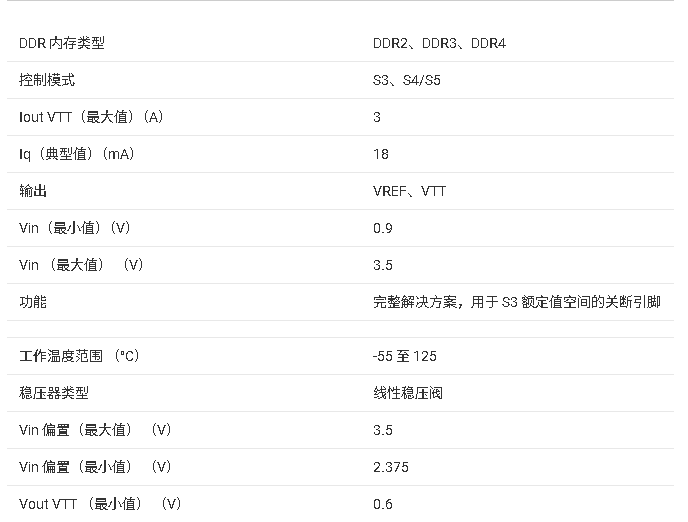

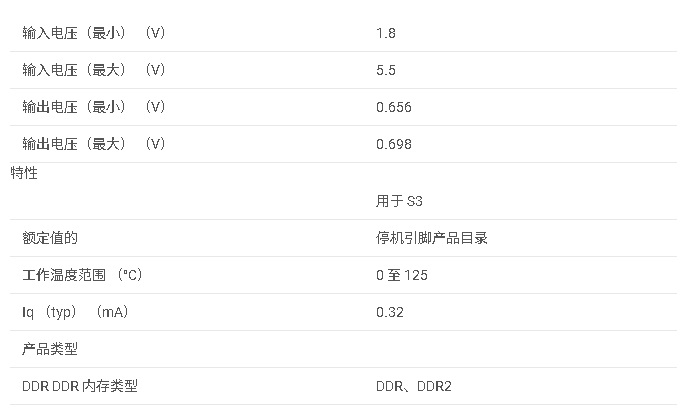

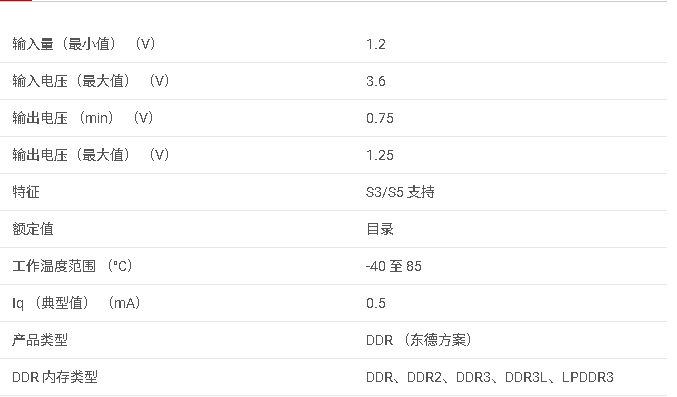

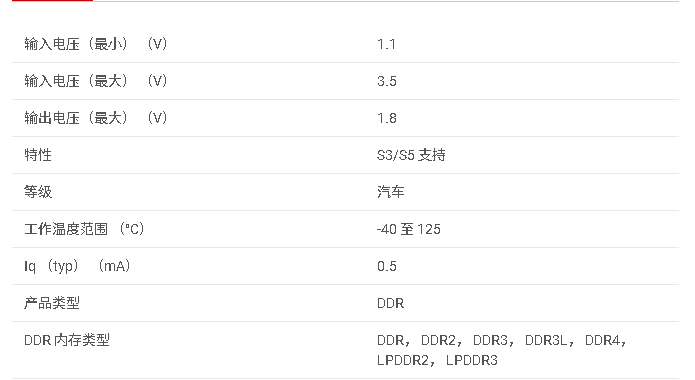

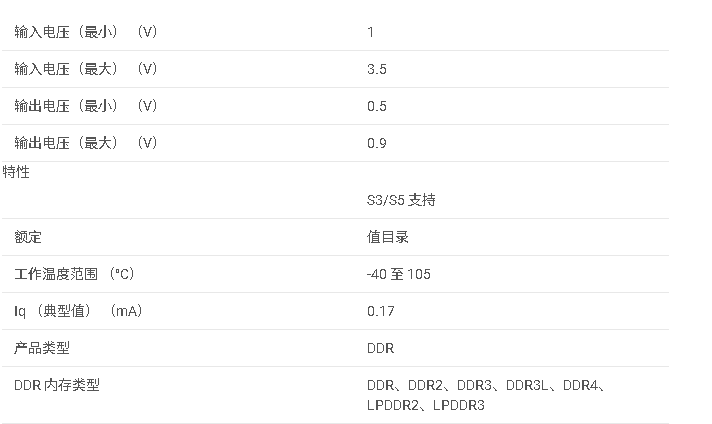

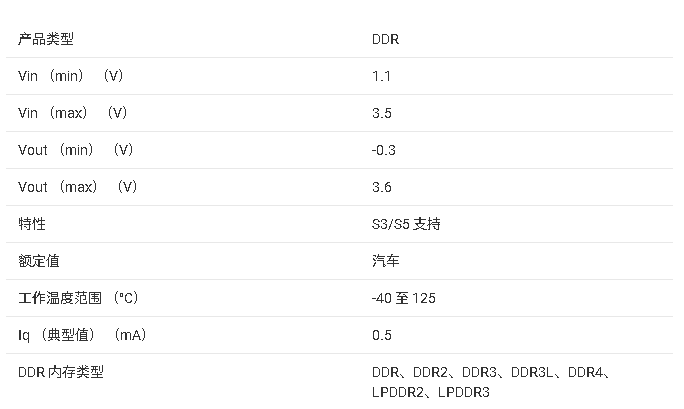

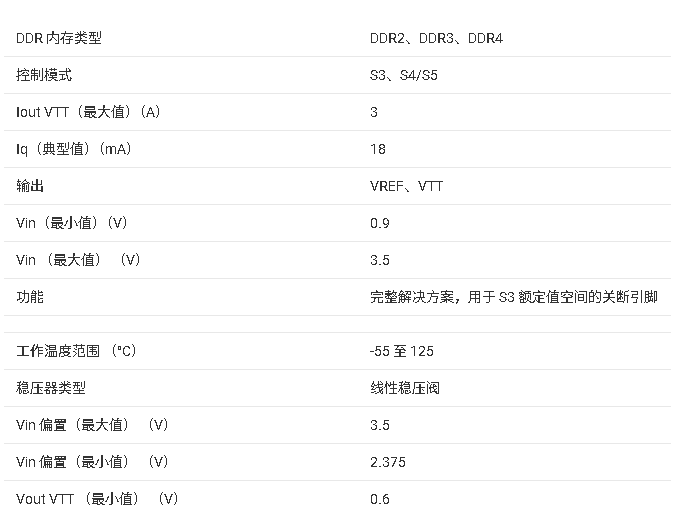

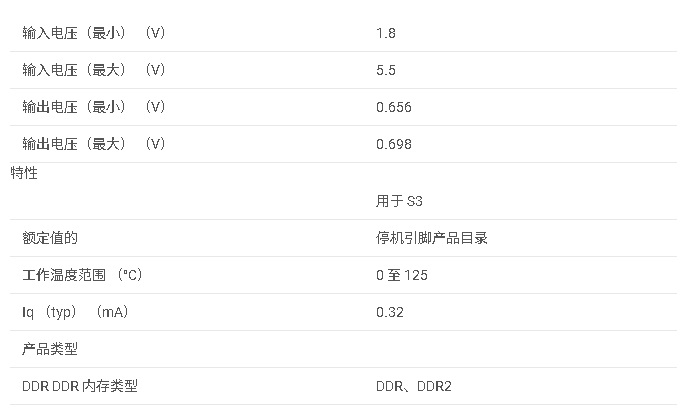

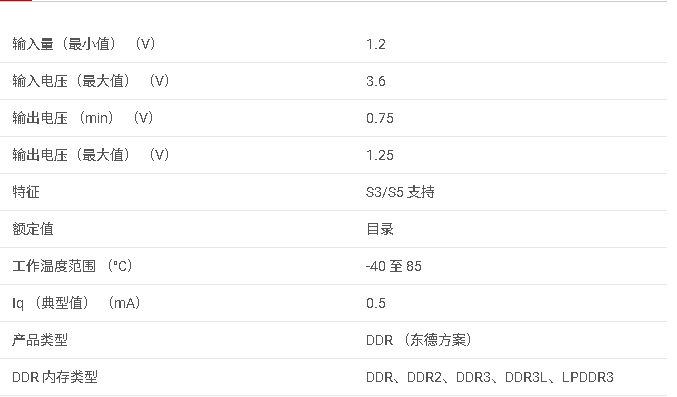

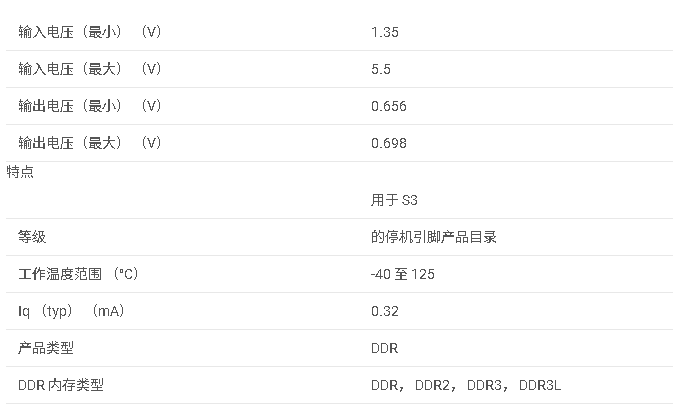

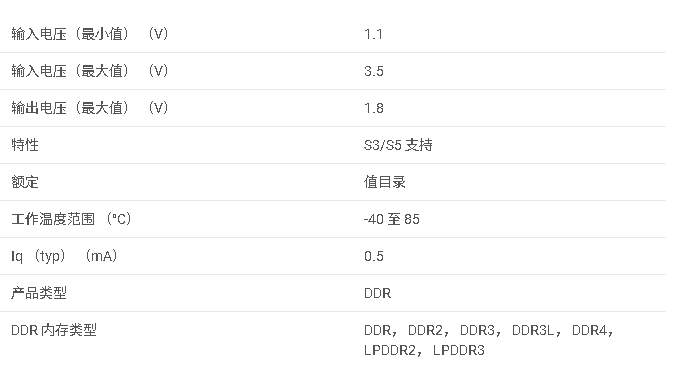

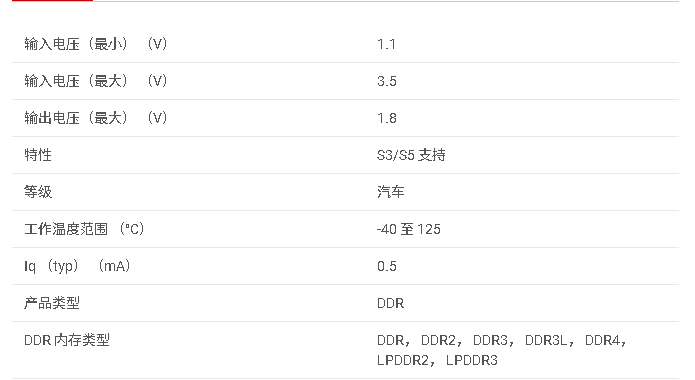

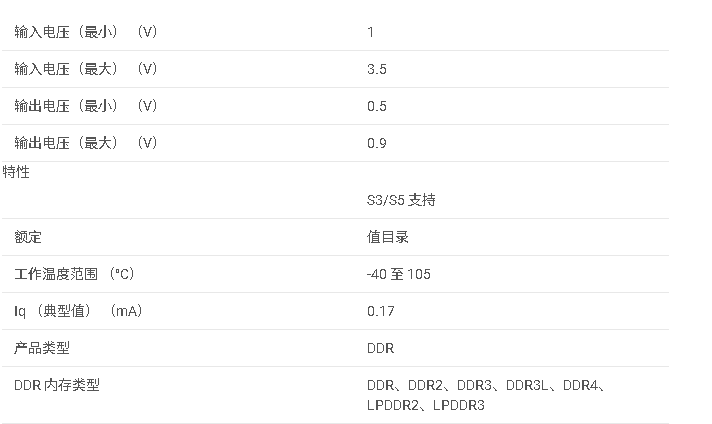

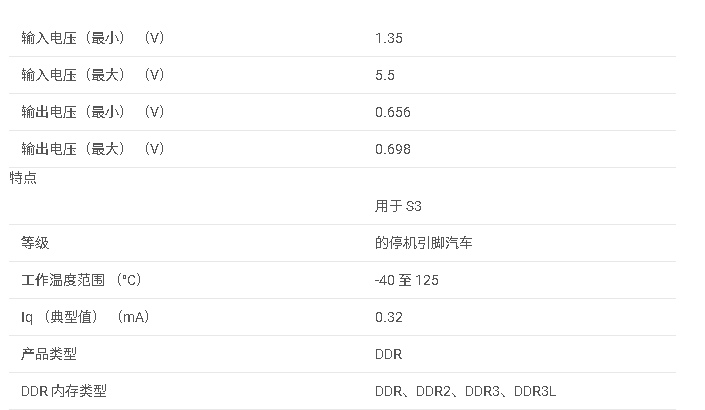

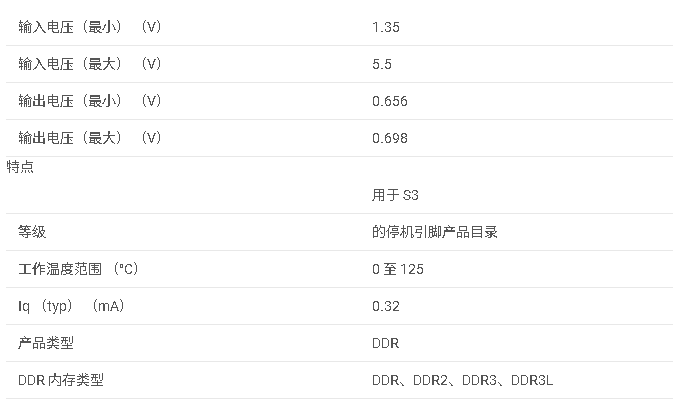

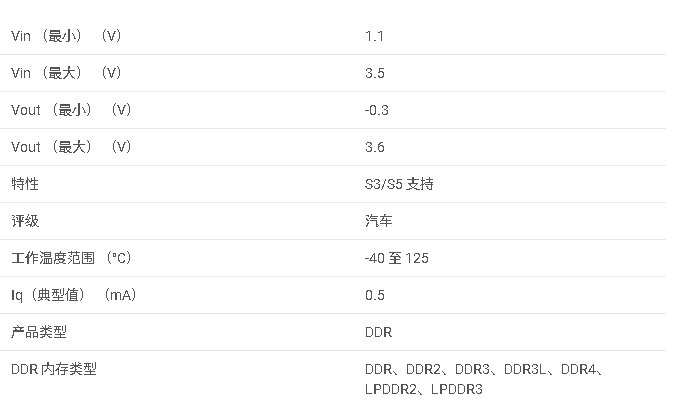

TPS51200A-Q1 器件是一款灌电流和源极双数据速率 (DDR) 终端稳压器,专为低输入电压、低成本、低噪声系统而设计,其中空间是关键考虑因素。

该器件保持快速瞬态响应,最小输出电容仅为

2025-09-09 14:28:07 713

713

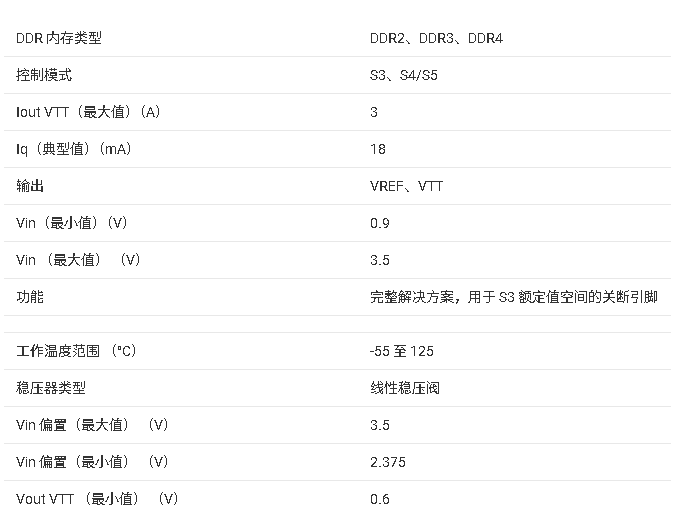

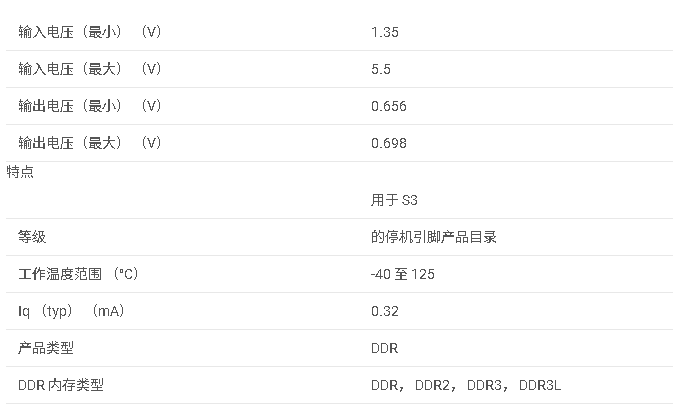

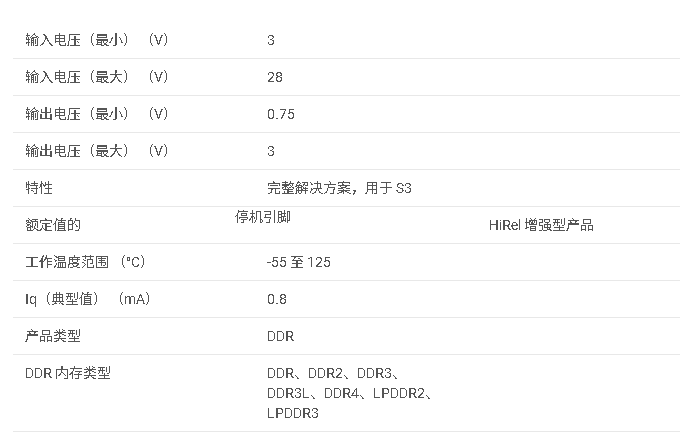

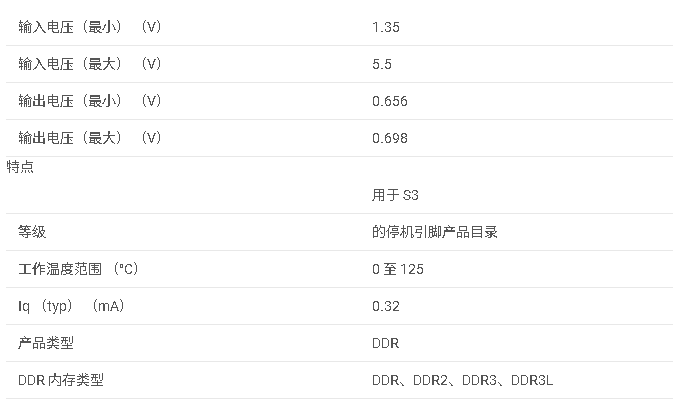

该TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接应用。TPS7H3302 VTT 稳压器的快速瞬态响应允许在读/写条件下提供非常稳定的电源

2025-09-09 13:53:22 688

688

该TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接应用。TPS7H3302 VTT 稳压器的快速瞬态响应允许在读/写条件下提供非常稳定的电源

2025-09-09 13:48:37 756

756

或者会数据出错,而L14层的走线眼图就好很多,再优化一下就会有一定的裕量,看起来过孔stub长居然对DDR4的信号质量有一定的改善作用。

这个原理其实在上篇文章中讲到过,我们再来重温一下:过孔stub

2025-09-04 10:50:26

如何利用 DDR 参数文件生成 Linux 映像

2025-09-02 06:39:54

EasyGo DeskSim是一款配置型的实时仿真软件,它允许用户将 Simulink 算法程序快速部署到 EasyGo 实时仿真机上。实时仿真机支持选配不同的 FPGA 芯片和 IO 模块,能够处理高速信号,并通过 IO 模块输出真实的仿真结果,可满足用户在科研、教学或工业测试中的多样化需求。

2025-08-30 09:53:09 801

801

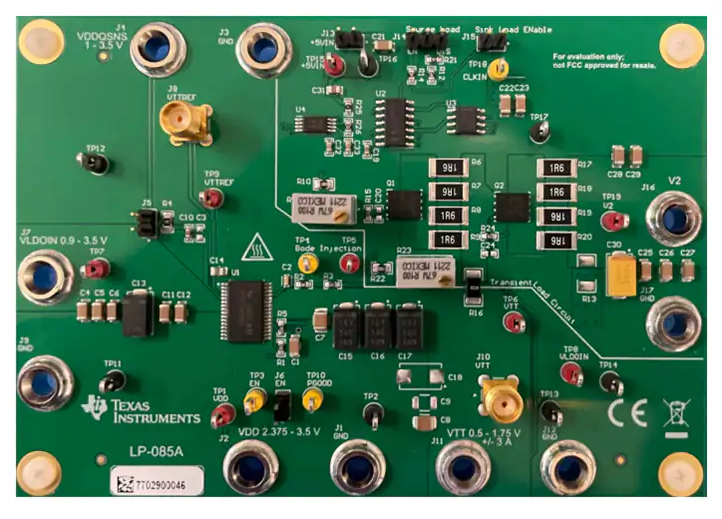

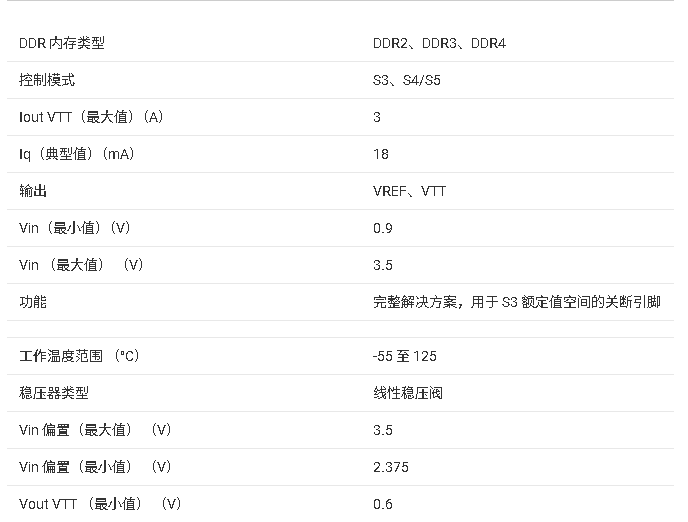

3A,支持测试DDR、DDR2、 DDR3、DDR3L和DDR4。该评估模块配有方便的测试点和跳线,用于评估TPS7H3302-SEP DDR端子。TPS7H3302EVM评估模块非常适合用于抗辐射DDR电源应用以及用于DDR、DDR2、DDR3和DDR4的存储器终端稳压器。

2025-08-27 16:14:21 831

831

凭借与紫光国芯的紧密合作,贞光科技能够为客户提供DDR3、LPDDR4及LPDDR4X全系列车规级存储产品。在产品覆盖、技术支持和供应保障等方面的综合优势,使贞光科技成为车载电子领域可靠且高效

2025-08-26 16:12:15 1426

1426

ATE测试,即自动化测试设备,是一种高度集成化、自动化的电子测试技术。它通过计算机控制,结合多种测试模块,对电子元器件、消费电子、电路板等进行功能和性能测试。ATE测试系统能够自动施加测试信号,采集响应数据,并与预设标准进行比对,快速判断被测对象是否符合质量要求。

2025-08-19 11:33:44 1646

1646 EasyGo DeskSim是一款配置型的实时仿真软件,它允许用户将 Simulink 算法程序快速部署到 EasyGo 实时仿真机上。实时仿真机支持选配不同的 FPGA 芯片和 IO 模块,能够处理高速信号,并通过 IO 模块输出真实的仿真结果,可满足用户在科研、教学或工业测试中的多样化需求。

2025-08-18 11:32:51 4723

4723

本测试方案旨在利用振动分析技术,结合高精度数采设备,实现对数控机床刀具质量的快速评估。该方法通过监测刀具在敲击激励下的振动响应,利用振动信号的特征参数来评估刀具的阻尼效果,进而判断其质量优劣。

2025-08-07 10:24:36 1249

1249

≤100ps)。

若眼图闭合,说明信号质量差,需优化物理层(如更换电缆、调整终端电阻)。

3. 协议级过滤与统计

工具:Teledyne LeCroy USB Protocol Suite的“Error

2025-08-01 15:00:38

眼图是一个统计叠加的概念,是一系列数字信号在示波器上积累而显示的图形,通过它可以观察出码间串扰和噪声对系统的影响,从而估计系统优劣。一个完整的眼图应该包含从“000”到“111”的所有状态组,且

2025-07-30 17:33:32 4935

4935

本文紧接着前一个文档《AD设计DDR3时等长设计技巧-数据线等长 》。本文着重讲解DDR地址线、控制信号线等长设计,因为地址线、控制信号线有分支,SOC有可能带有2片DDR或者更多,我们叫做T型分支

2025-07-29 16:14:51 2

2 (如NAK占比>1%表明链路不稳定)。

结合眼图测试功能,分析信号质量(如眼高、眼宽),定位物理层问题(如线缆老化、连接器氧化)。

设备兼容性验证

场景:新部署的GPU或NVMe

2025-07-29 15:02:27

完整性保障

眼图分析:通过眼图评估信号质量,确保眼高、眼宽满足协议要求。例如,PCIe 5.0要求时钟抖动<50ps,若眼图闭合或抖动超标,需检查硬件连接(如探头、线缆)或调整信号阈值

2025-07-28 17:28:18

的讲解数据线等长设计。 在另一个文件《AD设计DDR3时等长设计技巧-地址线T型等长》中着重讲解使用AD设计DDR地址线走线T型走线等长处理的方法和技巧。

2025-07-28 16:33:12 4

4 随着数据量的不断增加,对信号带宽的需求也在不断增长。同时,在长距离传输中,数字信号可能会因为传输介质的特性而衰减。现有的数字电路/链路等已经无法满足日益增长的带宽和质量需求,导致传输速度变慢及信号质量变差,影响数据的正确、快速传输。

2025-07-25 15:40:51 4398

4398

提供的标准语音样本文件进行测试,也支持上传真实的业务音频文件,以更贴近实际应用场景。默认音频文件便于快速开展基准测试,而真实音频文件则有助于验证在具体语音内容和编码格式下的传输质量。 3. 关键网络

2025-07-22 11:15:03

本原创文章由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处(www.meyesemi.com)

1.实验简介

实验目的:

完成 DDR3 的读写测试。

实验环境

2025-07-10 10:46:48

出整个数据流的路径。这是一个典型的FPGA图像处理系统架构:

输入端 (Camera Input) -> ISP (图像信号处理) -> DDR3 缓存 (Frame

2025-07-06 15:18:53

EasyGo DeskSim是一款配置型的实时仿真软件,它允许用户将 Simulink 算法程序快速部署到 EasyGo 实时仿真机上。实时仿真机支持选配不同的 FPGA 芯片和 IO 模块,能够处理高速信号,并通过 IO 模块输出真实的仿真结果,可满足用户在科研、教学或工业测试中的多样化需求。

2025-06-30 14:11:05 884

884

DDR内存占据主导地位。全球DDR内存市场正经历一场前所未有的价格风暴。由于原厂加速退出DDR3/DDR4市场,转向DDR5和HBM(高带宽内存)生产,DDR3和DDR4市场呈现供不应求、供需失衡、涨势延续的局面。未来,DDR5渗透率将呈现快速提升,市场份额增长的趋势。

2025-06-25 11:21:15 2010

2010

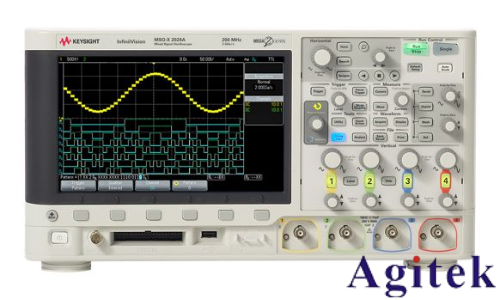

,为工程师提供了实时眼图与频谱分析的一体化解决方案。本文将深入探讨DSOX2004A如何通过其关键技术实现精准的眼图和频谱测量,助力用户高效解析复杂信号。 一、DSOX2004A示波器的核心功能概述 DSOX2004A是一款高性能混合信号示波器,具备以下关键特性:

2025-06-24 12:06:50 528

528

络中,数据通过双绞线上的差分信号传输。信号质量直接影响节点正确解读数据的能力。信号质量差可能表现为:

位错误 :由于噪声或信号失真导致的位误判。 帧错误 :CAN帧结构错误,导致接收节点拒绝。 总线

2025-06-07 08:46:40

网络配线架打线操作的质量检查是确保网络布线系统稳定性和可靠性的关键环节。以下从外观检查、电气性能测试、功能验证、标识与文档检查四个维度,系统阐述质量检查的核心措施及具体方法: 一、外观检查 1.

2025-06-06 10:30:16 786

786

随着汽车产业向智能化、网联化加速转型,高级驾驶辅助系统(ADAS)和智能驾驶技术已成为现代汽车不可或缺的核心组件。紫光国芯作为国内领先的存储器芯片制造商,其车规级DDR3存储产品在智能驾驶和ADAS

2025-06-05 16:50:17 1225

1225

对于高质量图形显示的应用要求,用户通常采用功能强大及搭载DDR高速接口的MPU来实现更多功能和更流畅的画面。但在开发过程会遇到DDR高速总线设计的难题,同时Linux系统难以实现类似MCU的快速启动性能。瑞萨新推出的RZ/A3M HMI MPU帮助客户解决这些问题。

2025-05-27 16:14:30 894

894

,如包起始或同步域。

信号质量参数:

眼图分析:测量眼高、眼宽、抖动等参数,评估信号质量。

抖动测试:包括随机抖动(RJ)和确定性抖动(DJ),确保符合USB规范。

上升/下降时间:测量信号边沿速率

2025-05-16 15:55:16

革命性的眼图分析功能,为工程师提供了一整套从信号捕获到故障定位的完整解决方案。本文将深入解析MSO54B眼图分析的核心技术、应用场景及操作要点,揭示其如何成为高速信号测试领域的标杆产品。 一、技术架构:构建眼图分析的硬件基石 1. 超高分

2025-05-13 15:57:13 547

547

下面是调用的DDR3模块的,模块的倒数第二行是,模块的时钟输入,时钟源来自PLL产生的系统时钟的倍频。

2025-05-03 10:21:00 1339

1339

在现代高速数字通信系统中,眼图分析是评估信号完整性的核心工具。泰克MDO32系列示波器凭借其强大的混合域分析能力,为工程师提供了经济高效的眼图测试方案。本文将结合理论与实际操作,系统讲解

2025-04-30 15:14:44 874

874

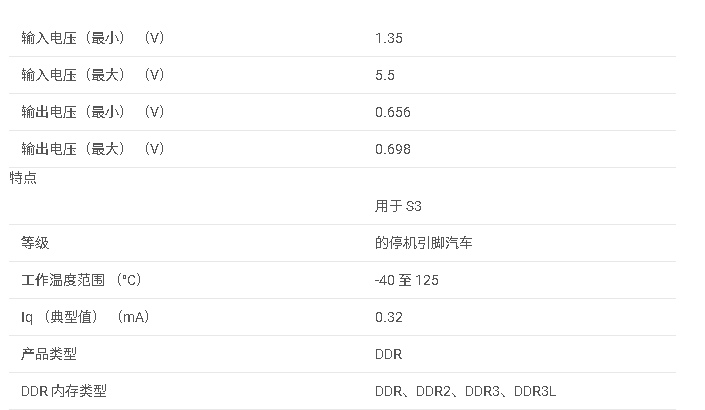

LP2996-N 和 LP2996A 线性稳压器旨在满足 JEDEC SSTL-2 标准 DDR-SDRAM 终止规范。该器件还支持 DDR2,而 LP2996A 支持 DDR3 和 DDR3

2025-04-29 18:11:05 834

834

终端供电。这 该器件还支持 DDR3 VTT 端接,VDDQ 电压为 1.5 V(典型值)。此外,TPS51100 包括集成的睡眠状态控制、在 S3 中将 VTT 置于 Hi-Z(暂停到 RAM)和软

2025-04-29 17:15:20 774

774

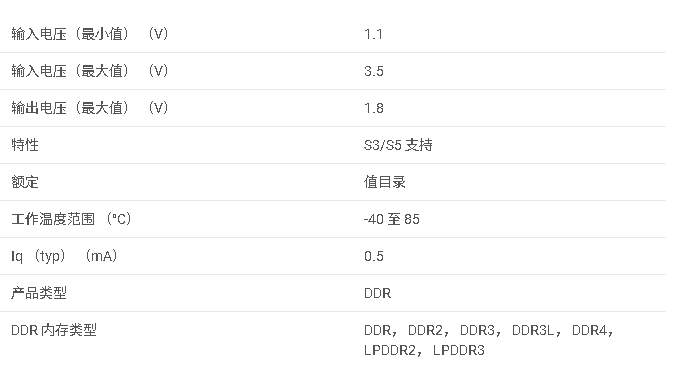

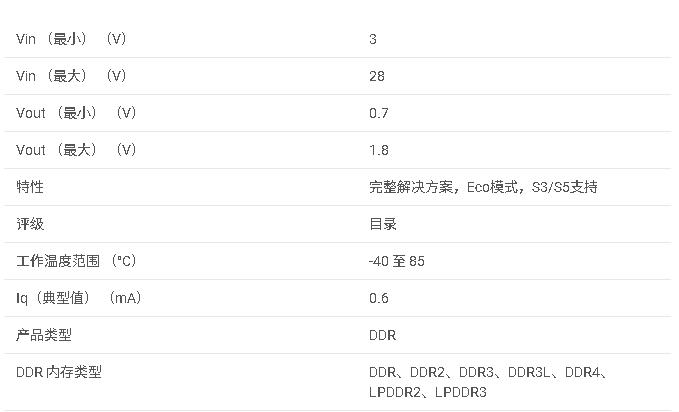

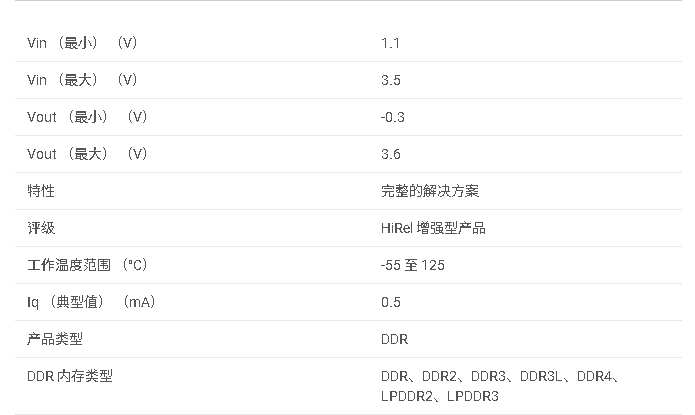

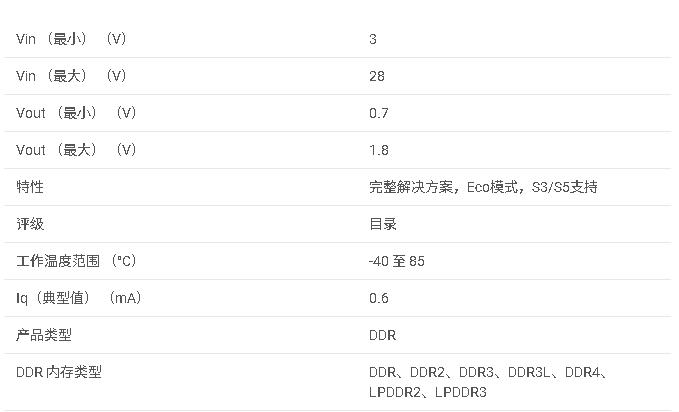

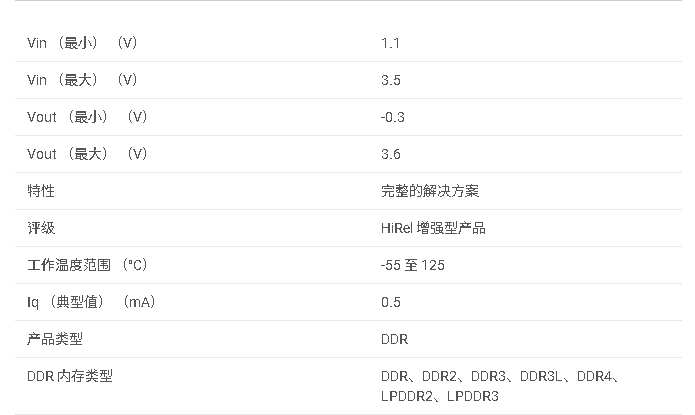

TPS51116为 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、DDR3L、LPDDR3 和 DDR4 内存系统提供完整的电源。它将同步降压控制器与 3A 灌电流/拉

2025-04-29 16:38:02 1031

1031

在高速PCB设计中,DDR模块是绝对绕不过去的一关。无论你用的是DDR、DDR2还是DDR3,只要设计不规范,后果就是——信号反射、时序混乱、系统频繁死机。

2025-04-29 13:51:03 2491

2491

LP2998 线性稳压器旨在满足 JEDEC SSTL-2 和 JEDEC SSTL-18 标准 DDR-SDRAM 和 DDR2 内存终止的规范。该器件还支持 DDR3 和 DDR3L VTT

2025-04-29 11:34:59 810

810

TPS51200 器件是一款灌电流和拉电流双倍数据速率 (DDR) 终端稳压器,专为空间受限的低输入电压、低成本、低噪声系统而设计。

该TPS51200保持快速瞬态响应,并且需要的最小输出电容

2025-04-29 09:59:25 1345

1345

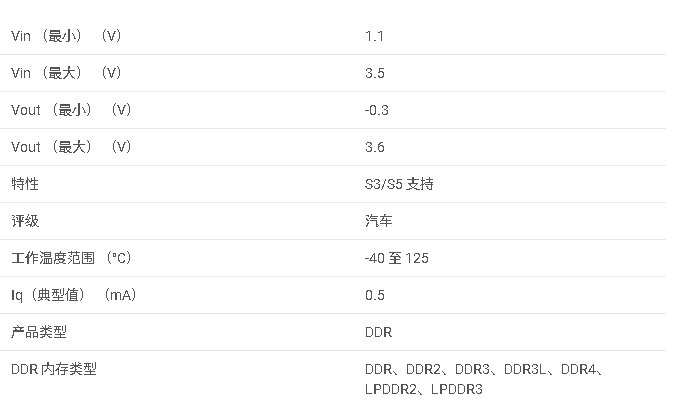

TPS51200-Q1 器件是一款灌电流和拉电流双倍数据速率 (DDR) 终端稳压器,专为空间受限的低输入电压、低成本、低噪声系统而设计。

TPS51200-Q1 器件保持快速瞬态响应,并且

2025-04-28 16:21:07 852

852

TPS59116 为 DDR/SSTL-2、DDR2/SSTL-18 和 DDR3 内存提供完整的电源 系统。它将同步降压控制器与 3A 灌电流/拉电流跟踪线性稳压器和缓冲低噪声基准集成在一起

2025-04-28 13:54:45 814

814

TPS51216 以最低的总成本和最小的空间为 DDR2、DDR3 和 DDR3L 内存系统提供完整的电源。它将同步降压稳压控制器 (VDDQ) 与 2A 灌/拉跟踪 LDO (VTT) 和缓

2025-04-28 11:09:05 663

663

TPS51916 器件以最低的总成本和最小的空间为 DDR2、DDR3、DDR3L 和 DDR4 内存系统提供完整的电源。它集成了同步降压稳压控制器 (VDDQ),具有 2A 灌电流和 2A 源跟踪 LDO (VTT) 和缓冲低噪声基准 (VTTREF)。

2025-04-28 10:58:44 657

657

快速瞬态响应,并且只需要 1 × 10μF 的陶瓷输出电容。该器件支持远程感应功能以及 DDR2、DDR3 和低功耗 DDR3 (DDR3L) 以及 DDR4 VTT 总线的所有电源要求。VTT 电流

2025-04-28 10:04:48 685

685

TPS51116为 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、 和 LPDDR3 内存系统。它将同步降压控制器与 1A 灌电流/拉电流集成在一起 跟踪线性稳压器和缓

2025-04-27 13:35:32 741

741

TPS51716为 DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 提供完整的电源 以最低的总成本和最小空间实现内存系统。它集成了一个同步降压 具有 2A 灌电流/拉电流跟踪 LDO

2025-04-27 11:36:05 763

763

LP2998 线性稳压器旨在满足 JEDEC SSTL-2 和 JEDEC SSTL-18 标准 DDR-SDRAM 和 DDR2 内存终止的规范。该器件还支持 DDR3 和 DDR3L VTT

2025-04-27 09:40:04 874

874

LP2996A 线性稳压器旨在满足 JEDEC SSTL-2 规范 DDR-SDRAM 终止。该器件还支持 DDR2、DDR3 和 DDR3L VTT 总线端接,带 V~DDQ~最小为 1.35V

2025-04-26 15:02:50 746

746

TPS51216-EP 以最低的总成本和最小的空间为 DDR2、DDR3 和 DDR3L 内存系统提供完整的电源。它将同步降压稳压控制器 (VDDQ) 与 2A 灌/拉跟踪 LDO (VTT) 和缓

2025-04-26 11:12:30 681

681

TPS51200-EP 器件是一款灌电流和拉电流双倍数据速率 (DDR) 终端稳压器 专为空间受限的低输入电压、低成本、低噪声系统而设计 考虑。

TPS51200-EP 保持快速瞬态响应,并且

2025-04-26 10:26:35 1335

1335

TPS51200A-Q1 器件是一款灌电流和拉电流双倍数据速率 (DDR) 终端稳压器,专为空间受限的低输入电压、低成本、低噪声系统而设计。

该器件保持快速瞬态响应,并且只需要 20 μF

2025-04-25 10:07:15 1053

1053

在全球科技竞争加剧、国产替代加速推进的背景下,紫光国芯凭借其在DDR3与RDIMM等高端内存芯片领域的技术积累,不断实现突破,推动国产存储芯片向高端市场迈进。作为其核心代理商,贞光科技在市场推广

2025-04-16 16:39:30 1342

1342

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代产品,相较于DDR2,DDR3有更高的运行性能与更低的电压。

2025-04-10 09:42:53 3930

3930

灿芯半导体(上海)股份有限公司(灿芯股份,688691)宣布推出基于28HKD 0.9V/2.5V 平台的DDR3/4, LPDDR3/4 Combo IP。该IP具备广泛的协议兼容性,支持DDR3

2025-03-21 16:20:03 984

984 初次使用XC7A35T-FGG484做设计,用的是25MHZ有源晶振,有源晶振3.3V供电,DDR3的供电1.35V,现在接上晶振后,DDR3的供电变成1.8V

求助怎么解决。

2025-03-21 14:25:05

0xDEADBEEF。

我们尝试并验证了一些事情:

硬件:

- 原理图审查并仔细检查

- 检查电压。GVDD、VREF、VTT 和 VPP

- 输入和输出 DDR 时钟

- DRAM 重置信号正确

- MEM

2025-03-21 07:15:45

在进行DDR(双倍数据速率)信号测试时,普源DHO1072示波器是一款功能强大的工具,能够帮助用户准确分析和调试信号。以下是使用普源DHO1072示波器进行DDR信号测试的几个关键要点。 一

2025-03-14 12:06:00 942

942

请问怎么使用STM32F723的开发板测试HS的眼图,开发板程序包含USBD_HS_TESTMODE_ENABLE后按教程修改了USBD_LL_TestMode函数,结果文件显示USBx_DEVICE定义的USBx_BASE没有定义,应该怎么改呀

2025-03-13 07:32:58

DDR内存控制器是一个高度集成的组件,支持多种DDR内存类型(DDR2、DDR3、DDR3L、LPDDR2),并通过精心设计的架构来优化内存访问效率。

2025-03-05 13:47:40 3573

3573

据报道,业内人士透露,全球三大DRAM内存制造商——三星电子、SK海力士和美光,有望在2025年内正式停产已有多年历史的DDR3和DDR4两代内存。 随着技术的不断进步和消费级平台的更新换代

2025-02-19 11:11:51 3465

3465 ;MTA9ASF1G72AZ-3G2R1是一款高性能的DDR3 SDRAM内存模块,专为满足现代计算需求而设计。该产品以其高带宽和低功耗的特性,广泛应用于个人电脑、服务器和嵌入式系统中,成为市场上备

2025-02-10 20:10:39

最近一项目中利用ADS1274采集20mv的微量信号,采集出来数据不正确。

具体情况为:

输入前端模拟信号幅度采集出来数据换算后

5.10mv,4.338mv;

5.11mv 4.348mv

2025-02-06 06:29:51

示波器作为电子测试测量领域的重要工具,其功能多样且强大。其中,眼图分析功能是示波器在数字信号完整性测试中的一项关键应用。眼图不仅直观展示了数字信号的整体特征,还能够反映出码间串扰、噪声、抖动等关键

2025-02-02 14:04:00 2311

2311 的重要性 通信质量评估 :信道信号强度是评估通信质量的重要参数,它可以帮助我们了解信号在传输过程中的损耗情况。 网络优化 :通过测试信道信号强度,可以发现网络覆盖的盲区,为网络优化提供数据支持。 设备性能测试 :信道信

2025-01-22 16:25:35 3622

3622 在现代通信系统中,调制技术是实现信息传输的关键环节。调制过程涉及将原始信息信号(基带信号)转换成适合在特定信道上传输的形式。这一过程对信号的传输质量有着深远的影响,包括信号的可靠性、传输效率、抗干扰

2025-01-21 09:25:53 1743

1743 一个10Nf~100nF的电容,整个VTT电路上需要有uF级大电容进行储能。

一般情况下,DDR的数据线都是一驱一的拓扑结构,且DDR2和DDR3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可

2025-01-21 06:02:11

复杂的实时嵌入式系统应用,支持多种内存接口和丰富的外设端口,满足多样化场景需求。

通过硬核NPU,JPU,MIPI 来支持边缘智能应用,为FPGA市场注入新的活力。SOM模组标配1GB DDR3

2025-01-10 14:32:38

很多方法都可以表征高速数字通道,目标是验证说明通道合规性的特定信号完整性指标。S参数和阻抗等指标都很有用,但还有一项重要测量需要使用数字比特流进行评估:眼图。 作为通道合规性的一部分,眼图是一种有用

2025-01-08 11:27:02 2632

2632

,保证良好的电气连接。

4、焊接质量审核

检查已焊接元器件的接点,确保焊接牢固,无虚焊或漏焊现象。

5、性能测试

验证元器件的功能指标,确保其性能满足产品设计的需求。

6、材料认证

确保使用正确的材料

2025-01-07 16:16:16

电子发烧友App

电子发烧友App

评论