来源:漫谈大千世界

信号完整性(Signal Integrity, SI)问题:随着DDR内存频率的提高,信号完整性问题变得更加突出。高速信号在传输过程中会受到各种因素的影响,如反射、串扰、噪声干扰等,这些问题会导致信号失真,影响数据的正确传输。DDR training通过自适应的机制来补偿这些信号完整性问题,确保数据链路的可靠性。

时钟和数据信号的对齐:在高速数据传输中,时钟信号和数据信号需要精确对齐以保证数据的正确读取和写入。由于物理布局、走线长度差异等因素,时钟和数据信号可能会有微小的偏差,DDR training通过调整时序来对齐这些信号,以确保数据传输的准确性。

适应不同的物理层设计:不同的主板设计、内存条设计以及物理层的实现可能会引入不同的信号传输特性。DDR training能够适应这些差异,通过调整参数来优化内存系统的性能。

提高数据传输效率:DDR内存通过双倍数据速率的传输方式,结合多通道传输和数据校验等技术,提高了数据传输效率和可靠性。DDR training是实现这些技术的关键步骤之一。

综上所述,从主机的角度来看,与 DIMM 上不同的颗粒的距离是不同的。而从 DIMM 的角度来看,时钟(黑色)与数据(绿色)之间的相对延迟对于不同颗粒是不同的。训练的目的即消除这两个不同对数据读写的影响,确保高速内存系统在各种条件下都能稳定、可靠运行的重要技术手段。

1. DDR training sequence

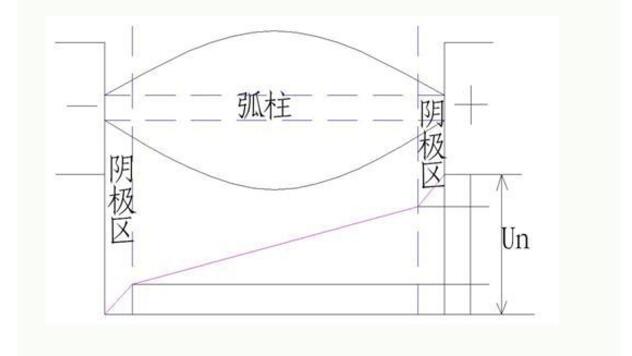

为了保证稳定且可靠的内存访问,写入和读取的眼图(eye diagram)的宽度是一个关键因素。眼图的位置取决于两个主要参数:LCDL(Load Command Delay Line,负载命令延迟线)的值以及VREF(参考电压)的设置。

写入和读取数据眼图训练用于通过改变LCDL的值(结合初始计算和编程的VREF设置)来找出最佳的眼图位置。

VREF训练用于确定一个VREF值的范围,在该范围内内存接口(写入和读取)是稳定的,并进一步确定最佳的写入和读取眼图位置。

1. CS Training: 目的是对齐CS_N和CK;在发送cmd后进入CS Training Mode,通过Delay CS_N timing以达到和CK对齐

2. CA Training: 目的是对齐CA和CK,在发送cmd后进入CA Training Mode,通过Delay CA timing以达到和CK对齐

3. ZQ Calibration:每个DRAM都包含一个称为DQ校准控制块的特殊模块和一个ZQ引脚,该引脚连接有一个外部精密(±1%)240Ω电阻。这个外部精密电阻是“参考”电阻,它在所有温度下都保持在240Ω。在初始化期间发出ZQCL命令时,DQ校准控制块被激活,并产生一个调谐值。然后,该值被复制到每个DQ的内部电路中。

4. DLL(Delay Lock Loop): 目的是在Read时,对齐DQS和CK.

DDR SDRAM对时钟的精确性要求很高,因为它有两个时钟:外部的总线时钟和内部的工作时钟。理论上,这两个时钟应该是同步的,但由于温度、电压波动等原因,它们很难保持同步。DLL的任务就是根据外部时钟动态修正内部时钟的延迟,以实现两者的同步. DLL功能在DDR SDRAM中可以被禁止,但仅限于除错与评估操作,正常工作状态是自动有效的

5. MPR mode: 启用此模式后,发送到DRAM的读取和写入操作会被转移到多用途寄存器,而不是内存bank,可以避免cell问题导致读取数据错误,确保后续的读写可以正常进行

6. Read preamble Training: Controller方用于对齐DQS 和CK

7. Read Training: Controller方用于找到最佳的DQS sample DQ 的窗口。Read Training 的目的是训练控制器的读采样电路,确保在读取数据时,采样操作发生在数据眼图的中心位置,以获得最稳定的采样结果。

8. Write Leveling: 对齐Write时的DQS和CK

9. VrefDQ training: VrefDQ校准的目的是为了确保控制器能够正确地识别和解释从DRAM接收到的信号。在VrefDQ校准阶段,内存控制器需要通过尝试不同的VrefDQ值来设置一个能够正确区分高低电平的值。这个校准过程对于读写操作都是至关重要的,因为它直接影响到数据的完整性和准确性。

DRAM VREF训练:此训练通过扫描内存内部的DRAM VrefDQ值来优化写入眼图。

Host VREF训练:此训练通过扫描PHY I/O的VREF设置来优化读取眼图

上述的Training中,仅仅ZQ和DLL是control发生CMD后,DDR自己完成的;其它的都是在control发起后,control完成。

2. CS Training Mode (CSTM)

CS训练模式是一种促进CS_n信号采样序列环回的方法。在这种模式下,CK(时钟信号)在运行,而CA(命令/地址)信号保持在NOP(无操作)命令编码状态。一旦启用了这个模式并且选择了DRAM设备来主动采样和驱动反馈,DRAM将在CK的上升沿时对CS_n信号进行采样。每组四个CK上升沿的采样将被包含在逻辑计算中,以确定发送回主机的CSTM输出结果,通过DQ总线发送回主机。一旦开始采样,DRAM必须保持每4个tCK的连续采样组。当CS_n Sample[0]和Sample[2]的结果为逻辑0,而CS_n Sample[1]和Sample[3]的结果为逻辑1时,DRAM将在所有的DQ信号上驱动0。没有要求驱动任何时序信号,输出信号可以每4个tCK转换一次。

3. CA Training Mode (CSTM)

目的:CA training旨在确保CA信号与CK信号正确对齐,以实现正确的时序。

机制:在CA training模式下,CK正常运行,CS_n在CK采样CA信号时进行限定。通过回传方程,CA信号的逻辑组合被回传到主机存储控制器,以异步方式通过DQ信号发送。这样,主机可以优化CS_n、CK和CA[13:0]信号之间的时序,实现正确的对齐

4. Write Leveling

Write Leveling(写均衡)是DDR内存技术中用于确保数据在正确的时钟周期内被写入内存的一种训练过程。以下是Write Leveling的一些关键点:

目的:Write Leveling的目的是调整DQS(数据请求信号)与CK(时钟信号)之间的时序关系,以确保数据在内存中可靠地写入。由于布线差异等因素,DRAM使用的strobe信号通常不会与它接收的输入时钟对齐,因此需要通过Write Leveling来调整这种相位差。

实现原理:Memory Controller(MC)通过调节发出DQS-DQS#的时间,来让各个内存颗粒的DQS-DQS#和CK-CK#对齐,起到补偿skew的作用。MC不断地调整DQS-DQS#信号相对于CK-CK#的延迟,颗粒端在每个DQS-DQS#上升沿采样CK-CK#信号。如果采样值为低,则将所有DQ[n]保持为低来告知MC,tDQSS相位关系还未满足;如果在某个DQS-DQS#上升沿采样到CK-CK#电平发生跳变,则认为此时tDQSS已满足,将所有DQ[n]保持为高(异步反馈)来告知MC,tDQSS相位关系已满足,表征写均衡成功。

操作过程:在Write Leveling过程中,控制器不断将选通信号发送到特定的DRAM。当DRAM接收到选通信号时,它将对时钟信号进行采样,并将其在数据总线上的值返回给控制器。控制器将为DQS信号引入越来越多的延迟,直到观察到数据总线上从零到一的转变为止。此时,控制器将锁定此校准延迟设置,并将其用于以后的写操作。

Write Leveling会针对每个DRAM芯片进行CK与DQS信号间的相位调整,采用一种多次试错,寻找最优值的方法使DRAM接收到的时钟信号与写数据同步。

名词释义:

(1) DQSS:DQS-DQS# rising edge to CK-CK# rising edge,spec要求为+/-0.25 tCK,tCK为CK时钟周期

(2) tDQSH:DQS高电平脉宽

(3) tDQSL:DQS低电平脉宽

(4) tWLMRD:在 MC 配置 DRAM MR,使之进入 write leveling 模式后,经过 tWLMRD 后,MC 开始发出第一个用于 write leveling 的 DQS 脉冲。

(5) tWLO:DRAM 在 DQS 采样 CK 值后,通过 DQ 返回采样值,这里需要注意的是,返回采样值是一个异步的操作。DRAM 会在采样后的 tWLO 时刻返回采样值。

(6) tWLOE:协议规定,DQ 的所有比特都会返回一个相同的值,但这些比特的跳变时间之间有一个偏差,这个偏差的最大值是 tWLOE。

Write Leveling是确保高速内存接口中数据正确写入的关键步骤,它通过动态调整DQS和CK之间的时序来补偿可能的偏差,从而提高内存性能和稳定性。

5. Read Training

Read Training 的目的是训练控制器的读采样电路,确保在读取数据时,采样操作发生在数据眼图的中心位置,以获得最稳定的采样结果。以下是实现这一目的的具体步骤和机制:

启用MPR访问模式:DDR控制器通过设置模式寄存器MR3的第2位(MR3[2])为1,启用对多用途寄存器(MPR)的访问。这样,DRAM在读取操作时就会返回MPR中的数据,而不是直接从DRAM内存读取。

发起连续的读取操作:随后,控制器会发起一系列连续的读取操作。这些读取操作会返回之前在MPR模式写入步骤中写入的数据模式,通常这个模式是交替的1-0-1-0-...序列。

动态调整读取延迟:在读取过程中,控制器内部的读取捕获机制会动态调整内部的读取延迟寄存器,以找到数据眼图的左边缘和右边缘。这通常是通过逐步增加或减少读取延迟来实现的。

确定数据眼图的边缘:当检测到眼图边缘时,读取延迟寄存器会被适当设置,以确保数据始终在眼图的中心位置被捕获。

对每个DQ数据位重复操作:上述步骤会针对每个DQ数据位重复执行,以确保所有数据位的读取操作都能达到最佳性能。

通过这一系列步骤,Read Training (或 Read Centering) 确保了控制器能够在数据眼图的最佳位置进行采样,从而提高了读取数据的稳定性和准确性。这个过程对于确保内存系统的高性能和可靠性至关重要。

6. ZQ Calibration

如果从 DRAM 内部的视角来看,每个 DQ 管脚之后的电路都有多个并联的 240 欧姆电阻组成VOH[0:4]。由于颗粒制造时,CMOS 工艺本身的限制,这些电阻不可能是精确的 240 欧姆。此外,阻值还会随着温度和电压的改变而改变。所以必须校准至接近 240 欧姆,用于提高信号完整性。

现在,连接到DQ校准控制模块的电路本质上是一个电阻分压器电路,其中一个电阻是多晶硅,另一个是精密240Ω。在初始化期间发出命令时,该DQ校准控制模块将启用,DQ校准控制模块中的内部比较器使用p沟道器件进行调谐,直到电压准确(经典电阻分压器)。此时,校准已完成,值将传输到所有DQ引脚。

具体校准过程如下:

(1) 收到ZQ校准命令后,PUP会被驱动为低电平,使和VDDQ连接的PMOS开关打开

(2) 校准控制模块通过调整VOH[0:4], 来使不同的P Channel device导通

(3) 比较VPULL-UP和VDDQ/2的电压,当二者相等时,DQ上下两侧的电阻相等,均为240Ω,记录下该电阻的VOH[0:4]的值。此时,校准已完成,值将传输到所有DQ引脚。

下拉电阻校准过程类似,不多赘述。不同的是和240Ω+电阻并联的是N Channel device。

具有一组并联的240Ω电阻可以调整驱动强度(用于读取)和端接电阻(用于写入)。每个PCB布局都是不同的,因此需要这种调谐功能来提高信号完整性,最大化信号的眼睛尺寸,并允许DRAM高速运行。

(1) 在DQ作为输出时,断掉所有下拉电阻,只有上拉电阻和DQ连接,并且控制上拉电阻的导通个数,来控制输出Voh电压(Output High Voltage)。

(2) 在DQ作为输入时,断掉所有上拉电阻,只有下拉电阻和DQ连接,从而构成ODT需要的下拉ODT(On-Die Termination)终止电阻(RTT),并且通过控制下拉电阻的导通个数,生成需要的不同电阻值的电阻。

7. Preamble 术语解释

7.1 Read Preamble/Postamble

可以看到在DQ信号开始传送的时候,DQS会先有一个从上到下,再往上的信号,维持时间为一个tCK,这个信号我们称之为Read Preamble,其用意主要是在提示Memory Controller Read的资料即将出现。而在DQ信号即将结束的時候DQS也会有一个由下往上的信号,维持时间为0.5个tCK,这个信号我们称之为Read Postamble,其用意主要是在提示Memory Controller Read的资料即将传送结束。

7.2 Write Preamble/Postamble

Write信号也会有Write Preamble和Postamble,我们可以看到Write Preamble也是先上再下的信号,但DQS与DQ的Edge则有一个90度的相位差。

可以通过DQS与DQ的相位是否切齐来判断此时信号为Read or Write,切齐则是read操作,相差90度是write操作。

上描述侧重的是在颗粒端,在MC端(实际是PHY端),Read操作时,DQS在DQ的中间,Write操作时,会通过training的过程决定DQS与DQ的相位关系。

简而言之,在使用 DRAM 之前需要完成 4 个步骤

(1) 上电和初始化

(2) ZQ校准

(3) Vref DQ 校准

(4) 读/写Training

完成此操作后,系统将正式处于空闲状态并正常运行。您可能需要启用定期校准,具体取决于设备的部署条件。

-

DDR

+关注

关注

11文章

748浏览量

68561 -

内存

+关注

关注

9文章

3173浏览量

76131 -

时钟

+关注

关注

11文章

1953浏览量

134574 -

信号完整性

+关注

关注

68文章

1473浏览量

97779

原文标题:DDR training

文章出处:【微信号:封装与高速技术前沿,微信公众号:封装与高速技术前沿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

DDR training的产生原因

DDR training的产生原因

评论