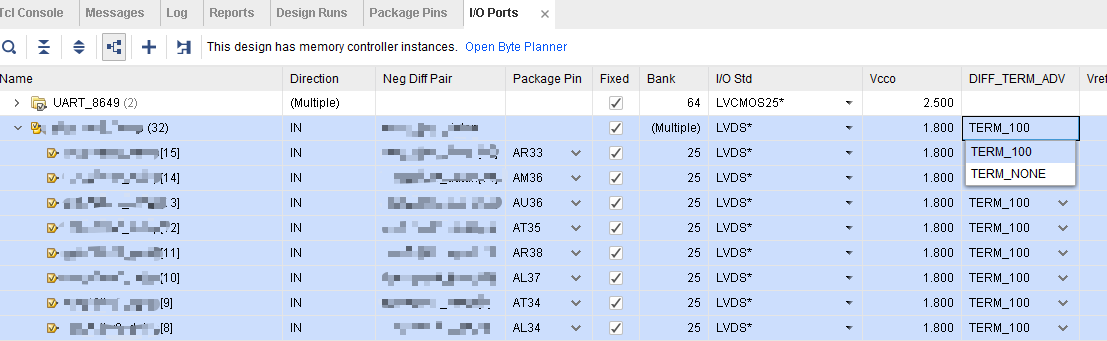

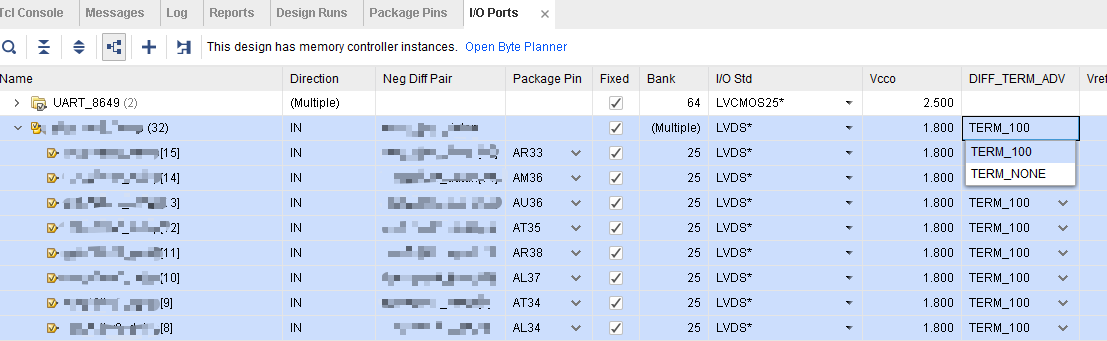

,后者指定了管脚对应的电平标准。 在vivado中,使用如下方式在xdc中对管脚进行约束。 set_property -dict {PACKAGE_PIN AJ16 IOSTANDARD

2020-10-30 16:08:13 17476

17476

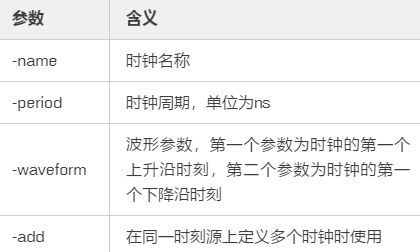

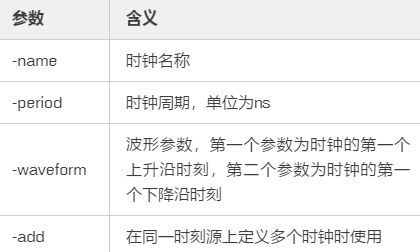

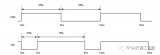

时钟周期约束,顾名思义,就是我们对时钟的周期进行约束,这个约束是我们用的最多的约束了,也是最重要的约束。

2020-11-19 11:44:00 6516

6516

在 Flow Navigator 中点击设置, 然后选择Synthesis,或者 selectFlow Settings Synthesis Settings。 如图1所示: 1、综合约束 在设置

2020-11-23 14:16:36 6670

6670

路径分析问题作一介绍: 1、时钟网络分析 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: ① VivadoIDE中的Flow

2020-11-29 10:34:00 10164

10164 时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 11063

11063 Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-14 09:09:56 2515

2515 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 2392

2392 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 1938

1938

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 12757

12757

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 4234

4234 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 3055

3055 FPGA中时序约束是设计的关键点之一,准确的时钟约束有利于代码功能的完整呈现。进行时序约束,让软件布局布线后的电路能够满足使用的要求。

2023-08-14 17:49:55 2211

2211

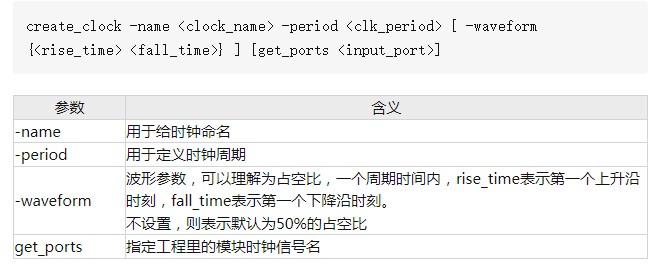

时钟周期约束是用于对时钟周期的约束,属于时序约束中最重要的约束之一。

2023-08-14 18:25:51 1777

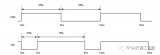

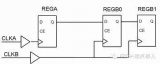

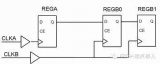

1777 在数字设计中,时钟代表从寄存器(register)到寄存器可靠传输数据的时间基准。

2024-01-04 09:16:09 5877

5877

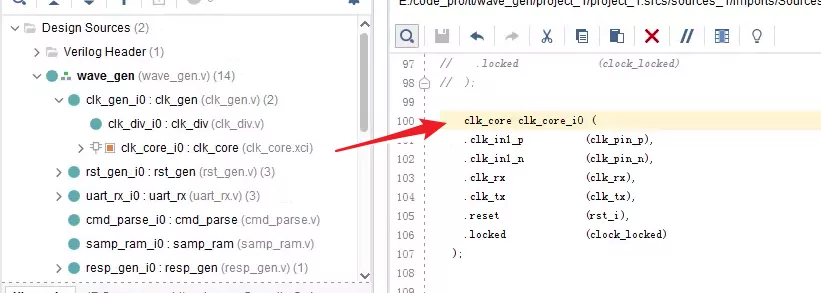

FPGA中的BUFGCE_DIV/BUFG_GT以及Versal中的MBUFG/BUFG_GT等。对于这类时钟,Vivado会自动创建时钟,并不需要用户手工通过create_generated_clock创建。

2024-01-11 09:50:09 3808

3808

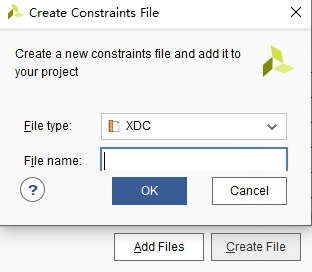

Vivado的时序约束是保存在xdc文件中,添加或创建设计的工程源文件后,需要创建xdc文件设置时序约束。时序约束文件可以直接创建或添加已存在的约束文件,创建约束文件有两种方式:Constraints Wizard和Edit Timing Constraints,在综合后或实现后都可以进行创建。

2025-03-24 09:44:17 4561

4561

在设计以太网中继器时,因为没有配置时钟约束,导致中继器工作不正常。后面根据手册配置时钟约束解决了此问题。

2016-10-07 18:51:24

FPGA的DCM模块,40MHz时钟输入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。对40MHz时钟添加了约束,系统不是会自动对三个输出时钟进行约束

2017-05-25 15:06:47

,FPGA上的全局时钟管脚用完了就出现不够用的情况。FPGA全局时钟约束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

路径。在本实例中,以上的约束将会覆盖如图8.27所示的时钟。(特权同学,版权所有)图8.27 时钟约束可覆盖路径接着,对lcd_clk这个时钟进行约束,它需要约束为虚拟(virtul)时钟,将会被用于

2015-07-30 22:07:42

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

/ 134第5章 IP的管理 / 1355.1 定制IP / 1355.1.1 在Vivado工程中定制IP / 1355.1.2 在Manage IP中定制IP / 1395.2 IP的两种生成文件形式

2020-10-21 18:24:48

出于某种原因,Vivado忽略了我的约束文件,当我尝试在tcl控制台中逐个输入约束时,我尝试分配的每个端口都会出现以下错误:set_property PACKAGE_PIN T19

2018-11-06 11:36:22

(约束指令介绍)UG904 - Vivado Design Suite User Guide -Implementation UG906- Vivado Design Suite User Guide

2018-09-26 15:35:59

转自:VIVADO时序分析练习时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里

2018-08-22 11:45:54

小技巧和帮助来设置时钟;使用像Synopsys Synplify Premier一样的工具正确地设置时序约束;然后调整参数使之满足赛灵思FPGA设计性能的目标。会有来自不同角度的挑战,包括:?更好

2021-05-18 15:55:00

正如它在tittle中所说,当我使用vivado 2016.1时。 vivado做了不完整的事情。Fist.it在我的约束文件中将someuppercase改为小写,这个动作导致我的constain

2020-05-22 06:10:23

问题:

1.如何写入 eMMC 中的正确区域?

2. 将 img 文件转换为写入 eMMC 所需的格式需要做什么?

2025-07-17 07:21:49

新人学习LABVIEW ,我写了一个小程序,目的用来控制34401A万用表,使其响应指令的操作。附件有该框图以及万用表的使用说明书我在指令中输入*IDN? 时,在读取缓冲区显示了正确的仪器信息,说明

2014-04-30 12:58:03

1. Bootloader如何写入Flash ?初学者一般都会遇到如何将程序写入处理器的问题。对于不同的处理器,可以采用不同的方法。例如Intel的Xscale处理器可以...

2021-12-22 07:32:32

的MRCC或SRCC引脚上,在编译时,Vivado通常可能会报错。此时,我们可以通过在工程的.xdc约束文件中添加如下CLOCK_DEDICATED_ROUTE命令,来忽略这个报错,让编译继续进行

2020-09-15 13:30:49

在Vivado 2016.1和Kintex-7 FPGA中,我可以使用名为“Clocking Wizard v5.3”的IP来配置为我的项目输出系统时钟的MMCM。自定义此IP后,将自动为IP生成约束

2019-08-02 09:54:40

Xilinx工具:vivado在该图中,TX_CLK_i连接到pll_x1模块的输入时钟。然后,pll_x1的输出时钟连接到ODDR。接下来,ODDR的输出引脚将连接到I / O引脚

2020-05-04 08:04:41

在给 FPGA 做逻辑综合和布局布线时,需要在工具中设定时序的约束。通常,在 FPGA 中都包含有4 种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入 到输出的纯组合逻辑

2012-03-05 15:02:22

小技巧和帮助来设置时钟;使用像Synopsys Synplify Premier一样的工具正确地设置时序约束;然后调整参数使之满足赛灵思FPGA设计性能的目标。 会有来自不同角度的挑战,包括:更好

2019-08-11 08:30:00

我在vivado 2016.3中看到了以下地方的错误错误:[放置30-675]支持全局时钟的IO引脚和BUFG对的次优放置。如果此子设计可接受此子优化条件,则可以使用.xdc文件中

2018-11-09 11:37:33

如果我正确读取Spartan3数据表,每个Spartan3中都有一个内部硅振荡器,可以配置为CCLK时钟,用于在主串行模式下配置FPGA,并且有一个PERSIST选项可以在配置后保持时钟开启。我

2019-05-07 13:40:54

秒(100 Mhz)关闭和打开一个LED,我这样做是为了验证如何更改ZYNQ的时钟频率使用vivado的约束。这是我放在.xdc文件中生成不同的时钟频率set_property PACKAGE_PIN

2020-04-01 08:46:16

大家好,工具:Vivado 15.2设备:xc7vx485tffg1761-2我对vivado中的input_delay(计算trco和tfco)约束有些怀疑。我的主板包含一个FPGA和四个ADC

2020-04-13 09:20:06

大家好,使用UCF文件中的ISE,我习惯于在输入焊盘和第一个触发器之间的信号上设置maxdelay约束,特别是在总线信号上,以确保总线的所有信号具有大致相同的传播时间。使用Vivado,我无法在

2018-10-25 15:17:18

文件中匹配目标的时候,在可行的情况下更倾向于使用正则表达式。本文就介绍一下我常使用的正则表达式和一些在Vivado中应用的特殊之处,同时也有个别自己尚未解决的问题。

2021-01-26 07:03:16

DCMl输出: clkfx = 100MHz和clkfx_180=100MHz不过相位差180度.FPGA输出到DAC中,DAC需要FPGA提供data[11:0]和写入时钟. 我用clkfx作为

2012-03-29 09:51:36

DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟电路是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 在Vivado中通过set_clock_groups来约束不同的时钟组,它有三个选项分别是-asynchronous,-logically_exclusive

2017-02-08 08:39:49 1357

1357

偏移约束。 这里先说一下周期约束:周期约束是为了达到同步组件的时序要求。如果相邻同步原件相位相反,那么延迟就会是时钟约束值的一半,一般不要同时使用上升沿和下降沿。注意:在实际工程中,附加的约束时间为期望值的

2017-02-09 02:56:06 918

918 最近有些朋友在ISE中做的V7项目需要切换到vivado来,但导入代码后,导入约束时,发现vivado不再支持UCF文件,如果手抄UCF约束到 VIVADO 的 XDC 约束,不仅浪费时间,而且容易出错,这里介绍一种方法可以实现两种约束的切换。

2017-03-24 13:54:36 9459

9459

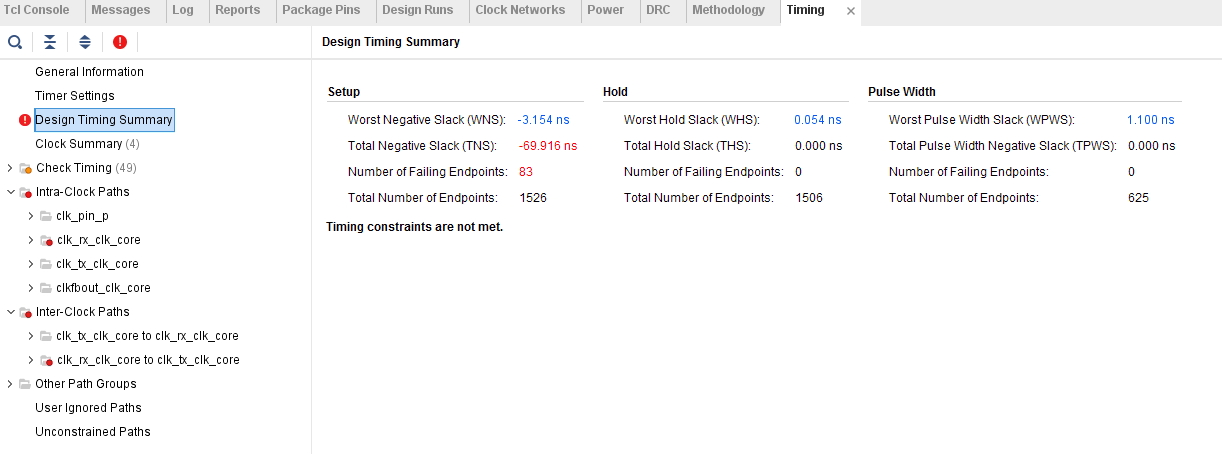

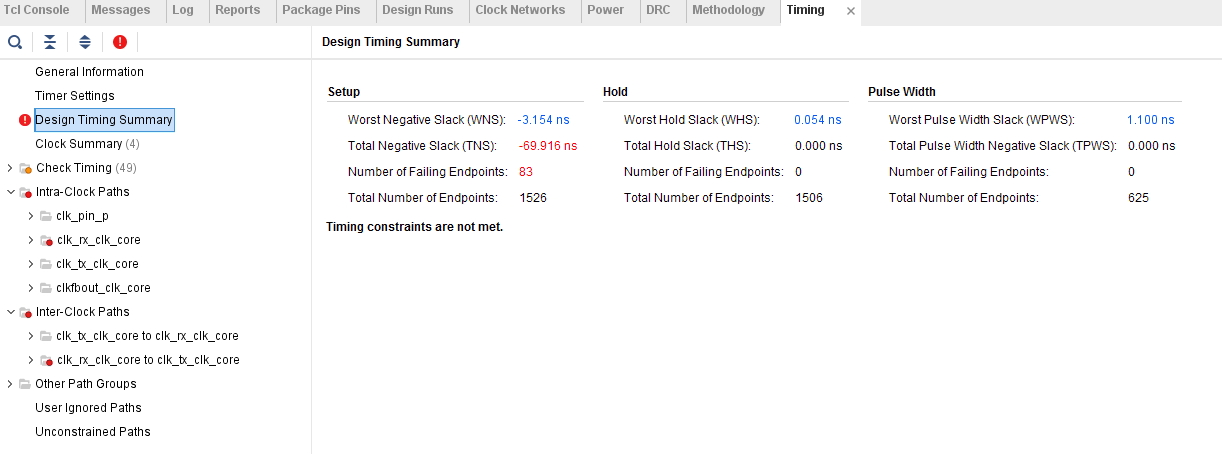

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2967

2967

Vivado时钟的两大特性--时钟延迟和时钟的不确定性。

2017-11-17 11:38:01 6283

6283

《XDC约束技巧》系列中讨论了XDC约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入Vivado中的XDC实际上就是用户设定的目标 ,Vivado对FPGA设计的实现

2017-11-17 18:03:55 39395

39395

Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。本文介绍了Tcl在Vivado中的基础应用,希望起到抛砖引玉的作用,指引使用者在短时间内快速掌握相关技巧,更好地发挥Vivado在FPGA设计中的优势。

2017-11-18 03:52:01 5363

5363

介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,才可能满足约束,约束反过来检查

2018-06-25 09:14:00 7199

7199 现在的硬件设计中,大量的时钟之间彼此相互连接是很典型的现象。为了保证Vivado优化到关键路径,我们必须要理解时钟之间是如何相互作用,也就是同步和异步时钟之间是如何联系。同步时钟是彼此联系的时钟

2019-07-15 15:35:23 7191

7191 时钟是FPGA设计中最重要的信号,FPGA系统内大部分器件的动作都是在时钟的上升沿或者下降沿进行。

2019-09-20 15:10:18 6055

6055

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够

2020-01-28 17:34:00 4750

4750

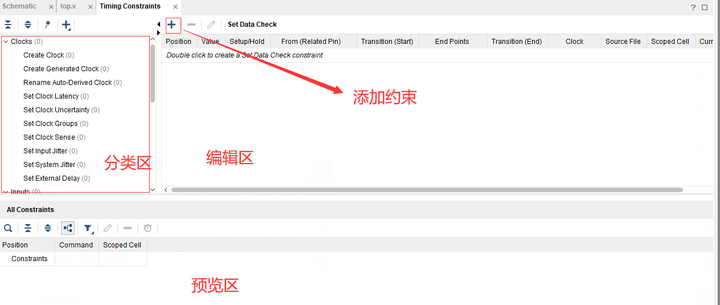

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

2020-03-08 17:17:00 20443

20443

确定了主时钟和衍生时钟后,再看各个时钟是否有交互,即clka产生的数据是否在clkb的时钟域中被使用。

2020-04-06 10:20:00 5354

5354 Vivado IDE约束管理器将任何已编辑的约束保存回XDC文件中的原始位置,但不会保存在Tcl脚本中。 任何新约束都保存在标记为目标的XDC文件的末尾。

2020-11-13 10:53:38 5530

5530

Timing Report中提示warning,并不会导致时序错误,这也会让很多同学误以为这个约束可有可无。 但其实这种想法是不对的,比如在很多ADC的设计中,输出的时钟的边沿刚好是数据的中心位置,而如果我们不加延迟约束,则Vivado会默认时钟和数据是对齐的。 对

2020-11-14 10:34:35 4075

4075

伪路径约束 在本章节的2 约束主时钟一节中,我们看到在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径

2020-11-14 11:28:10 3628

3628

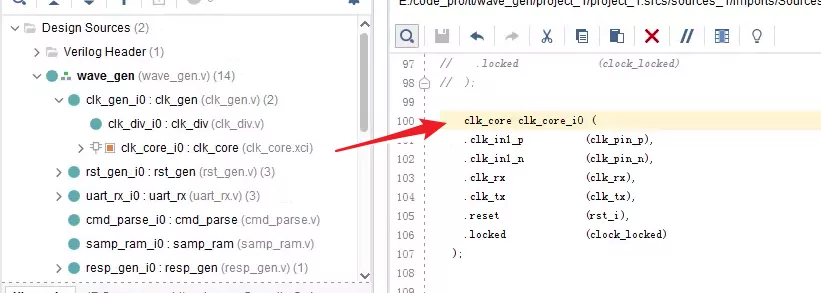

约束衍生时钟 系统中有4个衍生时钟,但其中有两个是MMCM输出的,不需要我们手动约束,因此我们只需要对clk_samp和spi_clk进行约束即可。约束如下

2020-11-17 16:28:05 3234

3234

约束主时钟 在这一节开讲之前,我们先把wave_gen工程的wave_gen_timing.xdc中的内容都删掉,即先看下在没有任何时序约束的情况下会综合出什么结果? 对工程综合

2020-11-16 17:45:06 4147

4147

,还是从对使用者思路的要求,都是全新的;在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。 本文介绍了Tcl在V

2020-11-17 17:32:26 3306

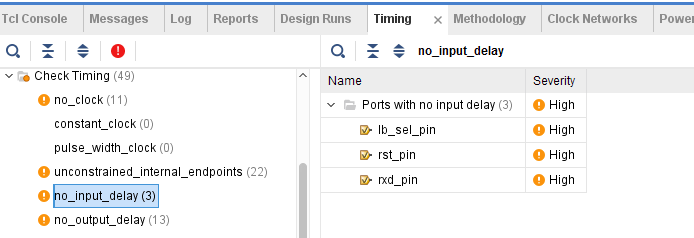

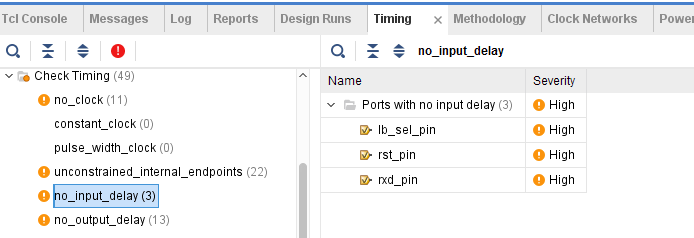

3306 1 I/O延迟约束介绍 要在设计中精确建模外部时序,必须为输入和输出端口提供时序信息。Xilinx Vivado集成设计环境(IDE)仅在FPGA边界内识别时序,因此必须使用以下命令指定超出这些边界

2020-11-29 10:01:16 6236

6236 create_clock:和其他FPGA EDA tool一样,在vivado中timing约束越全越好,越细越好,而place约束可以很粗略或者省略调。约束中最常用的语句就是

2021-01-12 17:31:39 21

21 有人希望能谈谈在做FPGA设计的时候,如何理解和使用过约束。我就以个人的经验谈谈: 什么是过约束; 为什么会使用过约束; 过约束的优点和缺点是什么; 如何使用过约束使自己的设计更为健壮。 什么是过

2021-03-29 11:56:24 6891

6891

在设计FPGA项目的时候,对时钟进行约束,但是因为算法或者硬件的原因,都使得时钟约束出现超差现象,接下来主要就是解决时钟超差问题,主要方法有以下几点。 第一:换一个速度更快点的芯片,altera公司

2021-10-11 14:52:00 4267

4267

很对人在使用Vivado时喜欢使用多个约束文件对整个工程进行约束,同时Vivado允许设计者使用一个或多个约束文件。虽然使用一个约束文件对于一个完整的编译流程来说看似更方便,但是在一些情况下,这会

2021-10-13 16:56:54 7907

7907 Vivado下set_multicycle_path的使用说明 vivado下多周期路径约束(set_multicycle_path)的使用,set_multicycle_path一般...

2021-12-20 19:12:17 1

1 对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

2022-02-16 16:21:36 2136

2136

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 2166

2166

【问题8.1】 VIVADO的时钟约束向导,常无法找到时钟,如下图所示,位置1中应该要识别出时钟。

2022-06-10 06:28:34 2746

2746

XDC约束可以用一个或多个XDC文件,也可以用Tcl脚本实现;XDC文件或Tcl脚本都要加入到工程的某个约束集(set)中;虽然一个约束集可以同时添加两种类型约束,但是Tcl脚本不受Vivado工具管理,因此无法修改其中的约束;

2022-06-30 11:27:23 5420

5420 FPGA端挂载DDR时,对FPGA引脚的约束和选择并不是随意的,有一定的约束规则,一般可以通过利用vivado工具中的pin assignment去选择合适的位置辅助原理图设计。

2022-07-03 17:20:44 6346

6346 时钟周期约束: 时钟周期约束,顾名思义,就是我们对时钟的周期进行约束,这个约束是我们用的最多的约束了,也是最重要的约束。

2022-08-05 12:50:01 5047

5047 Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-19 16:20:51 2298

2298 Vivado工具在编译时通常会自动识别设计中的时钟网络,并将其分配到专用的时钟布局布线资源中。

2022-10-24 15:23:11 4957

4957 数字设计中的时钟与约束 本文作者 IClearner 在此特别鸣谢 最近做完了synopsys的DC workshop,涉及到时钟的建模/约束,这里就来聊聊数字中的时钟(与建模)吧。主要内容如下所示

2023-01-28 07:53:00 4179

4179

Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43:09 2185

2185 《XDC 约束技巧》系列中讨论了XDC 约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入 Vivado中 的 XDC 实际上就是用户设定的目标,Vivado

2023-05-04 11:20:31 5693

5693

关于 Tcl 在 Vivado中的应用文章从 Tcl 的基本语法和在 Vivado 中的 应用展开,继上篇《用 Tcl 定制 Vivado 设计实现流程》介绍了如何扩展甚 至是定制 FPGA

2023-05-05 15:34:52 4104

4104

前面几篇文章已经详细介绍了FPGA时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。

2023-06-23 17:44:00 4086

4086

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 1252

1252

FPGA设计中,时序约束对于电路性能和可靠性非常重要。

2023-06-26 14:53:53 6881

6881

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 6080

6080

Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束,有利于综合逻辑的优化,同时综合后的design里面可以评估时序。

2023-07-03 09:03:19 1424

1424 时钟是每个 FPGA 设计的核心。如果我们正确地设计时钟架构、没有 CDC 问题并正确进行约束设计,就可以减少与工具斗争的时间。

2023-07-12 11:17:42 1817

1817

'sys_clk'. [timing.xdc:37](63 more like this) A:对于约束的问题,我们可以在Vivado的tcl中先执行一下这些约束指令,如果有

2023-08-08 14:10:48 2217

2217 电子发烧友网站提供《Vivado Design Suite用户指南:使用约束.pdf》资料免费下载

2023-09-13 15:48:39 2

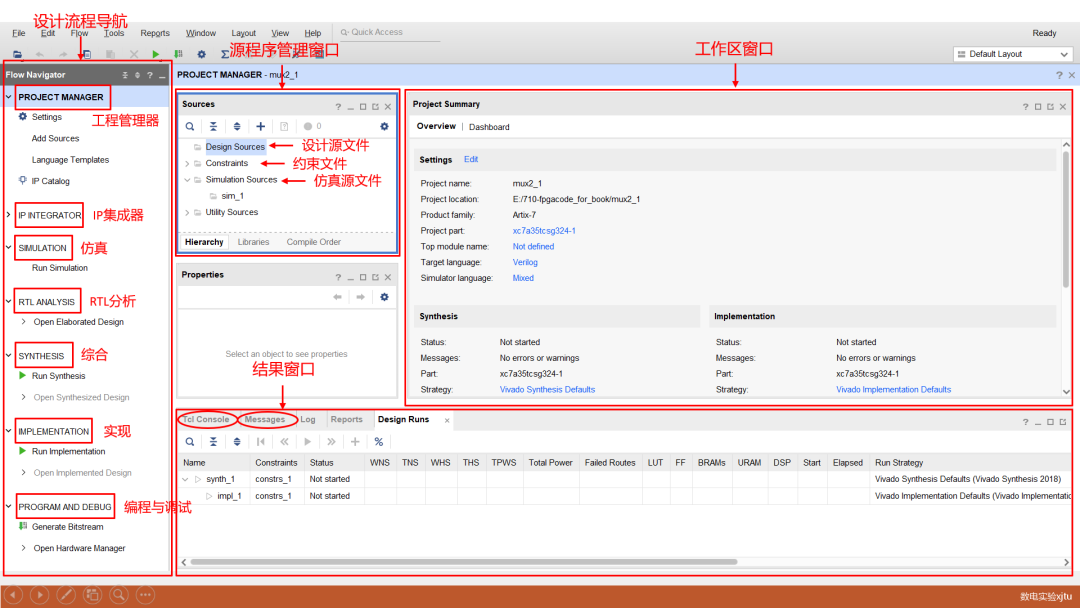

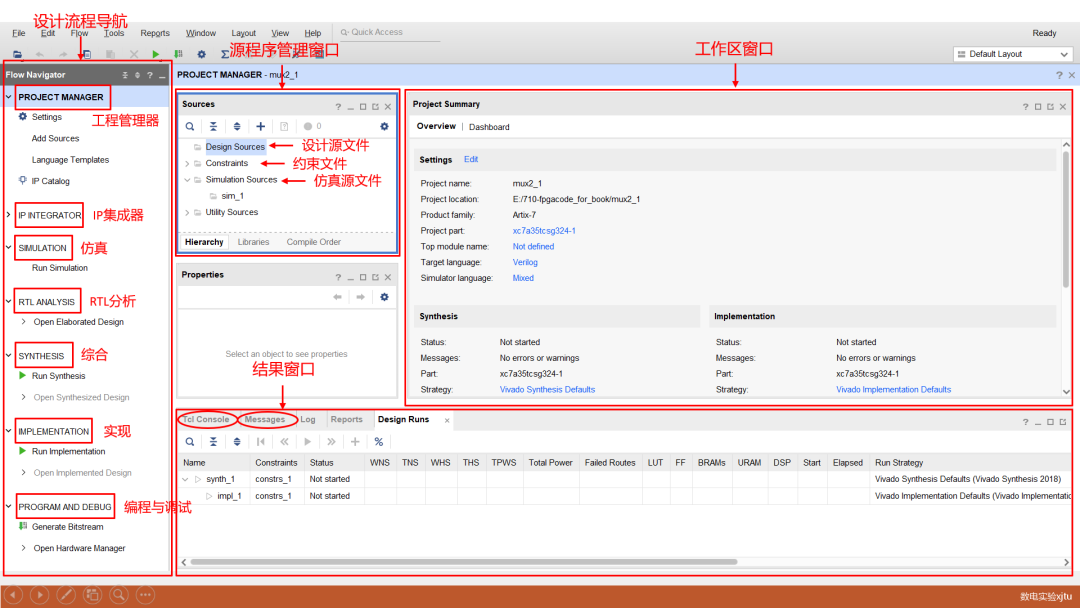

2 Vivado设计主界面,它的左边是设计流程导航窗口,是按照FPGA的设计流程设置的,只要按照导航窗口一项一项往下进行,就会完成从设计输入到最后下载到开发板上的整个设计流程。

2023-09-17 15:40:17 4711

4711

电子发烧友网站提供《如何写入tinyAVR 1系列器件中的闪存和EEPROM.pdf》资料免费下载

2023-09-25 09:55:19 0

0 LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。

2024-04-26 17:05:05 2426

2426

建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2024-08-06 11:40:18 2366

2366

后的约束在之前版本中已存在,那么Vivado会给出警告信息,显示这些约束会覆盖之前已有的约束;如果是新增约束,那么就会直接生效。

2024-10-24 15:08:40 1602

1602

一、主时钟create_clock 1.1 定义 主时钟是来自FPGA芯片外部的时钟,通过时钟输入端口或高速收发器GT的输出引脚进入FPGA内部。对于赛灵思7系列的器件,主时钟必须手动定义到GT

2024-11-29 11:03:42 2322

2322

Vivado中时序分析工具默认会分析设计中所有时钟相关的时序路径,除非时序约束中设置了时钟组或false路径。使用set_clock_groups命令可以使时序分析工具不分析时钟组中时钟的时序路径,使用set_false_path约束则会双向忽略时钟间的时序路径

2025-04-23 09:50:28 1079

1079

电子发烧友App

电子发烧友App

评论