在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序的约束。通常,在FPGA设计工具中都FPGA中包含有4种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入到输出的纯组合逻辑

2023-10-12 12:00:02 2179

2179

约束流程 说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为系统同步与源同步两大类。简单点来说,系统同步是指

2020-11-20 14:44:52 9155

9155

路径分析问题作一介绍: 1、时钟网络分析 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: ① VivadoIDE中的Flow

2020-11-29 10:34:00 10164

10164 引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2022-07-25 10:13:44 5970

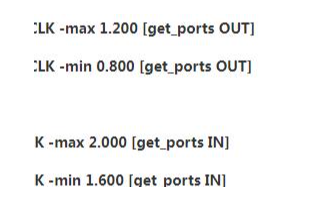

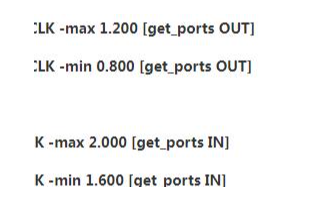

5970 set_input_delay属于时序约束中的IO约束,我之前的时序约束教程中,有一篇关于set_input_delay的文章,但里面写的并不是很详细,今天我们就来详细分析一下,这个约束应该如何使用。

2022-09-06 09:22:02 2908

2908 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 2392

2392 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 1938

1938

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 12757

12757

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 4234

4234 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 3055

3055 在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。

2023-06-26 14:47:16 3379

3379

FPGA中时序约束是设计的关键点之一,准确的时钟约束有利于代码功能的完整呈现。进行时序约束,让软件布局布线后的电路能够满足使用的要求。

2023-08-14 17:49:55 2211

2211

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 3030

3030

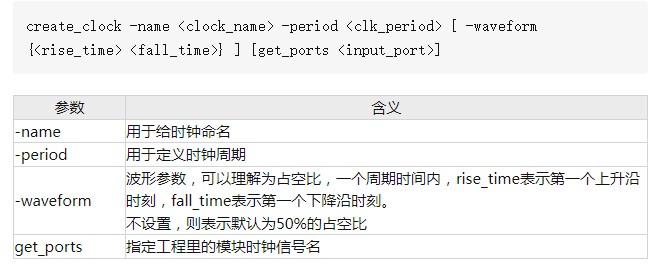

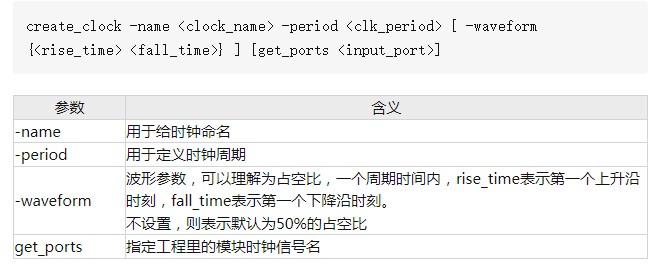

时钟周期约束是用于对时钟周期的约束,属于时序约束中最重要的约束之一。

2023-08-14 18:25:51 1777

1777 嗨,我是初学者,在FPGA上设计系统。我检查了我的输出没有生成,所以我想要。我有5个子模块,它们具有来自相同输入的时钟。据我所知,考虑到不同金属与时钟输入的不同延迟,应对每个子模块进行时钟缓冲。但在

2020-05-22 09:22:23

,FPGA上的全局时钟管脚用完了就出现不够用的情况。FPGA全局时钟约束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

FPGA毕竟不是ASIC,对时序收敛的要求更加严格,本文主要介绍本人在工程中学习到的各种时序约束技巧。 首先强烈推荐阅读官方文档UG903和UG949,这是最重要的参考资料,没有之一。它提倡

2020-12-23 17:42:10

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束

2016-06-02 15:54:04

不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束+时序例外约束+I/O约束 I/O约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时

2017-12-27 09:15:17

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在FPGA中,数据和时钟传输路径是由相应的EDA软件通过针对特定器件的布局布线

2021-07-26 06:56:44

你好: 现在我使用xilinx FPGA进行设计。遇到问题。我不知道FPGA设计是否符合时序要求。我在设计中添加了“时钟”时序约束。我不知道如何添加其他约束。一句话,我不知道哪条路径应该被禁止。我

2019-03-18 13:37:27

FPGA的DCM模块,40MHz时钟输入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。对40MHz时钟添加了约束,系统不是会自动对三个输出时钟进行约束

2017-05-25 15:06:47

更好的信号完整性及更低信噪比2、介绍与数据中心对齐和与数据边缘对齐两种模型,选择哪种模型会影响下游的约束方法的选择。3、单倍数据沿采样很双倍数据沿采样介绍4、数据传输模型介绍:同沿传输和负沿传输;同沿

2014-12-31 14:25:41

在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。通常的做法是设计编写约束文件并导入到综合实现工具,在进行

2023-09-21 07:45:57

FPGA的reset信号需要加什么SDC约束呢?

2023-04-23 11:38:24

,因此,为了避免这种情况,必须对fpga资源布局布线进行时序约束以满足设计要求。因为时钟周期是预先知道的,而触发器之间的延时是未知的(两个触发器之间的延时等于一个时钟周期),所以得通过约束来控制触发器之间的延时。当延时小于一个时钟周期的时候,设计的逻辑才能稳定工作,反之,代码会跑飞。

2018-08-29 09:34:47

`为保证设计的成功,设计人员必须确保设计能在特定时限内完成指定任务。要实现这个目的,我们可将时序约束应用于连线中——从某 FPGA 元件到 FPGA 内部或 FPGA 所在 PCB 上后续元件输入

2012-03-01 15:08:40

(rxdata)发送回vlx75T。有连接器在FPGA之间连接它们。我想知道 -1)为进入vlx760t FPGA的txdata和clk线的约束添加偏移是“强制性的”吗?甚至没有约束的偏移,设计仍然可以工作?2

2019-04-08 10:27:05

(约束指令介绍)UG904 - Vivado Design Suite User Guide -Implementation UG906- Vivado Design Suite User Guide

2018-09-26 15:35:59

完成顶层模块的实现并且仿真正确后,还需要编写用户约束文件,其中引脚约束文件是必不可少的,它将模块的端口和 FPGA 的管脚对应起来。具体步骤如下。(1)创建约束文件。新建一个源文件,在代码类型中选

2018-09-29 09:18:05

本视频是MiniStar FPGA开发板的配套视频课程,主要通过工程实例介绍Gowin的物理约束和时序约束,课程内容包括gowin的管脚约束及其他物理约束和时序优化,以及常用的几种时序约束。 本

2021-05-06 15:40:44

明德扬时序约束视频简介FPGA时序约束是FPGA设计中的一个重点,也是难点。很多人面对各种时序概念、时序计算公式、时序场景是一头乱麻,望而生畏。现有的教材大部分是介绍概念、时序分析工具和计算公式

2017-06-14 15:42:26

FPGA input delay约束的方法该视频抛弃复杂的理论,按照工程实际情况,分析各种情况,只要选择正确情况然后约束即可。mdy-edu.com/article_cat/video?id

2017-03-04 14:55:43

我们在实现FPGA逻辑电路时,时常会在Verilog代码里添加一些约束原语。前言我们在描述FPGA电路时,我们经常会在电路里添加一些像这样的约束原语:通过这种方式,我们可以指导FPGA在综合及布局

2022-07-22 14:28:10

求大神详细介绍一下FPGA嵌入式系统开发过程中的XBD文件设计

2021-05-06 08:19:58

求大神详细介绍一下基于FPGA的电子稳像平台的研究

2021-05-07 06:02:47

大家好我正在使用Virtex5 FPGA,我在设计中添加了一个OFFSET IN约束,如下所示。NET“Sysclk”TNM_NET =“Sysclk”;TIMESPEC“TS_Sysclk

2020-06-13 19:23:05

该文提出一种基于时间约束的FPGA数字水印技术,其基本思想是将准备好的水印标记嵌人非关键路径上的时间约束来定制最终的下载比特流文件,同时并不改变设计的原始性能.这一方

2010-06-09 07:45:49 7

7 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 赛灵思FPGA设计时序约束指南,下来看看

2016-05-11 11:30:19 49

49 FPGA学习资料教程之Xilinx-FPGA-引脚功能详细介绍

2016-09-01 15:27:27 0

0 引脚和区域约束也就是LOC约束(location)。定义了模块端口和FPGA上的引脚的对应关系。 那么我们应该怎么写呢?

2018-07-14 02:49:00 11898

11898 时序约束可以使得布线的成功率的提高,减少ISE布局布线时间。这时候用到的全局约束就有周期约束和偏移约束。周期约束就是根据时钟频率的不同划分为不同的时钟域,添加各自周期约束。对于模块的输入输出端口添加

2017-02-09 02:56:06 918

918 Xilinx FPGA编程技巧常用时序约束介绍,具体的跟随小编一起来了解一下。

2018-07-14 07:18:00 5223

5223

FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。

2017-02-11 06:33:11 2023

2023 作时序和布局约束是实现设计要求的关键因素。本文是介绍其使用方法的入门读物。 完成 RTL 设计只是 FPGA 设计量产准备工作中的一部分。接下来的挑战是确保设计满足芯片内的时序和性能要求。为此,您

2017-11-17 05:23:01 3260

3260

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2967

2967

针对八通道采样器AD9252的高速串行数据接口的特点,提出了一种基于FPGA时序约束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行数据,利用FPGA内部的时钟管理模块DCM、位置约束

2017-11-17 12:27:01 7352

7352

XDC中的I/O约束虽然形式简单,但整体思路和约束方法却与UCF大相径庭。加之FPGA的应用特性决定了其在接口上有多种构建和实现方式,所以从UCF到XDC的转换过程中,最具挑战的可以说便是本文将要

2017-11-17 19:01:00 8137

8137

作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 5955

5955

本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。 Xilinx定义了如下几种约束类型

2017-11-24 19:59:29 4435

4435

在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序的约束。通常,在FPGA设计工具中都FPGA中包含有4种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入到输出的纯组合逻辑

2017-11-24 20:12:54 2067

2067 摘要:本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。 Xilinx定义了如下几种约束类型

2017-11-25 01:27:02 7029

7029

在简单电路中,当频率较低时,数字信号的边沿时间可以忽略时,无需考虑时序约束。但在复杂电路中,为了减少系统中各部分延时,使系统协同工作,提高运行频率,需要进行时序约束。通常当频率高于50MHz时,需要考虑时序约束。

2018-03-30 13:42:59 15212

15212

本文档的主要内容详细介绍的是SOPC和FPGA的介绍和基础实验的详细资料概述包括了:FPGA基础实验一FPGA实现按键控制LED,FPGA实验二数码管显示实验,SOPC基础实验一LED实验,SOPC基础实验二片外存储器的应用

2018-06-19 08:00:00 15

15 观看视频,了解和学习有关XDC约束,包括时序,以及物理约束相关知识。

2019-01-07 07:10:00 7145

7145

本文档的主要内容详细介绍的是FPGA的系统设计及应用的详细视频教程免费下载。

2019-02-26 14:14:32 9

9 本文档详细介绍的是FPGA教程之CPLD和FPGA的配置与下载的详细资料说明主要内容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下载配置,三、FLEX/ACEX系列FPGA的下载配置,四、ALTERA的编程文件

2019-02-28 09:56:18 20

20 本文档的主要内容详细介绍的是FPGA视频教程之FPGA开发流程的详细资料概述免费下载。

2019-03-01 11:35:37 11

11 本文档的主要内容详细介绍的是FPGA视频教程之BJ-EPM240学习板的详细资料说明免费下载,BJ-EPM240学习板是一款FPGA/CPLD入门级学习板。

2019-03-01 11:35:52 21

21 本文档的主要内容详细介绍的是FPGA教程之FPGA入门闪烁灯实验的详细资料说明。

2019-03-29 17:17:06 25

25 本文档的主要内容详细介绍的是FPGA教程之FPGA系统设计与应用的详细资料说明包括了:1.Altera的FPGA体系结构简介,2.Altera的FPGA选型策略,3.嵌入式逻辑分析工具SignalTAPII的使用4.基于CPLD的FPGA配置方法

2019-04-04 17:47:03 62

62 本文档的主要内容详细介绍的是在写Verilog时对时序约束的四大步骤的详细资料说明包括了:一、 时钟,二、 Input delays,三、 Output delays,四、 时序例外

2019-08-30 08:00:00 32

32 FPGA在与外部器件打交道时,端口如果为输入则与input delay约束相关,如果最为输出则output delay,这两种约束的值究竟是什么涵义,在下文中我也会重点刨析,但是前提是需要理解图1和图2建立余量和保持余量。

2019-11-10 10:06:23 5266

5266

伪路径约束 在本章节的2 约束主时钟一节中,我们看到在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径

2020-11-14 11:28:10 3628

3628

时序分析结果,并根据设计者的修复使设计完全满足时序约束的要求。本章包括以下几个部分: 1.1 静态时序分析简介 1.2 FPGA 设计流程 1.3 TimeQuest 的使用 1.4 常用时序约束 1.5 时序分析的基本概念

2020-11-11 08:00:00 67

67 本文档的主要内容详细介绍的是FPGA的入门基础知识详细说明。

2020-12-20 10:13:30 10643

10643

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

2021-01-11 17:44:44 8

8 说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为系统同步与源同步两大类。简单点来说,系统同步是指FPGA与外部

2021-01-11 17:46:32 14

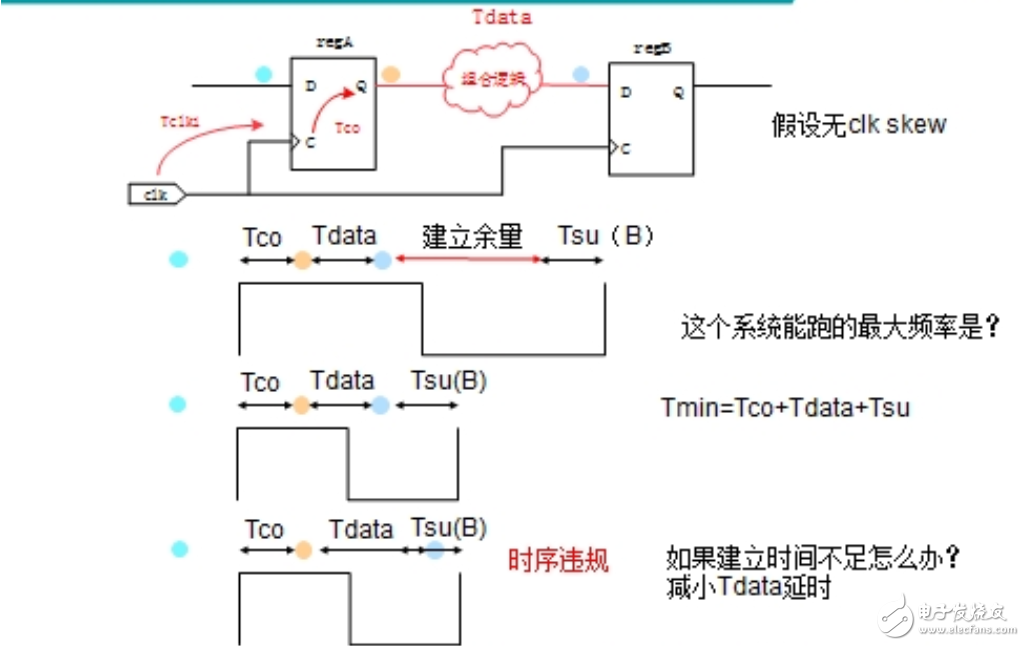

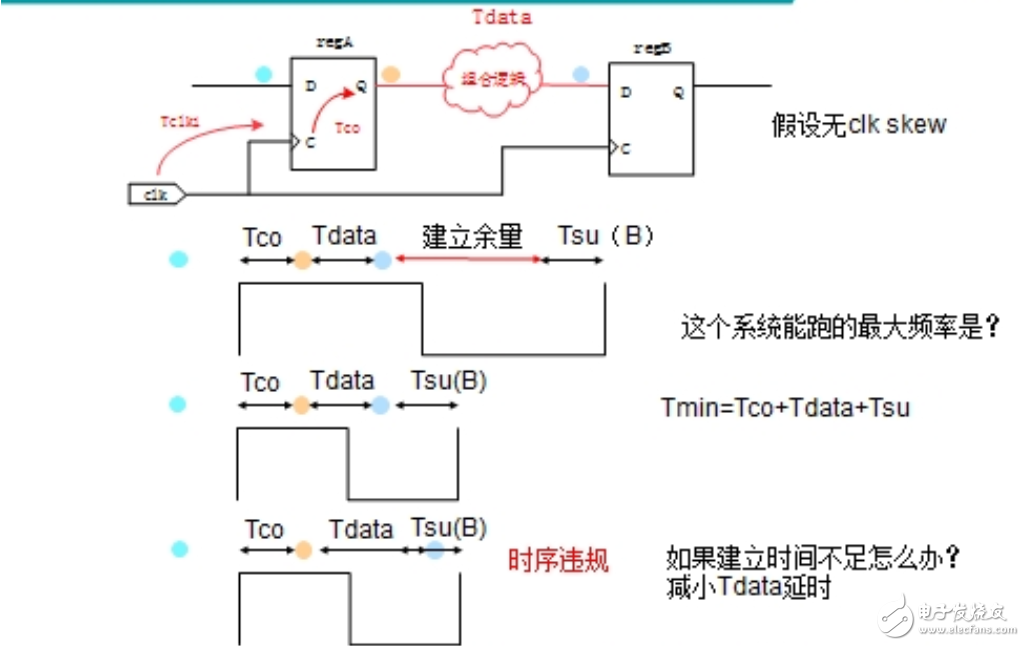

14 组合逻辑延迟和走线延迟。Tsu表示捕获寄存器建立时间要求。Th表示捕获寄存器保持时间要求。其中Tco、Tsu和Th是由FPGA的芯片工艺决定的。所以,我们所谓的时序约束,实际上就是对时钟延迟和Tdata做一定的要求或者干预,其中Tdata由组合逻辑(代码)及布局布线决定,这也决

2021-01-12 17:31:36 9

9 在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束。这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的。好的时序约束可以指导布局布线工具进行权衡,获得最优的器件性能,使设计代码最大可能的反映设计者的设计意图。

2021-01-12 17:31:00 8

8 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是重点。只有约東正确才能在高速情况下保证FPGA和外部器件通信正确

2021-01-13 17:13:00 11

11 功耗是我们关注的设计焦点之一,优秀的器件设计往往具备低功耗特点。在前两篇文章中,小编对基于Freez技术的低功耗设计以及FPGA低功耗设计有所介绍。为增进大家对低功耗的了解,以及方便大家更好的实现低功耗设计,本文将对FPGA具备的功耗加以详细阐述。如果你对低功耗具有兴趣,不妨继续往下阅读哦。

2021-02-14 17:50:00 7165

7165 本文档的主要内容详细介绍的是Xilinx的时序设计与约束资料详细说明。

2021-01-14 16:26:51 34

34 有人希望能谈谈在做FPGA设计的时候,如何理解和使用过约束。我就以个人的经验谈谈: 什么是过约束; 为什么会使用过约束; 过约束的优点和缺点是什么; 如何使用过约束使自己的设计更为健壮。 什么是过

2021-03-29 11:56:24 6891

6891

引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2021-04-27 10:36:59 6127

6127

A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加

2021-09-30 15:17:46 5927

5927 在设计FPGA项目的时候,对时钟进行约束,但是因为算法或者硬件的原因,都使得时钟约束出现超差现象,接下来主要就是解决时钟超差问题,主要方法有以下几点。 第一:换一个速度更快点的芯片,altera公司

2021-10-11 14:52:00 4267

4267

FPGA图像处理应用详细介绍

2022-02-28 10:29:49 51

51 本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-03-16 09:17:19 4001

4001

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 2166

2166

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-05-11 10:07:56 4989

4989

明德扬有完整的时序约束课程与理论,接下来我们会一章一章以图文结合的形式与大家分享时序约束的知识。要掌握FPGA时序约束,了解D触发器以及FPGA运行原理是必备的前提。今天第一章,我们就从D触发器开始讲起。

2022-07-11 11:33:10 6143

6143

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 3757

3757

时钟周期约束: 时钟周期约束,顾名思义,就是我们对时钟的周期进行约束,这个约束是我们用的最多的约束了,也是最重要的约束。

2022-08-05 12:50:01 5047

5047 时序约束是我们对FPGA设计的要求和期望,例如,我们希望FPGA设计可以工作在多快的时钟频率下等等。因此,在时序分析工具开始对我们的FPGA设计进行时序分析前,我们必须为其提供相关的时序约束信息。在

2022-12-28 15:18:38 5209

5209 Pad-to-Setup:也被称为OFFSET IN BEFORE约束,是用来保证外部输入时钟和外部输入数据的时序满足FPGA内部触发器的建立时间要求的。如下图TIN_BEFORE约束使得FPGA在

2023-02-15 11:52:33 3119

3119 上一篇《XDC 约束技巧之时钟篇》介绍了 XDC 的优势以及基本语法,详细说明了如何根据时钟结构和设计要求来创建合适的时钟约束。我们知道 XDC 与 UCF 的根本区别之一就是对跨时钟域路径(CDC

2023-04-03 11:41:42 3390

3390 在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。通常的做法是设计编写约束文件并导入到综合实现工具,在进行

2023-04-27 10:08:22 2404

2404 前面几篇文章已经详细介绍了FPGA时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。

2023-06-23 17:44:00 4086

4086

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 1252

1252

FPGA设计中,时序约束对于电路性能和可靠性非常重要。

2023-06-26 14:53:53 6881

6881

本文将详细介绍输出延时的概念、场景分类、约束参数获取方法以及约束方法

2023-07-11 17:12:50 4481

4481

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。

2024-04-26 17:05:05 2426

2426

建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2024-08-06 11:40:18 2365

2365

xilinx FPGA IOB约束使用以及注意事项 一、什么是IOB约束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距离IO最近的寄存器,同时位置固定。当你输入或者输出

2025-01-16 11:02:01 1657

1657

电子发烧友App

电子发烧友App

评论