时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错。

2020-06-26 10:37:00 6144

6144

静态时序分析包括建立时间分析和保持时间分析。建立时间设置不正确可以通过降低芯片工作频率解决,保持时间设置不正确芯片无法正常工作。

2022-08-22 10:38:24 5380

5380 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 2392

2392 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 1938

1938

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 4234

4234 建立时间(setup time)和保持时间(hold time)是时序分析中最重要的概念之一,深入理解建立时间和保持时间是进行时序分析的基础。

2023-06-21 10:44:01 2768

2768

时序分析本质上就是一种时序检查,目的是检查设计中所有的D触发器是否能够正常工作,也就是检查D触发器的同步端口(数据输入端口)的变化是否满足建立时间要求(Setup)和保持时间要求(Hold);检查D

2023-07-14 10:48:19 5776

5776

今天有个小伙伴遇到一个问题,就是在vivado里面综合后看到的建立时间和保持时间裕量都是inf,我们来看看怎么解决这个问题。

2023-07-30 10:26:02 2193

2193

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 3030

3030

我理解这个D触发正常运转要满足四个约束,第一个是建立时间,第二个是保持时间,第三个是对于最后一个传输门的关断时间的控制,第四个是[时钟周期]() 约束。

2023-12-04 15:44:02 3182

3182

是 FPGA/ASIC 时序定义的基础概念。后面要讲到的其它时序约束都是建立在周期约束的基础上的,很多其它时序公式,可以用周期公式推导。周期约束是一个基本时序和综合约束,它附加在时钟网线上,时序分析工具根据

2024-06-17 17:07:28

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

后期顶层模块集成占用大资源时爆发出来。 下面介绍主要面对的两个时序问题的处理技巧。 1)setup time 建立时间问题 建立时间是工程设计中最常遇到的问题了。一般说来,导致建立时间违例主要有

2020-12-23 17:42:10

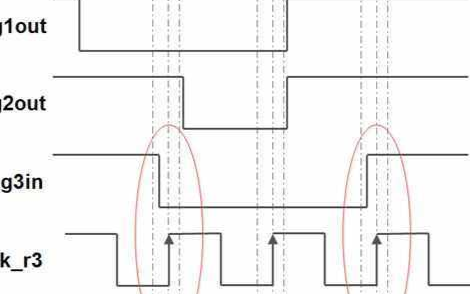

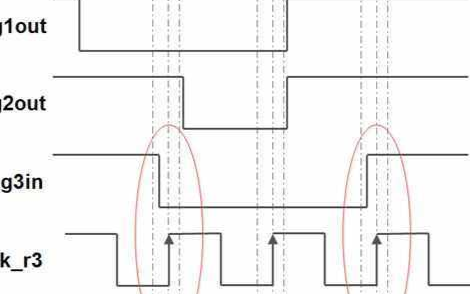

建立时间和保持时间本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 在这个波形中,我们看到clk_r3的前后

2015-07-17 12:02:10

),即pin2pin前面三类是和FPGA内部的寄存器相关的,也是和时钟相关的,所以我们关注的重点还是数据信号和时钟锁存沿之间的建立时间和保持时间关系。而最后一类信号的传输通常不通过时钟,因此它的时序

2015-07-20 14:52:19

对应的时序表中,我们找到了t1>0.2ns,t2>1.5ns这样的信息。表8.1 ADV7123时序参数表参数名称最小值 标准值 最大值单位 数据和控制信号建立时间t1 0.2ns 数据和控制信号保持时间t2 1.5ns

2015-07-26 21:56:45

,最后在计算ADV7123的时序时,我们必须将数据的建立时间Tsu和保持时间Th考虑在内。(特权同学,版权所有)图8.30 时序路径模型

2015-07-30 22:07:42

VGA驱动接口时序设计之4建立和保持时间分析本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt下面我们可以简单

2015-08-02 19:26:19

VGA驱动接口时序设计之6建立和保持时间约束本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 接着,我们可以

2015-08-06 21:49:33

8.42 hold时间时序分析报告为了帮助大家进一步的理解时序的概念,这里可以找一条路径,将他们的建立时间和保持时间波形图同时拉出来,如图8.43所示,大家便可一目了然。建立时间和保持时间会分别使用他

2015-08-10 15:03:08

约束,就是设计者告诉时序设计工具FPGA外部的路径上占用了4ns时间,时序设计工具自己有一套运算机制,它也能运算出FPGA内部的pin2reg时间是6ns。而我们这个模型和所使用的约束方式,是间接方式

2015-08-12 12:42:14

所示,在报告中,数据的建立时间有9~13ns的余量,而保持时间也都有7~11ns的余量,可谓余量充足。(特权同学,版权所有)图8.57 setup时序报告图8.58 hold时序报告另外,我们也可以

2015-08-19 21:58:55

整个系统进行时序分析,所以FPGA需要作为一个整体分析,其中包括FPGA的建立时间、保持时间以及传输延时。传统的建立时间、保持时间以及传输延时都是针对寄存器形式的分析。但是针对整个系统FPGA的建立时间

2012-04-25 15:42:03

如图,建立时间和保持时间都是针对的时钟沿,如图所示,时钟沿有一个上升的过程,图中虚线与clk上升沿的交点是什么?幅值的50%?还是低电平(低于2.5V)往高电平(高于2.5V)跳转的那个点?

2018-11-29 00:20:02

本帖最后由 虎子哥 于 2015-3-12 21:24 编辑

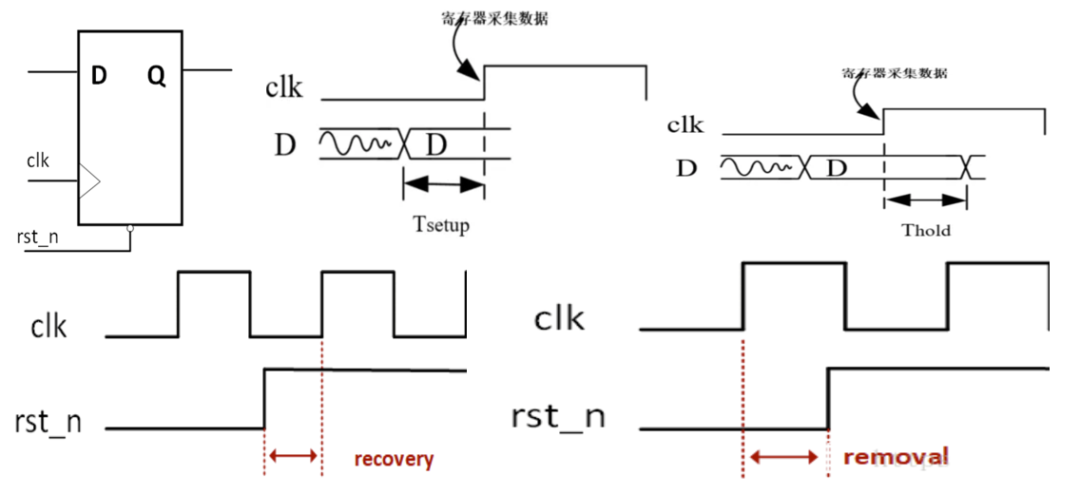

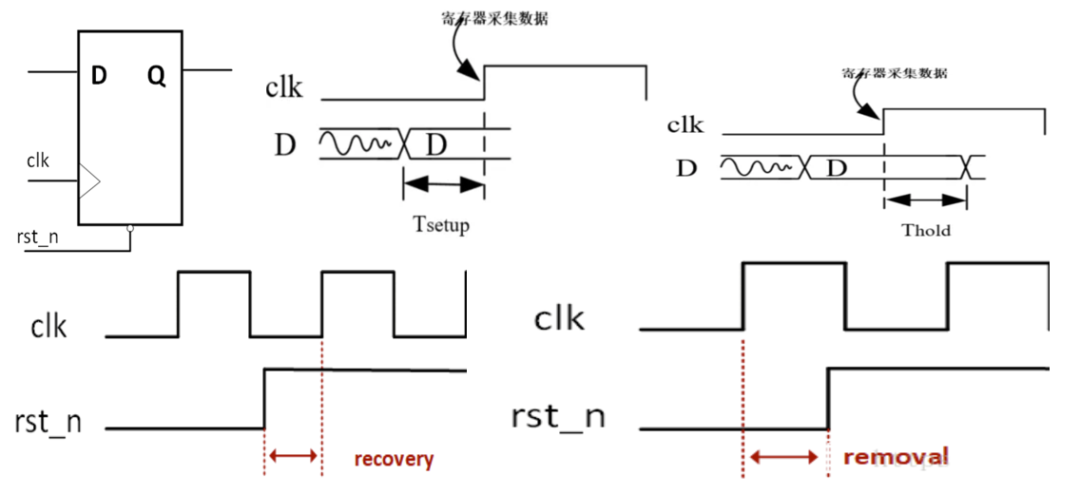

建立时间(Setup Time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟

2015-03-10 23:19:03

工作时钟却只有100MHz,查资料这款FPGA最快可跑四五百M,时序约束也没有不满足建立时间和保持时间的报错,本身整个系统就用了一个时钟,同步设计请教一下,为什么只能跑100MHz?是什么原因限制了呢

2017-08-14 15:07:05

约束中的注意事项。 一、时序分析中的重要概念 在数字系统中有两个非常重要的概念:建立时间和保持时间,其示意图如图1所示。一个数字系统能否正常工作跟这两个概念密切相关。只有建立时间和保持时间都同时得到

2020-08-16 07:25:02

时序约束可以很复杂,这里我们先介绍基本的时序路径约束,复杂的时序约束我们将在后面进行介绍。在本节的主要内容如下所示:·时序路径和关键路径的介绍 ·建立时间、保持时间简述 ·时钟的约束(寄存器-寄存器之间的路径约束) ·输入延时的约束 ·输出延...

2021-07-26 08:11:30

ADC时延和建立时间的区别是什么?以及ADC时延和建立时间将会如何影响您的应用电路?

2021-04-12 07:19:18

有没有人遇到在DC综合后分析建立时间时序,关键路径时序违例是因为起始点是在时钟的下降沿开始驱动的,但是设计中都是时钟上升沿触发的。在线等待各位大牛解惑!很急 求大神帮忙!

2015-01-04 15:17:16

PLL jitter 对建立时间和保持时间有什么样的影响?哪位大神给解答下

2015-10-30 11:16:30

VGA驱动接口时序设计之4建立和保持时间分析本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 下面我们可以

2019-04-10 06:33:34

今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为

2024-05-06 15:51:23

关系。因为时钟是不相关的,所以不可能确定出建立时间、保持时间和时钟的最终关系。因为这个原因,Xilinx推荐使用适当的异步设计技术来保证对数据的成功获取。Xilinx约束系统允许设计者在不需考虑源和目的

2024-04-12 17:39:04

什么是同步逻辑和异步逻辑?同步电路和异步电路的区别在哪?为什么触发器要满足建立时间和保持时间?

2021-09-28 08:51:33

什么是同步逻辑和异步逻辑?同步电路和异步电路的区别在哪?为什么触发器要满足建立时间和保持时间?什么是亚稳态?为什么两级触发器可以防止亚稳态传播?

2021-08-09 06:14:00

什么叫建立时间,保持时间,和恢复时间

2017-04-08 16:52:35

1、FPGA中的时序约束--从原理到实例 基本概念 建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。 电路中的建立时间和保持时间其实跟生活中的红绿灯很像

2022-11-15 15:19:27

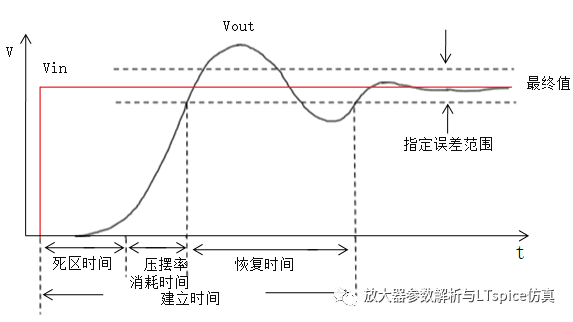

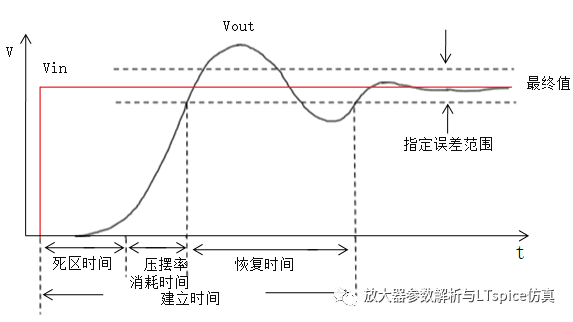

。这种方法把准确性和精确度建立在波形生成器和采样保持电路的相对速度上。 受测器件的步进输入 本文中,建立时间是指使用某个理想步进输入,到受测器件(DUT)进入并维持在某个规定误差范围(终值对称)内

2012-07-30 17:36:20

的工作时钟,通过调整sdram_clk的相位就能调整时序,从而满足建立时间和保持时间的要求。那么sdram_clk如何产生呢?可以通过PLL来产生,PLL可以保证频率相同、相位偏移量,所以该系统的结构

2016-09-13 21:58:50

关于数字IC的建立时间以及保持时间你想知道的都在这

2021-09-18 07:24:40

接口的光以太网数据通信就正常了。 这里阐述了时序分析基础,说明概念的同时进行了时序分析,通过时序分析理解建立时间和保持时间。希望大家阅读本文之后可以对FPGA时序分析有进一步的了解。

2018-04-03 11:19:08

建立时间测量的采样保持方法测试装置存在哪些局限性?

2021-04-09 06:08:05

建立时间(Setup Time)是指触发器的时钟信号上升沿到来之前,数据保持稳定不变的时间。 输入信号应该提前时钟上升沿(如上升沿有效)Tsu时间到达芯片,这个 Tsu就是建立时间。如果不满足建立时间

2021-07-26 07:36:01

请问,对于触发器的时钟信号,建立时间和保持时间有要求吗?刚看到一个门控时钟产生毛刺的反例,(如下图)想到了这个问题。若此时钟信号毛刺极小,有没有可能被触发器忽略呢?为什么呢?如果有可能小到什么程度会被忽略呢?

2012-01-27 18:44:58

16444_[。只有降低SPI频率到20MHz才ok。(2)问题分析:通过示波器测量,发现DM9051的cs建立时间和保持时间很紧张,其它信号质量和时序ok,需要增加cs的建立时间和保持时间来试试。(3

2023-02-15 06:55:16

)问题分析:

通过示波器测量,发现DM9051的cs建立时间和保持时间很紧张,其它信号质量和时序ok,需要增加cs的建立时间和保持时间来试试。

(3)问题解决:

根据

2024-06-18 07:31:22

T2max,最小为T2min。问,触发器D2的建立时间T3和保持时间应满足什么条件

2019-09-09 17:19:55

在PCB走线的延时,因此上图只是一个理想过程,即没有考虑PCB走线的延时,而我们的时序分析工具确实将其考虑在内了,所以,我们的FPGA建立时间,除了包括数据保持稳定的时间外,还应加上这段走线延时的时间

2015-03-31 10:35:18

该文简要讨论了环路性能(建立时间,相位噪声和杂散信号)和环路参数(带宽,相位裕度等)的相互关系。提出并分析了一种自适应的具有快速建立时间的锁相环结构及其关键模块(鉴相

2010-04-23 08:33:53 20

20 该文提出一种基于时间约束的FPGA数字水印技术,其基本思想是将准备好的水印标记嵌人非关键路径上的时间约束来定制最终的下载比特流文件,同时并不改变设计的原始性能.这一方

2010-06-09 07:45:49 7

7 基本概念:线与逻辑、锁存器、缓冲器、建立时间、缓冲时间

基本概念:线与逻辑、锁存器、缓冲器、建立时间、缓冲时间

标签/分类:

2007-08-21 15:17:27 1607

1607 时延和建立时间setup在ADC电路中的区别:对于大多数 ADC 用户来说,“时延”和“建立时间”这两个术语有时可以互换。但对于 ADC 设计人员而言,他们非常清楚

2007-11-22 23:33:07 1940

1940 为实现高速DAC的最佳性能,必须满足一定的建立和保持时间要求。在200 MSPS至250 MSPS的时钟速率下,FPGA/ASIC/DAC的全部时序预算并不是一件小事。客户若要完成时序验证,必须清楚列出并

2011-11-24 14:20:35 33

33 本文将介绍一种新方法,其经过证明可以有效地完成这些测量工作。它是一种相对低成本、简单的建立时间测量方法。这种方法把准确性和精确度建立在波形生成器和采样保持电路的相

2012-07-27 10:25:16 1810

1810

FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 建立时间和保持时间贯穿了整个时序分析过程。只要涉及到同步时序电路,那么必然有上升沿、下降沿采样,那么无法避免setup-time 和 hold-time这两个概念。 1. 什么是setup-time

2017-02-08 14:48:11 7008

7008 经常需要定义时序和布局约束。我们了解一下在基于赛灵思 FPGA 和 SoC 设计系统时如何创建和使用这两种约束。 时序约束 最基本的时序约束定义了系统时钟的工作频率。然而,更高级的约束能建立时钟路径之间

2017-11-17 05:23:01 3260

3260

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2967

2967

和底层工具Planahead实现高速串并转换中数据建立时间和保持时间的要求,实现并行数据的正确输出。最后通过功能测试和时序测试,验证了设计的正确性。此方法可适用于高端和低端FPGA,提高了系统设计的灵活性,降低了系统的成本。

2017-11-17 12:27:01 7352

7352

在简单电路中,当频率较低时,数字信号的边沿时间可以忽略时,无需考虑时序约束。但在复杂电路中,为了减少系统中各部分延时,使系统协同工作,提高运行频率,需要进行时序约束。通常当频率高于50MHz时,需要考虑时序约束。

2018-03-30 13:42:59 15212

15212

FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2019-12-23 07:02:00 4742

4742

FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2019-12-23 07:01:00 2671

2671

时钟是FPGA设计中最重要的信号,FPGA系统内大部分器件的动作都是在时钟的上升沿或者下降沿进行。

2019-06-19 15:04:17 6698

6698

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够

2020-01-28 17:34:00 4750

4750

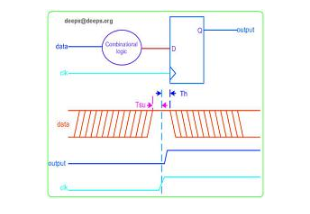

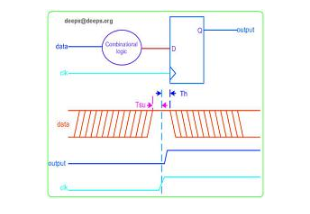

组合逻辑延迟和走线延迟。Tsu表示捕获寄存器建立时间要求。Th表示捕获寄存器保持时间要求。其中Tco、Tsu和Th是由FPGA的芯片工艺决定的。所以,我们所谓的时序约束,实际上就是对时钟延迟和Tdata做一定的要求或者干预,其中Tdata由组合逻辑(代码)及布局布线决定,这也决

2021-01-12 17:31:36 9

9 本篇仿真介绍放大器的建立时间,也称为上升时间。它是高速放大电路、或在SARADC驱动电路设计时,需要谨慎评估的参数。

2021-02-15 16:37:00 7260

7260

AN-359:运算放大器的建立时间

2021-04-29 15:28:46 4

4 约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE约束可以告诉综合布线工具输入信号在时钟之前什么时候准备好,综合布线工具就可以根据这个约束调整与IPAD相连的Logic Circuitry的综合实现过程,使结果满足FFS的建立时间要求。 附加时序

2021-09-30 15:17:46 5927

5927 约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE约束可以告诉综合布线工具输入信号在时钟之前什么时候准备好,综合布线工具就可以根据这个约束调整与IPAD相连的Logic Circuitry的综合实现过程,使结果满足FFS的建立时间要求。 附加时序

2021-10-11 10:23:09 6573

6573

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 2166

2166

时间裕量包括建立时间裕量和保持时间裕量(setup slack和hold slack)。从字面上理解,所谓“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立时间或保持时间所多出的时间,那么“裕量”越多,意味着时序约束越宽松。

2022-08-04 17:45:04 1079

1079 对于建立时间和保持时间本文就不再过多叙述,可参考【FPGA】几种时序问题的常见解决方法-------3,可以说在数字高速信号处理中最基本的概念就是建立时间和保持时间,而我们要做的就是解决亚稳态问题和传输稳定问题。

2022-12-13 11:03:58 707

707 时间裕量包括建立时间裕量和保持时间裕量(setup slack和hold slack)。从字面上理解,所谓“裕量”即富余的、多出的。

2023-02-06 11:06:03 793

793 Pad-to-Setup:也被称为OFFSET IN BEFORE约束,是用来保证外部输入时钟和外部输入数据的时序满足FPGA内部触发器的建立时间要求的。如下图TIN_BEFORE约束使得FPGA在

2023-02-15 11:52:33 3119

3119 本篇通过仿真介绍放大器的建立时间,也称为上升时间。它是高速放大电路、或在SAR ADC驱动电路设计时,需要谨慎评估的参数。

2023-02-22 11:29:31 1919

1919

个风险(时序报告是按照工艺、电压以及温度的上下限给出的结果)。当违例数较多,也就意味着设计在实际环境中出现问题的概率也会越大。 时间裕量包括建立时间裕量和保持时间裕量(setup slack和hold slack)。从字面上理解,所谓“裕量”即富余的、多出的。什

2023-03-17 03:25:03 2014

2014 运算放大器建立时间是保证数据采集系统性能的关键参数。为了实现精确的数据采集,运算放大器输出必须在A/D转换器能够准确数字化数据之前建立。然而,建立时间通常不是一个容易测量的参数。

2023-06-17 10:37:54 1635

1635

本文主要介绍了建立时间和保持时间。

2023-06-21 14:38:26 4826

4826

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 1252

1252

在时序电路设计中,建立时间/保持时间可以说是出现频率最高的几个词之一了,人们对其定义已经耳熟能详,对涉及其的计算(比如检查时序是否正确,计算最大频率等)网上也有很多。

2023-06-27 15:43:55 18883

18883

建立时间和保持时间是SOC设计中的两个重要概念。它们都与时序分析有关,是确保芯片正常工作的关键因素。

2023-08-23 09:44:55 1828

1828 信号经过传输线到达接收端之后,就牵涉到建立时间和保持时间这两个时序参数,它们表征了时钟边沿触发前后数据需要在锁存器的输入持续时间,是接收器本身的特性。简而言之,时钟边沿触发前,要求数据必须存在一段时间,这就是器件需要的建立时间;

2023-09-04 15:16:19 1610

1610

文件提到两种setup/hold测量方式:10% push-up和pass/fail,按照TSMC说法,前者会更乐观一些,因此如果是采用前者(10% push-up)的测量方式得到建立时间和保持时间,需要十份小心时序裕量是否足够,最好人为添加margin。

2023-12-05 11:19:38 3630

3630

建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2024-08-06 11:40:18 2366

2366

电子发烧友App

电子发烧友App

评论