作者:猫叔

延迟约束

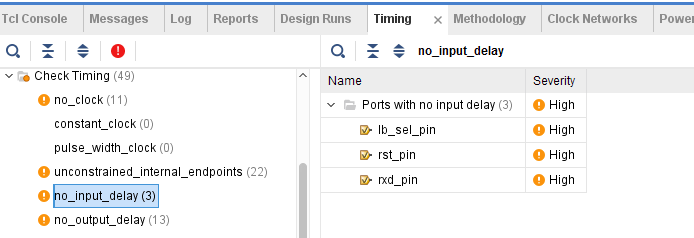

对于延迟约束,相信很多同学是不怎么用的,主要可能就是不熟悉这个约束,也有的是嫌麻烦,因为有时还要计算PCB上的走线延迟导致的时间差。而且不加延迟约束,Vivado也只是在Timing Report中提示warning,并不会导致时序错误,这也会让很多同学误以为这个约束可有可无。

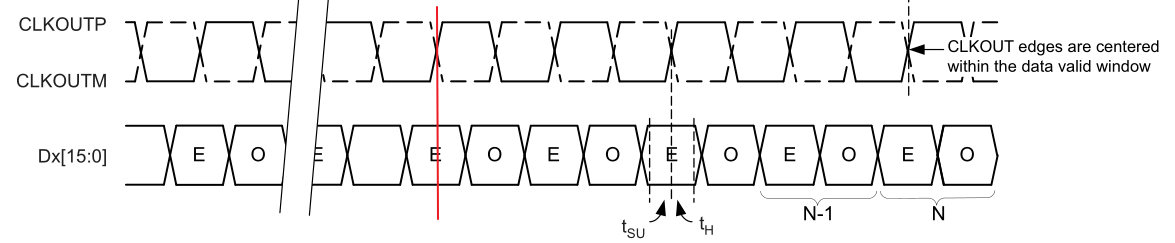

但其实这种想法是不对的,比如在很多ADC的设计中,输出的时钟的边沿刚好是数据的中心位置,而如果我们不加延迟约束,则Vivado会默认时钟和数据是对齐的。

对于输入管脚,首先判断捕获时钟是主时钟还是衍生时钟,如果是主时钟,直接用set_input_delay即可,如果是衍生时钟,要先创建虚拟时钟,然后再设置delay。对于输出管脚,判断有没有输出随路时钟,若有,则直接使用set_output_delay,若没有,则需要创建虚拟时钟。

在本工程中,输入输出数据管脚的捕获时钟如下表所示:

根据上表,我们创建的延迟约束如下,其中的具体数字在实际工程中要根据上下游器件的时序关系(在各个器件手册中可以找到)和PCB走线延迟来决定。未避免有些约束有歧义,我们把前面的所有约束也加进来。

# 主时钟约束 create_clock -period 25.000 -name clk2 [get_ports clk_in2] # 衍生时钟约束 create_generated_clock -name clk_samp -source [get_pins clk_gen_i0/clk_core_i0/clk_tx] -divide_by 32 [get_pins clk_gen_i0/BUFHCE_clk_samp_i0/O] create_generated_clock -name spi_clk -source [get_pins dac_spi_i0/out_ddr_flop_spi_clk_i0/ODDR_inst/C] -divide_by 1 -invert [get_ports spi_clk_pin] create_generated_clock -name clk_tx -source [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1] [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT1] create_generated_clock -name clk_rx -source [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1] [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT0] # 设置异步时钟 set_clock_groups -asynchronous -group [get_clocks clk_samp] -group [get_clocks clk2] # 延迟约束 create_clock -period 6.000 -name virtual_clock set_input_delay -clock [get_clocks -of_objects [get_ports clk_pin_p]] 0.000 [get_ports rxd_pin] set_input_delay -clock [get_clocks -of_objects [get_ports clk_pin_p]] -min -0.500 [get_ports rxd_pin] set_input_delay -clock virtual_clock -max 0.000 [get_ports lb_sel_pin] set_input_delay -clock virtual_clock -min -0.500 [get_ports lb_sel_pin] set_output_delay -clock virtual_clock -max 0.000 [get_ports {txd_pin {led_pins[*]}}] set_output_delay -clock virtual_clock -min -0.500 [get_ports {txd_pin {led_pins[*]}}] set_output_delay -clock spi_clk -max 1.000 [get_ports {spi_mosi_pin dac_cs_n_pin dac_clr_n_pin}] set_output_delay -clock spi_clk -min -1.000 [get_ports {spi_mosi_pin dac_cs_n_pin dac_clr_n_pin}]

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4417文章

23967浏览量

426192 -

adc

+关注

关注

100文章

7947浏览量

556905

发布评论请先 登录

相关推荐

热点推荐

07. 如何在Allegro中设置可以走线但不能铺的铜区域?| 芯巧Allegro PCB 设计小诀窍

背景介绍:我们在进行PCB设计时,经常需要绘制一些禁止铺铜但是允许走线的区域,如果我们直接使用Route Keepout绘制的话,虽然可以实现在此区域内禁止铺铜的效果,但是走

发表于 04-09 17:23

05. 如何在 Allegro 中沿着板子轮廓走线?| 芯巧Allegro PCB 设计小诀窍

背景介绍:在PCB设计过程中我们经常会遇到异形板框的设计要求,最常见的比如FPC设计、消费类控制板设计以及灯板设计等。在这些设计中通常会需要沿着板子轮廓进行走线,并且走线要与板框保持一

发表于 04-03 16:46

03. 如何把 PCB 板上的线变成铜皮?| 芯巧Allegro PCB 设计小诀窍

图形的描述是矢量的,而有很多软件对大块图形的描述是线性的,这就导致这类图形导入到Allegro PCB之后,图形是由一条条的线组成的,这时就需要把线构成的图形转换成Shape。另外,当我们PC

发表于 04-03 16:40

MCU 的 3.3V 电源线走线有没有问题?比如滤波电容的位置、走线长度这些是不是规范?

“各位大神好~我是 PCB 设计新手,第一次画板子,想请教下这个 MCU 的 3.3V 电源线走线有没有问题?比如滤波电容的位置、走线长度

发表于 01-05 21:30

PCB板双面布局的DDR表底走线居然不一样

越好,也就是下图所示的这几段走线。

这个客户还是比较的爱学习,除了硬件本身的知识外,还花很多时间去了解PCB设计的知识,也看了很多主流芯片的PCB设计指导书,对DDR设计包括高速设计

发表于 12-11 10:43

到底DDR走线能不能参考电源层啊?

高速先生成员--黄刚

一些通用的PCB设计经验以及高速信号理论,都告诉我们PCB上的信号最好都以地平面为参考,尤其是高速走线,建议上下参考平

发表于 11-11 17:46

别蒙我,PCB板上这几对高速走线怎么看我都觉得一样!

工程师说过孔这档子事了。那不说过孔说什么啊,就单纯的走线,正常走的话也不影响高速性能。Chris就喜欢杠,就打算在走线上挑挑刺!

你以为Chris装不了?废话不说了,直接上案例。各位

发表于 06-09 14:34

PCB上走线的延迟约束

PCB上走线的延迟约束

评论