Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为了快速掌握 Vivado 使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏 升级到 Vivado 的信心。

本文介绍了 Tcl 在 Vivado 中的基础应用,希望起到抛砖引玉的作用, 指引使用者在短时间内快速掌握相关技巧,更好地发挥 Vivado 在 FPGA 设计中的优势。

Tcl 的背景介绍和基础语法

Tcl(读作 tickle)诞生于 80 年代的加州大学伯克利分校,作为一种简单高效可移植性好的脚本语言,目前已经广泛应用在几乎所有的 EDA 工具中。Tcl 的最大特点就是其语法格式极其简单甚至可以说僵化,采用纯粹的 [命令选项 参数] 形式,是名副其实的“工具命令语言”(即 Tcl 的全称 Tool Command Language)。

实际上 Tcl 的功能可以很强大,用其编写的程序也可以很复杂,但要在 Vivado 或大部分其它 EDA 工具中使用,则只需掌握其中最基本的几个部分。

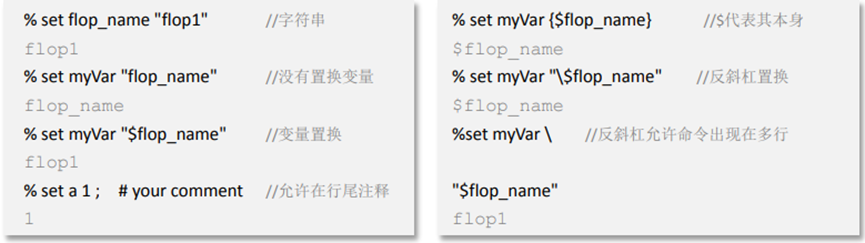

注:在以下示例中,% 表示 Tcl 的命令提示符,执行回车后,Tcl 会在下一行输出命令执行结果。 // 后是作者所加注释,并不是例子的一部分。

打印主要通过 puts 语句来执行,配合特殊符号,直接决定最终输出内容。

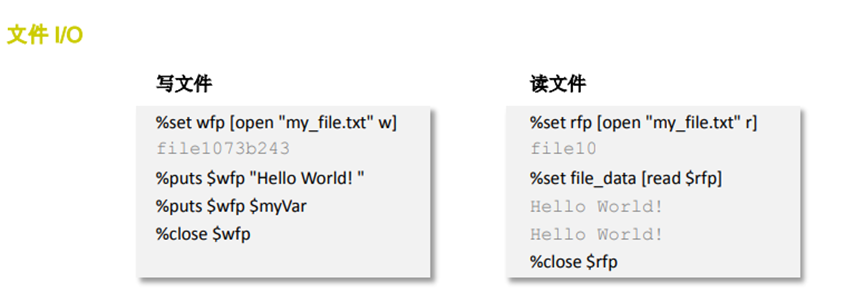

可以看到 Tcl 对文件的操作也是通过设置变量,改变属性以及打印命令来进行的。上述写文件的例子中通过 puts 命令在 my_file.txt 文件中写入两行文字,分别为“Hello World!” 和 myVar 变量的值,然后在读文件操作 中读取同一文件的内容。

控制流和循环命令

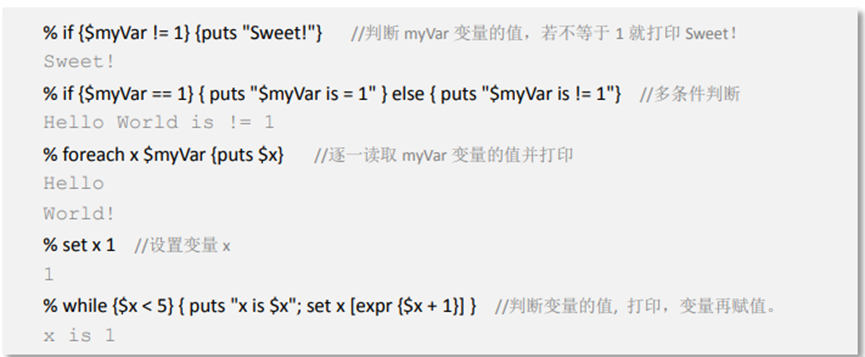

Tcl 语言中用于控制流程和循环的命令与 C 语言及其它高级语言中相似,包括 if、while、for 和 foreach 等等。

具体使用可以参考如下示例,

子程序/过程

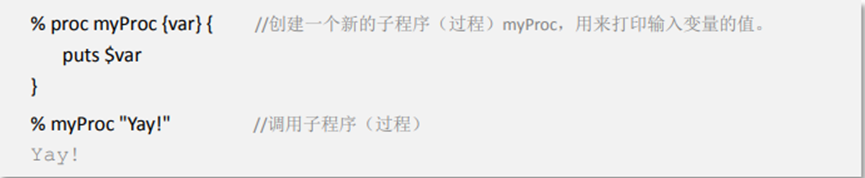

Tcl 中的子程序也叫做过程(Procedures),Tcl 正是通过创建新的过程来增强其内建命令的能力,提供更强的扩展性。具体到 Vivado 的使用中,用户经常可以通过对一个个子程序/过程的创建来扩展或个性化 Vivado 的使用流程。

一些特殊符号

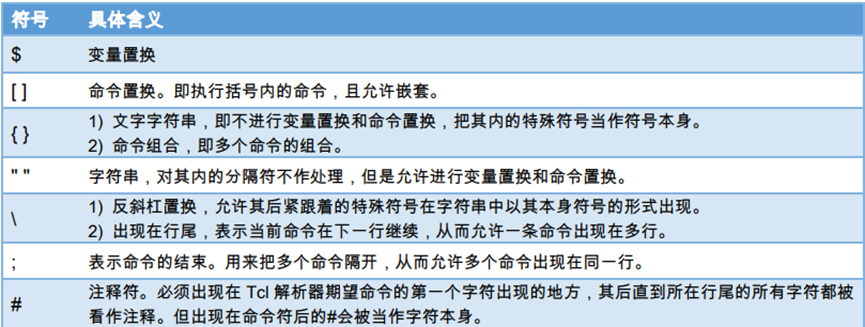

注: 反斜杠出现在行尾以允许命令在下一行继续时,必须是这一行的最后一个字符,其后不能有空格。

Tcl 语言的基本语法相对简单,但要熟练掌握仍需日常不断练习。Xilinx 网站上有很多相关资料,这里推荐 两个跟 Tcl 相关的文档 UG835 和 UG894 ,希望对大家学习 Vivado 和 Tcl 有所帮助。

在Vivado 中使用 Tcl定位目标

在 Vivado 中使用 Tcl 最基本的场景就是对网表上的目标进行遍历、查找和定位,这也是对网表上的目标进行约束的基础。要掌握这些则首先需要理解 Vivado 对目标的分类。

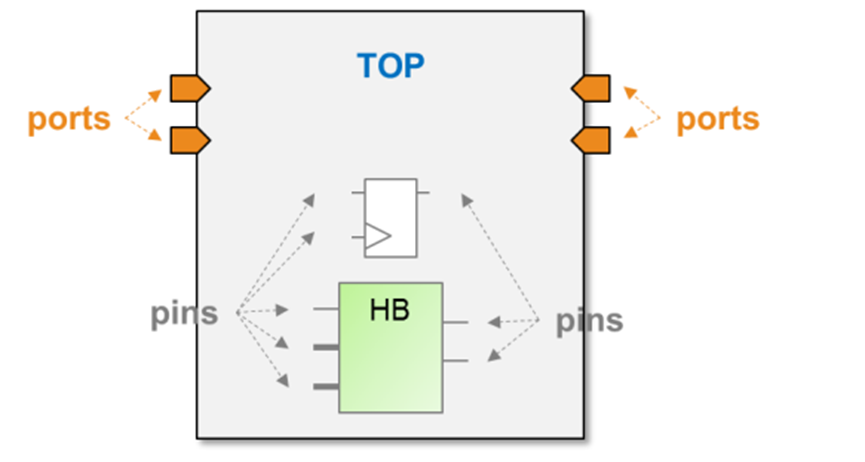

目标的定义和定位

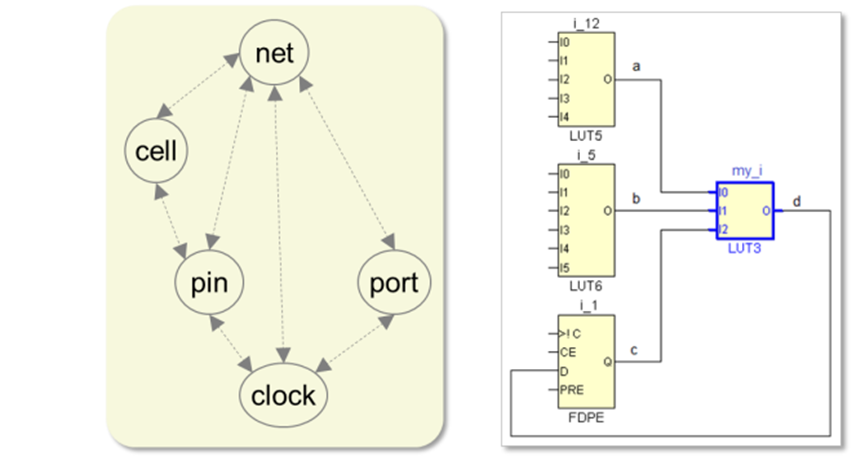

如上图所示,设计顶层的 I/O 称作 ports,其余底层模块或是门级网表上的元件端口都称作 pins。而包括顶层在内的各级模块,blackbox 以及门级元件,都称作 cells。连线称作 nets,加上 XDC 中定义的 clocks,在 Vivado 中一共将网表文件中的目标定义为五类。要选取这五类目标,则需用相应的 get_*命令,例如 get_pins 等等。

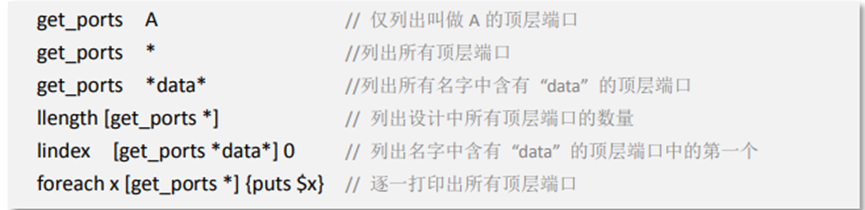

get_ports

ports 仅指顶层端口,所以get_ports 的使用相对简单,可以配合通配符“* ”以及 Tcl 语言中处理 list 的命令一起使用。如下所示,

get_cells/get_nets

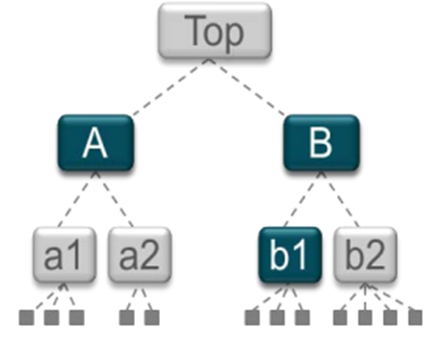

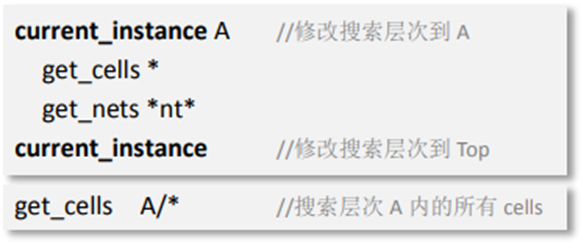

不同于 ports 仅指顶层端口,要定位 cells 和 nets 则相对复杂,首先需要面对层次的问题。这里有个大背景需要明确:Vivado 中 Tcl/XDC 对网表中目标的搜索是层次化的,也就是一次仅搜索一个指定的层次 current_instance,缺省值为顶层。

以右图所示设计来举例,若要搜索 A(不含 a1,a2)层次内的所有 cells 和名字中含有 nt 的 nets,有两种方法:

若要将搜索层次改为 A+B+b1,则可以写一个循环,逐一用 current_instance 将搜索层次指向 A,B 和 b1,再将搜索到的 cells 或 nets 合成一个 list 输出即可。

若要将搜索层次改为当前层次以及其下所有子层次,可以使用 -hierarchical (在 Tcl 中可以简写为-hier)

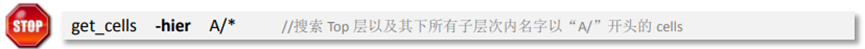

在使用-hierarchical 时有一点需要特别留意,即后面所跟的搜索条件仅指目标对象的名字,不能含有代表 层次的“/” 。下面列出的写法便是一种常见的使用误区,并不能以此搜索到 A 及其下子层次内所有的 cells。

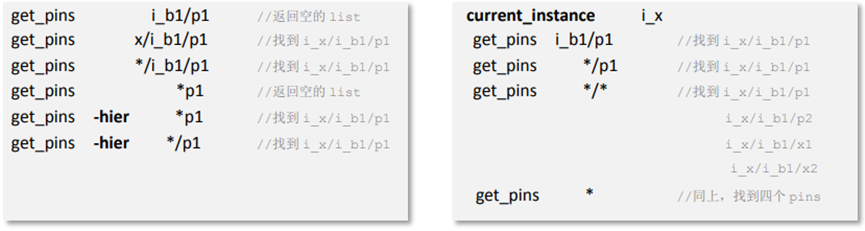

get_pins

pins 在 Vivado 数据库中有个独特的存在形式,即 / 。这里的“ / ”不表示层次,而是其名字的一部分,表示这个 pin 所属的实体。也就是说,在使用 get_pins 配合-hier 来查找 pins 时,“ / ”可以作为名字的一部分,出现在搜索条件内(注意与上述 get_cells 和 get_nets 的使用区别)

目标之间的关系

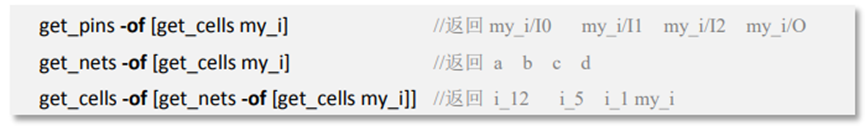

Tcl 在搜索网表中的目标时,除了上述根据名字条件直接搜索的方式,还可以利用目标间的关系,使用 -of_objects(在 Tcl 中可以简写为-of)来间接搜索特定目标。Vivado 中定义的五类目标间的关系如下页左图所示。

以上示右图的设计来举例,

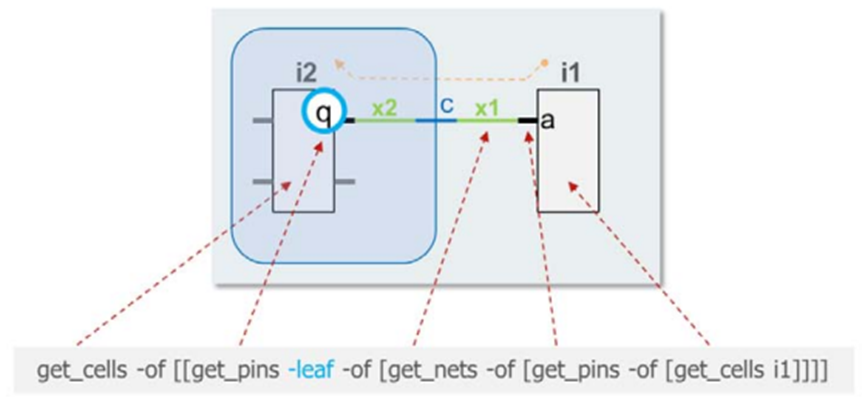

下图是一个更复杂的示例,涉及跨层次搜索。可以看到在 get_pins 时,要加上-leaf 才能准确定位到门级 元件(或 blackbox)的端口 q。另外,在实际操作中,使用get_nets 和 get_pins 时,需要视情况而加上其它 条件(-filter)才能准确找到下述例子中的 cells (i2) 。

高级查找功能

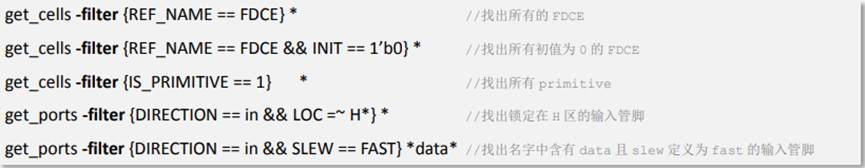

在使用 get_*命令查找网表中的目标时,除了名字这一直接条件,往往还需要辅以其它更复杂的条件判断,这就需要用到高级查找功能:-filter 结合 Tcl 支持的各种关系和逻辑运算符(==, !=, =~, !~, <=, >=, >,

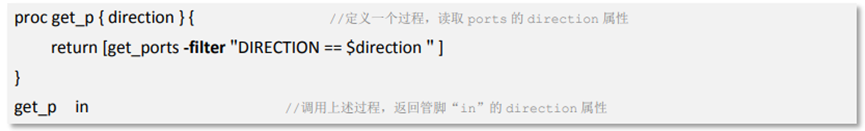

在创建子程序时也常常用到-filter,例如下述 get_p 的子程序/过程就可以用来返回指定管脚的方向属性,告诉用户这是一个输入管脚还是一个输出管脚。需要特别指出的是,通常在-filter 后会使用{ },但此时需要对 $direction 做变量替换,必须如下所示改用" " 。

Tcl 在 Vivado 中的延伸应用

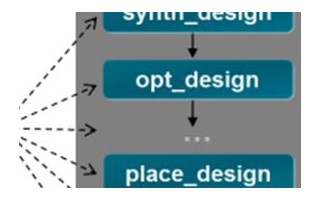

Tcl 在 Vivado 中的应用还远不止上述所列,其它常用的功能包括使用预先写好的 Tcl 脚本来跑设计实现流程,创建高级约束(XDC 不支持循环等高级 Tcl 语法)以及实现复杂的个性化设计流程等等。Tcl 所带来的强大的可扩展性决定了其在版本控制、设计自动化流程等方面具有图形化界面不能比拟的优势。

Vivado 在不断发展更新的过程中,还有很多新的功能,包括 ECO、PR、HD Flow 等等都是从 Tcl 脚本方 式开始支持,然后再逐步放入图形化界面中实现。这也解释了为何高端 FPGA 用户和熟练的 Vivado 用户都更 偏爱 Tcl 脚本。

篇幅所限,不能一一展开。关于以上 Tcl 在 Vivado 中的延伸应用,敬请关注 Xilinx 官方网站和中文论坛 上的更多技术文章。

-

FPGA

+关注

关注

1655文章

22281浏览量

630050 -

Xilinx

+关注

关注

73文章

2192浏览量

129880 -

eda

+关注

关注

72文章

3053浏览量

181461 -

脚本

+关注

关注

1文章

407浏览量

29050 -

Vivado

+关注

关注

19文章

846浏览量

70454

原文标题:Tcl在Vivado中的应用

文章出处:【微信号:FPGA算法工程师,微信公众号:FPGA算法工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Tcl在Vivado中的基础应用

用 TCL 定制 Vivado 设计实现流程

在Vivado下利用Tcl脚本对综合后的网表进行编辑过程

Tcl在Vivado中的基础应用

Tcl在Vivado中的应用

Tcl在Vivado中的应用

评论