在FPGA的时序约束中,主时钟约束是第一步就要做的,主时钟通常有两种情形:一种是时钟由外部时钟源提供,通过时钟引脚进入FPGA,该时钟引脚绑定的时钟为主时钟:另一种是高速收发器(GT)的时钟RXOUTCLK或TXOUTCLK。对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

对于进入到IP Core(比如MMCM)的主时钟,只有我们在IP Core中指定了时钟频率,那么Vivado会自动产生一个约束文件来约束该输入的主时钟。

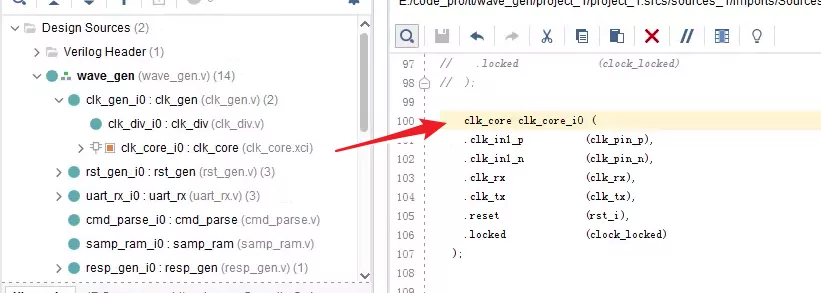

我们以Vivado自带的wave_gen工程为例,该工程中输入一对差分的时钟信号,进入到MMCM中,我们无需再对这个主时钟添加约束。

可以看到,综合后这个时钟已经被约束了:

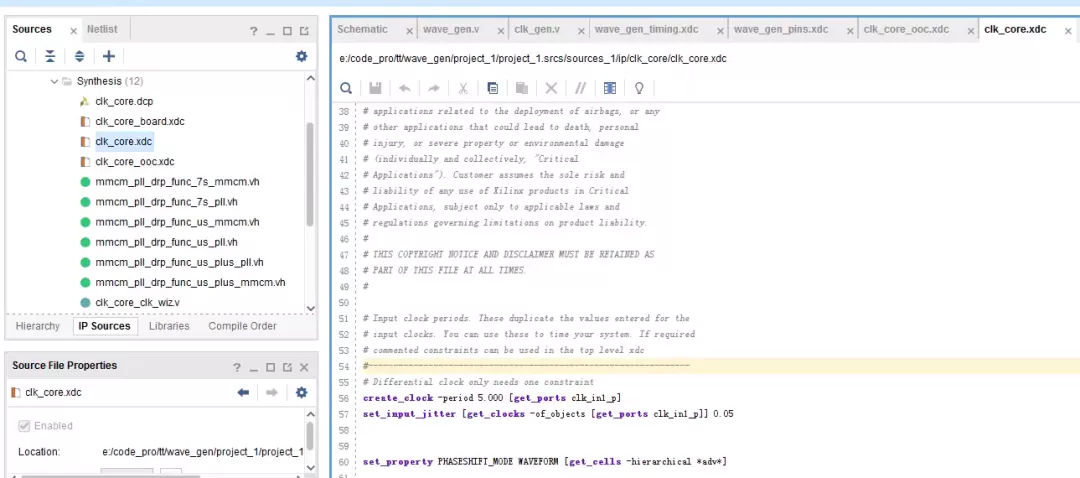

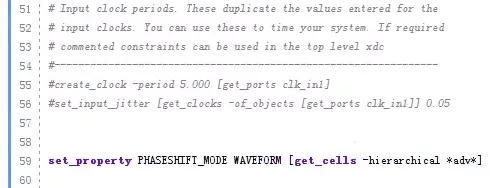

这是因为该ip生成的xdc文件中,已经包含了对这个主时钟的约束,如下图:

所以很多同学可能误以为只要是进了IP Core的主时钟,都不需要再手动添加约束了。

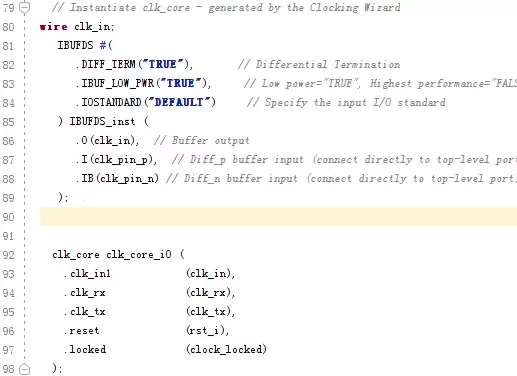

但如果收入的差分时钟先经过了IBUFDS,然后再以单独的形式进入了MMCM:

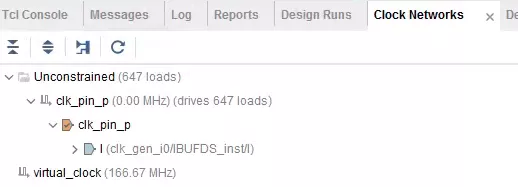

综合后,可以看到该时钟是没有被约束的:

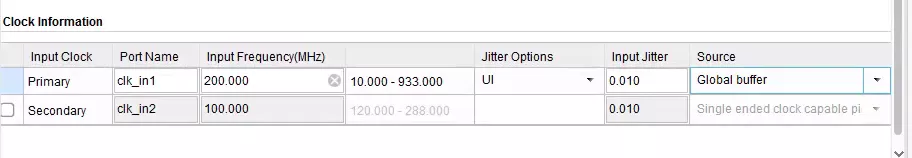

此时由于输入时钟并非来自管脚,所以Source选择为Global Buffer

再看刚刚的clk_core.xdc文件,已经没有产生主时钟的约束了:

为什么会没有这个约束了呢?因为输入的时钟并非来自管脚,IP Core并不知道从哪个pin输入的,所以就无法添加主时钟的约束,此时就需要我们再手动添加约束。

审核编辑:符乾江

-

FPGA

+关注

关注

1664文章

22502浏览量

639054 -

Vivado

+关注

关注

19文章

860浏览量

71392

发布评论请先 登录

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

系统c盘满了怎么清理不需要文件

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

E203移植genesys2(差分时钟板)生成比特流文件全过程

采用xc7a200开发板移植蜂鸟E203

时序约束问题的解决办法

关于综合保持时间约束不满足的问题

如何判断电能质量在线监测装置时钟模块需要进行手动校准?

光纤线需不需要套管

使用stm32u575rg通过spi读取外置adc的数据,如何设置才能让spi不需要中断重启持续读取数据?

FPGA时序约束之设置时钟组

进入IP Core的时钟,都不需要再手动添加约束吗

进入IP Core的时钟,都不需要再手动添加约束吗

评论