约束主时钟

在这一节开讲之前,我们先把wave_gen工程的wave_gen_timing.xdc中的内容都删掉,即先看下在没有任何时序约束的情况下会综合出什么结果?

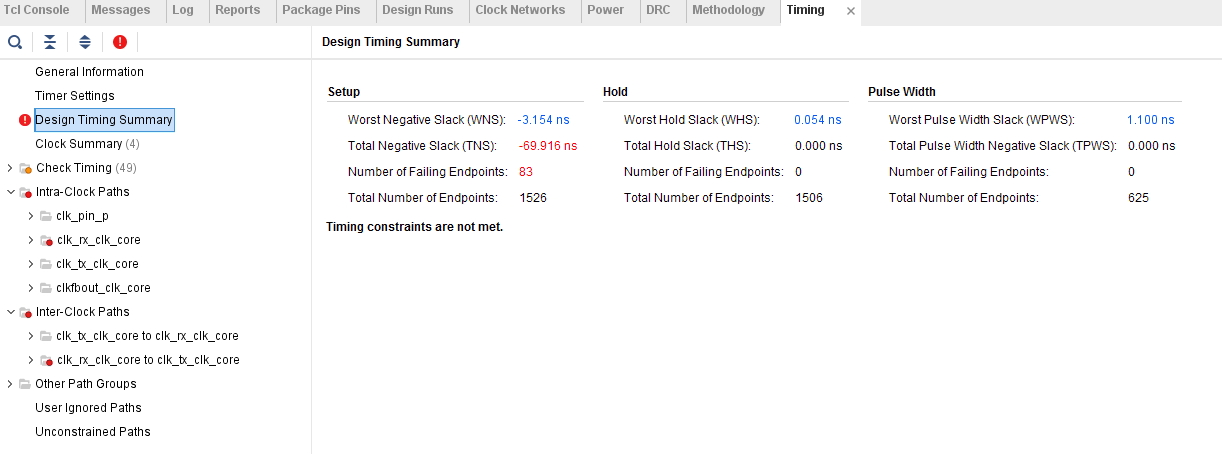

对工程综合并Implementation后,Open Implemented Design,会看到下图所示内容。

可以看到,时序并未收敛。可能到这里有的同学就会有疑问,我们都已经把时序约束的内容都删了,按我们第一讲中提到的“因此如果我们不加时序约束,软件是无法得知我们的时钟周期是多少,PAR后的结果是不会提示时序警告的”,这是因为在该工程中,用了一个MMCM,并在里面设置了输入信号频率,因此这个时钟软件会自动加上约束。

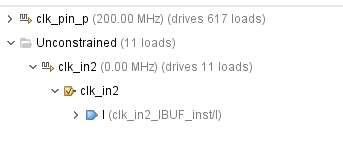

接下来,我们在tcl命令行中输入report_clock_networks -name main,显示如下:

可以看出,Vivado会自动设别出两个主时钟,其中clk_pin_p是200MHz,这个是直接输入到了MMCM中,因此会自动约束;另一个输入时钟clk_in2没有约束,需要我们手动进行约束。

或者可以使用check_timing -override_defaults no_clock指令,这个指令我们之前的内容讲过,这里不再重复讲了。

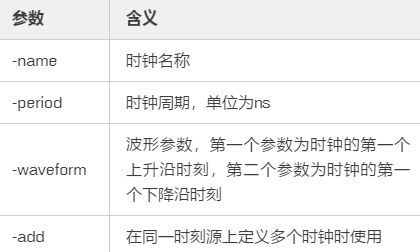

在tcl中输入

create_clock -name clk2 -period 25 [get_ports clk_in2]

注:在Vivado中,可以直接通过tcl直接运行时序约束脚本,运行后Vivado会自动把这些约束加入到xdc文件中。

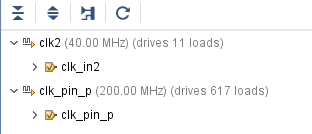

再执行report_clock_networks -name main,显示如下:

可以看到,主时钟都已被正确约束。

编辑:hfy

-

FPGA

+关注

关注

1664文章

22502浏览量

639061 -

TCL

+关注

关注

11文章

1815浏览量

91797 -

Vivado

+关注

关注

19文章

860浏览量

71394 -

时钟约束

+关注

关注

0文章

15浏览量

6224

发布评论请先 登录

FPGA案例解析:针对源同步的时序约束

FPGA主时钟约束详解 Vivado添加时序约束方法

FPGA时序约束之衍生时钟约束和时钟分组约束

FPGA时钟约束问题

FPGA时序约束的原理是什么?

FPGA时序约束之设置时钟组

FPGA之主时钟约束解析

FPGA之主时钟约束解析

评论