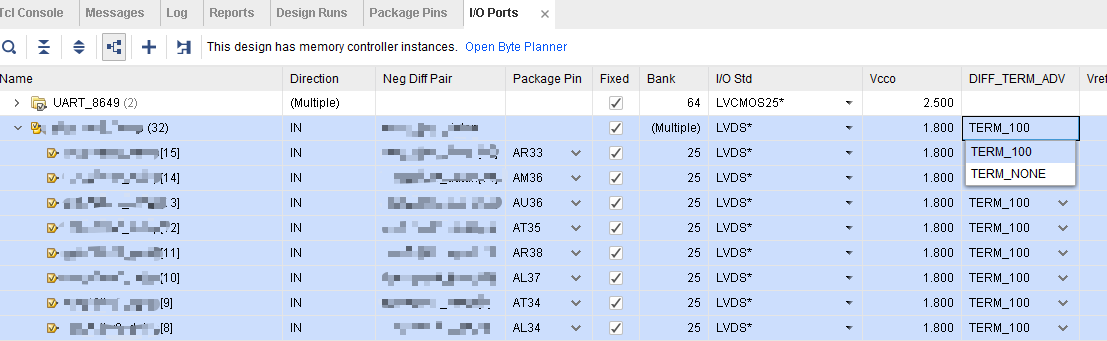

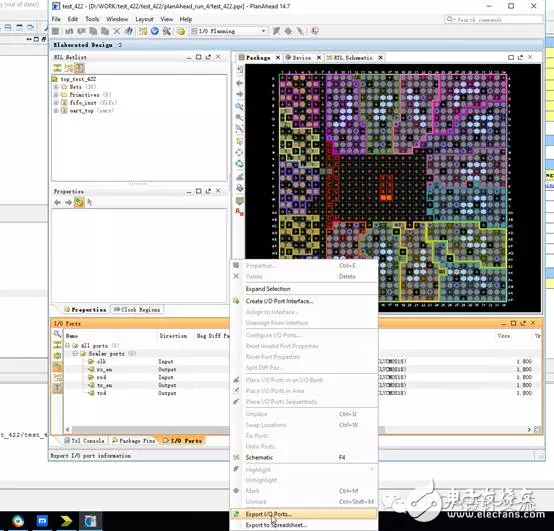

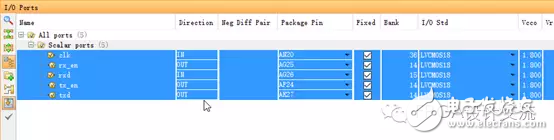

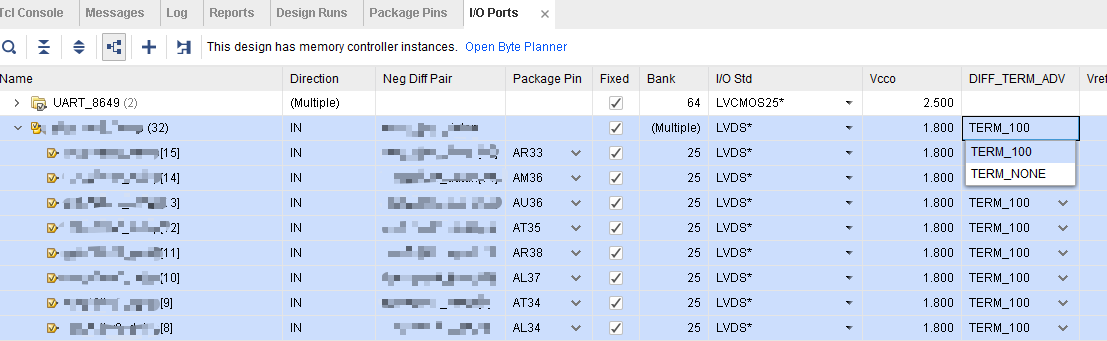

,后者指定了管脚对应的电平标准。 在vivado中,使用如下方式在xdc中对管脚进行约束。 set_property -dict {PACKAGE_PIN AJ16 IOSTANDARD

2020-10-30 16:08:13 17476

17476

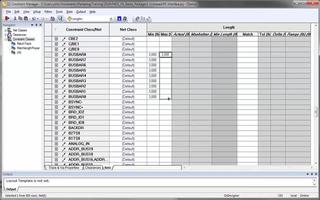

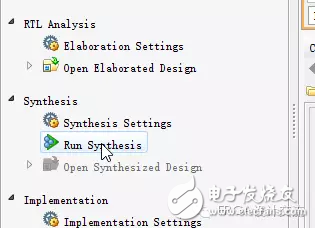

时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 11063

11063 Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-14 09:09:56 2515

2515 移动互联网的下一个春天,真的来临了

2023-11-14 23:06:44 1840

1840

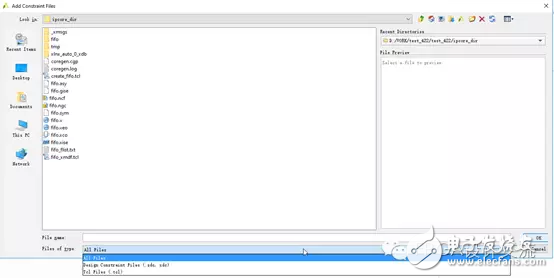

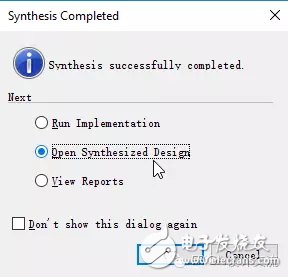

Vivado的时序约束是保存在xdc文件中,添加或创建设计的工程源文件后,需要创建xdc文件设置时序约束。时序约束文件可以直接创建或添加已存在的约束文件,创建约束文件有两种方式:Constraints Wizard和Edit Timing Constraints,在综合后或实现后都可以进行创建。

2025-03-24 09:44:17 4561

4561

14.4 ise vivado license

2013-03-25 21:22:03

我下载ISE 14.7嵌入式许可证的网站,因为它已经被要求知道这是购买Vivado的一部分许可证包含ISE许可证。问候!以上来自于谷歌翻译以下为原文We just bought a Vivado

2018-12-17 11:52:33

嗨,我们为Vivado 14.2购买了激活基础许可证。我从xilinx网站下载它,并通过VivadoManege License.Bu将它设置到我的电脑。现在我想使用ISE Design Suite

2018-12-05 11:08:35

嗨,我可以买一台新的PC进行开发。使用两个工具链,ISE(V6)和VIVADO(ZYNQ)。我的问题是,哪个系统会更快(只有性能,而不是价格):i7-7700K+ 4.2-4.5 GHz -4个核心

2019-04-19 06:28:07

有没有哪位大神对ISE的时序约束比较熟悉,尤其是多周期约束这一块。在Quartus中使用比较简单,而且相关资料也比较多,但是ISE中的资料好像不是那么多,而且也没有针对具体例子进行分析。官网上给出

2015-04-30 09:52:05

在我的所有尝试中,下载Vivado 2013.4所有操作系统完整安装程序以及Windows完整安装程序都带有错误的校验和。在几次尝试中,Windows的ISE 14.7full安装程序的下载都带有

2018-12-07 11:11:52

。 [ “d:/ VIVADO_PRJ /.../ constrs_1 /新/ timing.xdc”:6][约束18-472] set_input_delay:list不包含约束支持的任何类型的对象(输入

2020-04-27 09:11:58

不支持更老的设备(Spartan, Virtex-6 以及之前的 FPGA) 。同样 ,ISE 也不再支持 7 系列之后的设备ISE 和 Vivado 之间另一个重要的区别就是约束文件的类型。在 ISE

2021-01-08 17:07:20

你好,我是ZYBO Zynq 7000开发板的新手,通常也是FPGA的世界。1)我即将安装我的开发程序(ISE / Vivado)。如何区分它们以便为我的工作选择合适的一个。考虑到我已经尝试了这两种

2018-12-21 11:07:03

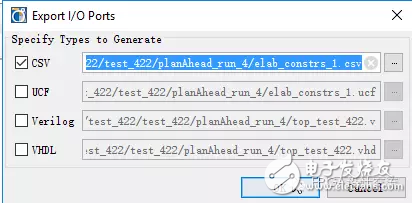

回到ISE, 我们可以做的一件事是路由设计,然后为设计生成约束文件,过去对这些较小的部件有用,看看工具如何连接引脚,给出了一个起点,我怎么在Vivado做这个?在vhdl / ip块中输入设计,模拟

2018-10-22 11:19:29

出于某种原因,Vivado忽略了我的约束文件,当我尝试在tcl控制台中逐个输入约束时,我尝试分配的每个端口都会出现以下错误:set_property PACKAGE_PIN T19

2018-11-06 11:36:22

使用Vivado 2015.4我生成了两个FIFO和一个Aurora Core。我收到与Vivado自动生成的时序约束相关的严重警告。由于我的FIFO在整个设计中被多次使用,我需要一种让Vivado

2018-11-02 11:30:10

你好Vivado的PR许可证是否与ISE不同?假设用于ISE的许可证也可用于Vivado?以上来自于谷歌翻译以下为原文Hi Does PR licence for vivado

2018-12-11 11:19:28

我的板子是6系列,vivado不支持,偶然间听说有个ise的界面与vivado差不多,想问一下是哪个版本,方便下载,谢谢啦!

2018-09-25 09:53:54

我的板子是6系列,vivado不支持,偶然间听说有个ISE界面和vivado一样,问一下这个版本叫什么,好去搜素下载,谢谢!

2018-09-25 09:39:37

vivado导入其他版本的项目的时候,IP核被锁,无法解开,请问该如何解决。

使用软件:vivado 2019.2

导入项目使用版本:vivado 2018

2024-11-08 21:29:58

(约束指令介绍)UG904 - Vivado Design Suite User Guide -Implementation UG906- Vivado Design Suite User Guide

2018-09-26 15:35:59

使用:System Generator,EDK和ISE设计新东西(或者Vivado,BTW:我可以使用Vivado吗?我看到它被说明在AR#51081中是不可能的,但我想知道自那以后是否有所改变2012年

2019-07-26 13:47:37

大家好,我是ISE,FPGA和VHDL的新手。我正在使用Mercury Nova FPGA板(Spartan 3a)。我正在运行Gentoo Linux(我知道是不支持的)。当我创建一个项目时,似乎

2020-03-09 08:43:49

在Vivado 2016.1和Kintex-7 FPGA中,我可以使用名为“Clocking Wizard v5.3”的IP来配置为我的项目输出系统时钟的MMCM。自定义此IP后,将自动为IP生成约束

2019-08-02 09:54:40

我现在运行了几个项目我观察到安装了程序Xilinx ISE和Vivado的目录高达50 GB,因为我想在运行项目期间生成的文件。我不记得一开始是不是那么多。请告诉我哪些可以删除的“运行时”文件以及

2018-12-20 11:20:46

Xilinx工具:vivado在该图中,TX_CLK_i连接到pll_x1模块的输入时钟。然后,pll_x1的输出时钟连接到ODDR。接下来,ODDR的输出引脚将连接到I / O引脚

2020-05-04 08:04:41

先生我想将我的system.xmp文件(嵌入式处理器)从ise 14.7迁移到vivado 2014.4。我尝试了很多但失败了。请指导我..shweta空间应用中心艾哈迈达巴德感谢

2018-10-26 15:09:29

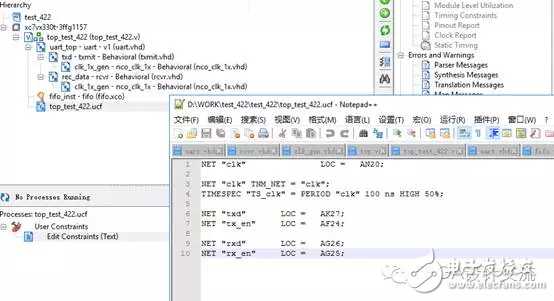

原理图实现的顶层模块为例),如图 3-55 所示。单击 Next 按钮,再单击Finish 按钮就完成了约束文件的创建。(2)对约束文件进行编辑。ISE 中有 3 种工具可以编辑约束文件,即

2018-09-29 09:18:05

我使用vivado 2016.我在warp v3板上做项目,因为我不能使用vivado。但是我有ise webpack13.4,这对于没有付费许可证使用warpboard的所有功能都没用,所以可以

2018-12-26 11:29:07

我的PC上安装了ISE Design Suite 14.7和Vivado 2016.4。(我保持安装ISE Design Suite 14.7,因为这是我的Spartan-6产品的开发平台

2018-12-27 10:55:34

我有两张标有“Vivado Design Suite 2013.2”和“ISE Design Suite 14.6”的光盘,我之前在Virtex-5设计上使用过Win7。最近将操作系统

2018-12-29 13:53:01

嗨,专家我以前在Windows下设计,最近我搬到了linux。是否有关于如何使用脚本运行ISE / VIVADO的指南,例如Perl的?谢谢。克里斯以上来自于谷歌翻译以下为原文Hi, experts

2019-02-19 10:59:18

在一个愚蠢的举动中,我为ise webpack创建了一个许可证并将其加载到我的机器上。但是,最终我真的想加载vivado的webpack许可证。我可以删除许可证(Xilinx.lic)文件等,但是

2018-12-13 10:23:01

你好我有一个新的vc707板。我可以将旧的ISE设计转移到Vivado 2014.1。使用Vivado,我可以通过USB电缆将我的比特流下载到电路板上,没有任何问题。但是当我尝试使用Vivado将我

2020-05-29 10:43:03

无法使用基于ISE的策略运行综合和实施,或导入ngc网表。请设置XILINX环境以获得完整功能。source run_ippack.tcl -notrace确实在我打开vivado并添加我的IP并完成我

2020-04-03 08:48:23

我想知道是否可以将Vivado项目转换为ISE项目,以便将其导入HDL Designer。 HDL设计师确实有Vivado流,但不是Vivado导入。或者,如果有人知道将vivado项目导入HDL

2018-12-20 11:24:10

大家好,使用UCF文件中的ISE,我习惯于在输入焊盘和第一个触发器之间的信号上设置maxdelay约束,特别是在总线信号上,以确保总线的所有信号具有大致相同的传播时间。使用Vivado,我无法在

2018-10-25 15:17:18

嗨, 我想知道是否有像ISE一样的vivado中的任何测试平台。在ISE中点击添加源我们得到vhd testbech module.but在vivado我们将如何创建测试平台

2020-03-19 09:43:58

尝试使用vivado .lic文件进行编译时,我收到许可错误。我看到有关在ISE上使用vivado设计套件版本的相互矛盾的信息。我有一个涉及斯巴达6芯片的项目。我购买了许可证,但似乎没有与ISE合作

2018-12-27 10:57:37

使用xdc文件进行管脚、位置、时序和属性等约束的时候,经常会使用各种get命令。Vivado提供了很丰富的匹配表达式,比如等于==、不等于!=、匹配=~、不匹配!~、《、》、《=、》=等等,这些

2021-01-26 07:03:16

时,老是范糊涂,因为Quartus II和ISE对IO端口的约束方式和计算公式略有不同,容易混淆。而老掉牙的ISE中也只是光秃秃的没有任何提示,Vivado可好了,出现了标好了具体约束值的时序图

2016-01-11 16:55:48

最近在学习FPGA,因为Xilinx家的芯片国内用的最多,故使用了XC6SLX16。但在安装Xilinx ISE时发现无法导入license,网络上寻找了下方法,实测可行,故在这分享给大家。以下

2021-05-17 08:00:00

Xilinx ISE Design Suite 12.3器件是XC5VLX220管脚约束文件这句话出错:NET "cina[0]"LOC = "G17"

2017-09-23 09:53:38

这个板子一开始约束的就是6路差分输入的,然后我想在AD9361中让6路差分输入转为12路单端,在ISE平台上实现,其中的差分CLK可以通过IBUFDS转换,而多位的数据我就不知道用什么转换了,请大神们指导一下,谢谢

2018-07-31 06:20:14

我发现vivado可以改变工具中的featuresaboutSynthesis - settings - Synthesis。但我在ISE中找不到类似的东西。如果有人知道设置在哪里。非常感谢你!

2019-08-12 10:13:33

嗨,我刚刚获得了一个完整的Vivado许可证,据我所知,其中包括对所有ISE设计套件的完全许可(需要使用ISE 14.6)我似乎无法在产品许可页面中找到ISE设计套件的基于证书的许可证。我的帐户中

2018-12-11 11:27:37

FPGACPLD设计工具——Xilinx ISE使用详解的主要内容:第1章 ISE系统简介第2章 工程管理器与设计输入工具第3章 ModelSim仿真工具第4章 ISE中集成的综合工具第5章 约束第6章

2009-07-24 16:06:58 198

198 ISE时序约束:What effects do timing constraints have on your project?• The implementation tools do

2010-01-11 08:54:06 87

87 赛灵思(Xilinx)公司宣布推出全新的Vivado设计套件。Xilinx全球高级副总裁汤立人表示,Vivado不是已有15年历史的ISE设计套件的再升级(ISE采用的是当时极富创新性的基于时序的布局布线引

2012-06-19 17:50:14 1054

1054 作者: 圆宵 FPGA那点事儿 在ISE时代,使用的是UCF约束文件。从Vivado开始,XDC成了唯一支持的约束标准。XDC除了遵循工业界的通行标准SDC(Synopsys Design

2017-02-08 02:10:50 5835

5835 By Adam Taylor 在之前的博客中介绍了Vivado的基本时序约束,时序约束定义了系统频率或自己所定义的时钟频率。为建立良好的时序约束,下一步是需要建立时钟路径之间关系的定义。这样

2017-02-08 03:46:35 357

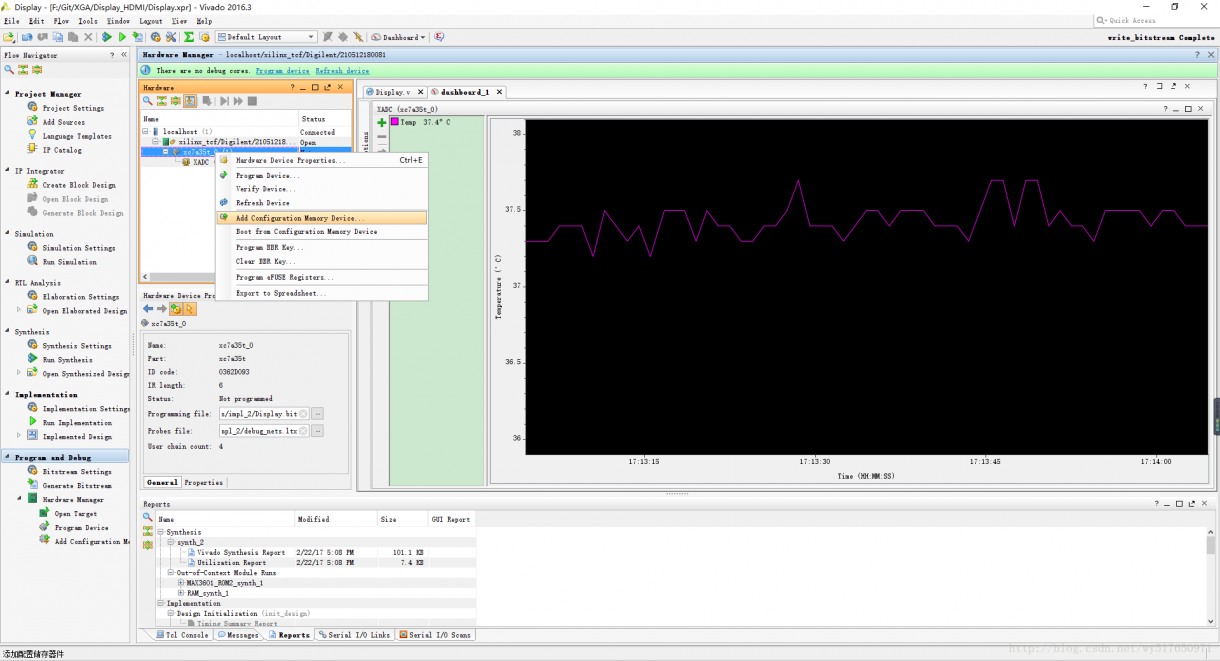

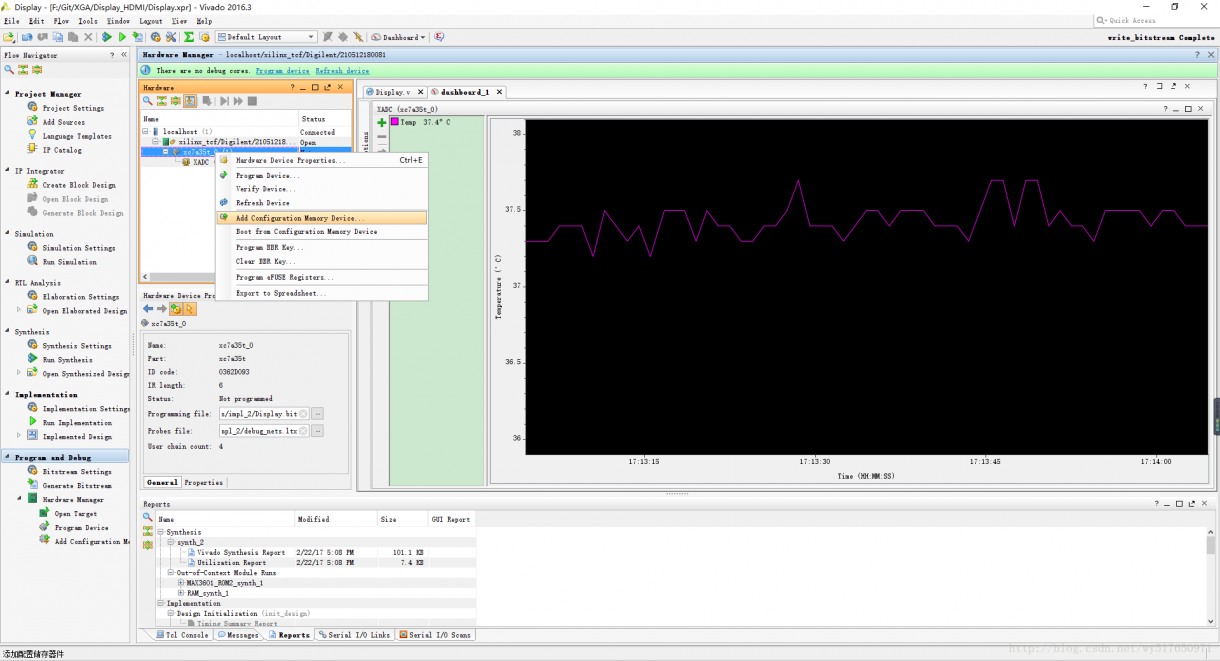

357 很多客户用过ISE中的MB,最近大家都开始玩7系列和VIVADO,如果依然需要MB,如何配置冷启动呢?VIVADO和ISE在MB配置过程有一些区别的。 step如下: A. 使用SDK已经完成

2017-02-08 05:46:11 726

726

在Vivado中通过set_clock_groups来约束不同的时钟组,它有三个选项分别是-asynchronous,-logically_exclusive

2017-02-08 08:39:49 1357

1357

这段时间在使用Xilinx公司的7系列FPGA,调试一款TI公司的高速ADC。鉴于目前Xilinx已经停止了对ISE开发组件的维护更新,所以果断将开发环境转到Vivado上来。 众所周知,ADC调试

2017-02-08 15:29:36 3412

3412 这段时间在使用Xilinx公司的7系列FPGA,调试一款TI公司的高速ADC。鉴于目前Xilinx已经停止了对ISE开发组件的维护更新,所以果断将开发环境转到Vivado上来。 众所周知,ADC调试

2017-02-09 01:43:06 2548

2548 时序约束可以使得布线的成功率的提高,减少ISE布局布线时间。这时候用到的全局约束就有周期约束和偏移约束。周期约束就是根据时钟频率的不同划分为不同的时钟域,添加各自周期约束。对于模块的输入输出端口添加

2017-02-09 02:56:06 918

918 《XDC约束技巧》系列中讨论了XDC约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入Vivado中的XDC实际上就是用户设定的目标 ,Vivado对FPGA设计的实现

2017-11-17 18:03:55 39395

39395

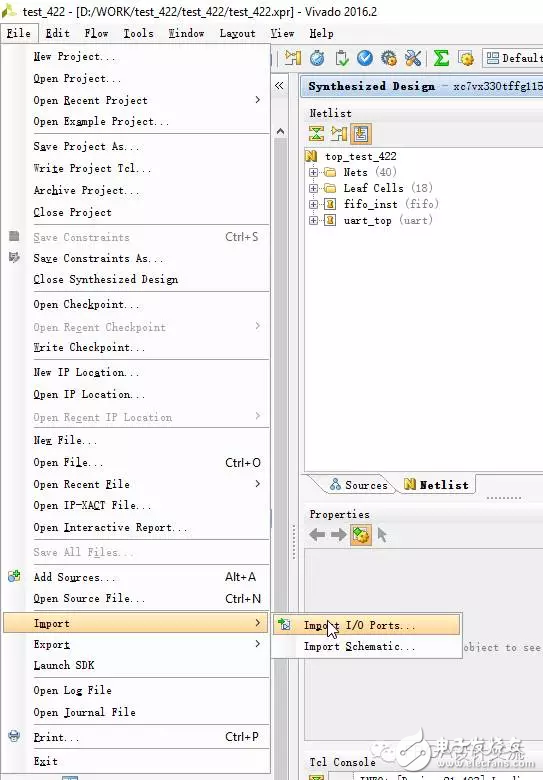

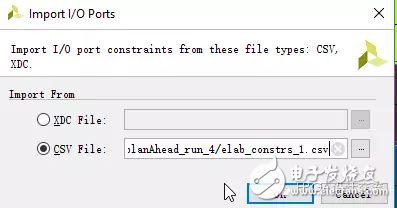

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握

2017-11-18 03:52:01 5363

5363

Xilinx©的新一代设计套件 Vivado 中引入了全新的约束文件 XDC,在很多规则和技巧上都跟上一代产品 ISE 中支持的 UCF 大不相同,给使用者带来许多额外挑战。Xilinx 工具专家

2017-11-18 03:59:01 4098

4098 本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。 Xilinx定义了如下几种约束类型

2017-11-24 19:59:29 4435

4435

摘要:本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。 Xilinx定义了如下几种约束类型

2017-11-25 01:27:02 7029

7029

一般来讲,添加约束的原则为先附加全局约束,再补充局部约束,而且局部约束比较宽松。其目的是在可能的地方尽量放松约束,提高布线成功概率,减少ISE 布局布线时间。典型的全局约束包括周期约束和偏移约束

2017-11-25 09:14:46 3015

3015 设计能否满足时序。主要涉及到xilinx vivado xdc约束语法,给出对应的ISE ucf 语法。另外quatus的语法和xdc几乎兼容,原理都一样。

2018-06-25 09:14:00 7199

7199 维持吗? 1、Vivado基本操作流程 2、时序基本概念 3、时序基本约束和流程 4、Baselining时序约束 5、CDC时序约束 6、I/O时序 7、例外时序约束 8、时序收敛优化技术

2018-08-06 15:08:02 722

722 该视频快速概述了ISE和Vivado中可用的XADC向导中的界面,功能和功能。

对于希望实例化基本设计的数字设计人员来说,这是一个很好的工具。

2018-11-20 06:19:00 5308

5308 了解如何将Altera的SDC约束转换为Xilinx XDC约束,以及需要更改或修改哪些约束以使Altera的约束适用于Vivado设计软件。

2018-11-27 07:17:00 5883

5883 了解如何轻松快捷地在设计周期中随时完成一次性设计约束的导入,并且有信心自己的产品设计全程完全遵守这些约束。

2019-05-21 06:00:00 1800

1800

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够

2020-01-28 17:34:00 4750

4750

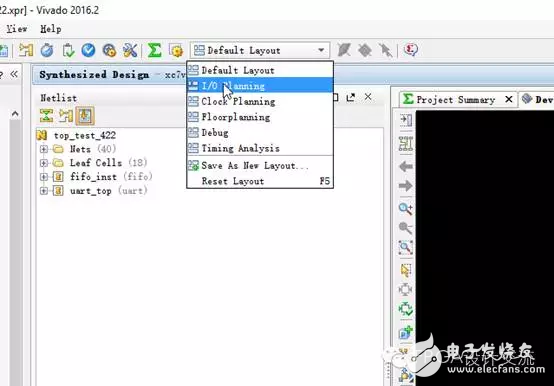

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

2020-03-08 17:17:00 20443

20443

Vivado IDE约束管理器将任何已编辑的约束保存回XDC文件中的原始位置,但不会保存在Tcl脚本中。 任何新约束都保存在标记为目标的XDC文件的末尾。

2020-11-13 10:53:38 5530

5530

Tcl介绍 Vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发。与之前的ISE设计套件相比,Vivado可以说是全新设计的。无论从界面、设置、算法

2020-11-17 17:32:26 3306

3306 由于Vivado下载程序步骤和ISE有较大差异,特此写此文章,希望对大家有所帮助。 1,下载文件生成 在.bit文件生成后,在TCL中输入 write_cfgmem -format mcs

2021-01-02 10:45:00 9173

9173

作者:材哥,玩儿转FPGA 前言 vivado和ISE的使用差别很大,Vivado是专门针对7系列和以后系列的FPGA/AP SOC进行高效设计的工具,特别是最近提出的UltraFast设计方法

2020-12-25 14:53:36 11506

11506

很对人在使用Vivado时喜欢使用多个约束文件对整个工程进行约束,同时Vivado允许设计者使用一个或多个约束文件。虽然使用一个约束文件对于一个完整的编译流程来说看似更方便,但是在一些情况下,这会

2021-10-13 16:56:54 7907

7907 Vivado下set_multicycle_path的使用说明 vivado下多周期路径约束(set_multicycle_path)的使用,set_multicycle_path一般...

2021-12-20 19:12:17 1

1 XDC约束可以用一个或多个XDC文件,也可以用Tcl脚本实现;XDC文件或Tcl脚本都要加入到工程的某个约束集(set)中;虽然一个约束集可以同时添加两种类型约束,但是Tcl脚本不受Vivado工具管理,因此无法修改其中的约束;

2022-06-30 11:27:23 5420

5420 Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-19 16:20:51 2298

2298 提到位置约束,我们会想到手工布局的方式,即画Pblock,将指定模块放入相应Pblock内,这既是面积约束又是位置约束,但显然这种约束是较为具体的位置约束。这种方式需要工程师有一定的经验,有时还需要

2022-11-17 11:47:46 3587

3587 版本迁移的操作想必大家已经做过不少了,其中包括从ISE转换到vivado与vivado老版本迁移到新版本。郑智海同学给大家介绍了一下如何把工程从ISE迁移到vivado中。

2023-01-30 09:11:30 6274

6274 Xilinx的新一代设计套件Vivado中引入了全新的约束文件 XDC,在很多规则和技巧上都跟上一代产品 ISE 中支持的 UCF 大不相同,给使用者带来许多额外挑战。Xilinx 工具专家告诉你,其实用好 XDC 很容易,只需掌握几点核心技巧,并且时刻牢记:XDC 的语法其实就是 Tcl 语言。

2023-03-28 09:51:10 4592

4592 Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43:09 2185

2185 《XDC 约束技巧》系列中讨论了XDC 约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入 Vivado中 的 XDC 实际上就是用户设定的目标,Vivado

2023-05-04 11:20:31 5693

5693

前面几篇文章已经详细介绍了FPGA时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。

2023-06-23 17:44:00 4086

4086

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 6081

6081

Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束,有利于综合逻辑的优化,同时综合后的design里面可以评估时序。

2023-07-03 09:03:19 1424

1424 帮到不经常看群消息的小伙伴,另一方面也算是我们的技术积累。 Q:Vivado的Implementation阶段约束报警告? [Vivado 12-627] No clocks matched

2023-08-08 14:10:48 2217

2217 电子发烧友网站提供《Vivado Design Suite用户指南:使用约束.pdf》资料免费下载

2023-09-13 15:48:39 2

2 有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们可以打开布线后的dcp,直接在Vivado Tcl Console里输入更新后的时序约束。如果调整

2024-10-24 15:08:40 1602

1602

我是一名物联网公司的开发者小王, 最近在给智能咖啡机联网。 要连Wi-Fi, 大家可能以为和手机平板设备一样 输入账号和密码就可以 结果发现—— 这简直是 “联网版九九八十一难”! 在这套联网流程中 多次重启? 频繁切换模式? 整体操作体验差? 连接始终不稳定? 这时候, 手机响了 有时候 一个人上班 真挺无助的...... 在智能家电这类对连接稳定性与用户体验要求较高的场景下, 稳定、快速、简单的联网方式显得尤为关键。 整个Wi-Fi扫描与连接

2025-04-30 16:20:54 840

840

电子发烧友App

电子发烧友App

评论