1、前言

FPGA端挂载DDR时,对FPGA引脚的约束和选择并不是随意的,有一定的约束规则,一般可以通过利用vivado工具中的pin assignment去选择合适的位置辅助原理图设计。

2、DDR3约束规则

XILINX 7series FPGA支持高性能存储接口,对于DDR来说分为数据(DQ,DQS,DM)和控制(地址和控制信号)两类引脚,在和FPGA互联时,DDR数据部分以字节组为单位,即每8个数据线和对应的DQS和DM数据掩码作为一组,对于64位DDR来说就有8个字节组。DDR控制部分不分组,可以任意接在同一的IO BANK内,但不能跨BANK放置。

FPGA的IO BANK有50 pins,划分为4个区域(4*12)和2个VRN/VRP管脚,DDR字节组(8DQ+2DQS+1DM)需要放在FPGA bank 区域(12 pins)里,同一个区域内除了DQS需要接在DQS位置,其余管脚可以在区域内任意换位置,区域里多余的管脚可以用于接其他控制信号(除RAS_NCAS_NWE_NCS_NODT等)。

当系统时钟推荐放置在地址控制IO BANK内,并且应当放置在SRCCMRCCDQS等位置上,当存在多个时钟CK时应该将其放置在同一字节区域内

单个DDR接口不允许使用超过3个IO BANK,并且当使用3个BANK时,地址控制部分必须在中间BANK的位置,且不允许跨BANK分布。

VRN/VRP一般用作数控阻抗DCI,但是特殊情况下也可以用作地址控制管脚。

为了减小PCB设计复杂性,通常PCB布线时需要换pin以方便走线,减小布线交叉的情况,布线时允许换pin的原则有:

1、数据部分字节区域内部可以任意换pin(除DQS专用引脚)

2、数据部分字节区域之间可以任意互换

3、地址控制部分可以在对应bank 内任意字节区域之内或者之间进行换pin,但是要保证CK信号放在srccmrccdqs等pn对上。

3、利用VIVADO辅助原理图设计

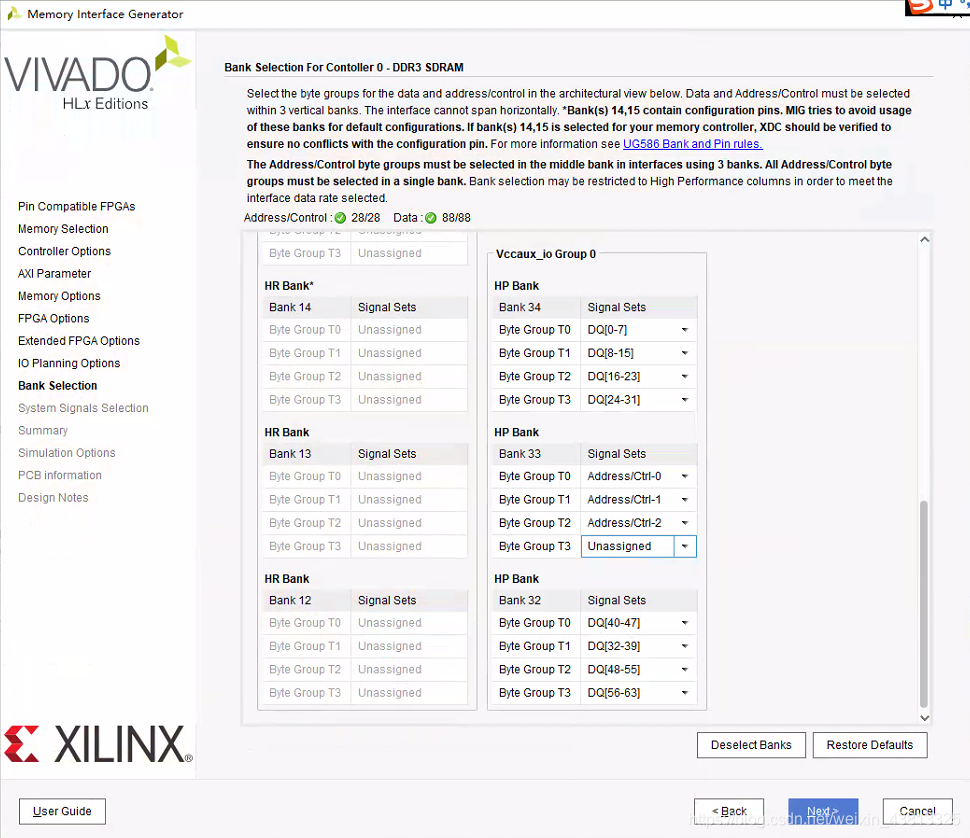

使用vivado IPCORE进行设置时可以看到比较典型的64位DDR3的引脚分配。

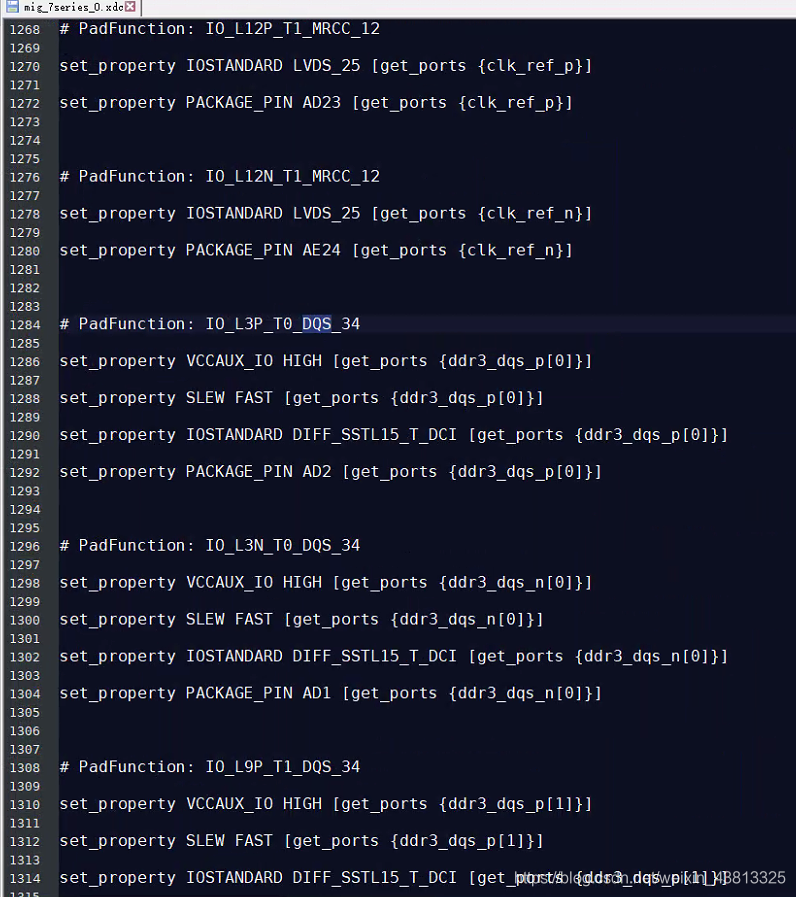

具体到管脚上的分配可以查看IP CORE的XDC约束文件看到,根据约束去辅助原理图设计,保证设计可用性。

3、DDR3 IP核时钟需求

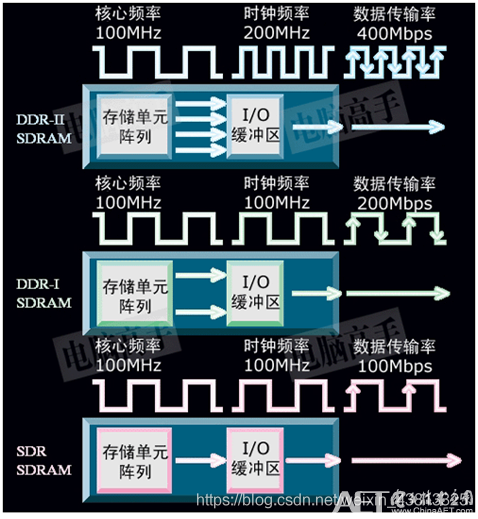

首先了解DDR的工作时钟和内核时钟与数据速率的关系。下图可知工作时钟=数据速率/2,(因为DDR在时钟上下降沿都采样数据),内核时钟=数据速率/8(数据预取bit为8),因此工作时钟和内核时钟之间的关系就是4:1的关系,如果是数据速率为1600M的DDR3,工作时钟应该是800M,用户时钟为200M,同时系统还需要一个200M固定参考时钟用于延时调整,这几个时钟通常利用输入系统参考时钟(外部晶振参考时钟或者内部PLL输出时钟)经过DDR内部PLL锁出工作时钟、用户时钟、参考时钟。

原文标题:XILINX 7series FPGA挂载DDR3之引脚约束

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

FPGA

+关注

关注

1655文章

22287浏览量

630308 -

DDR3

+关注

关注

2文章

287浏览量

43941 -

Xilinx

+关注

关注

73文章

2192浏览量

129938 -

时钟

+关注

关注

11文章

1953浏览量

134544 -

IP核

+关注

关注

4文章

339浏览量

51716

原文标题:XILINX 7series FPGA挂载DDR3之引脚约束

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

DDR3 SDRAM控制器IP核的写命令和写数据间关系讲解

cyclone V控制DDR3的读写,quartusII配置DDR3 ip核后,如何调用实现DDR3的读写呢,谢谢

如何使用IP核生成的xdc文件?

DDR3存储器接口控制器IP助力数据处理应用

Xilinx:K7 DDR3 IP核配置教程

紫光同创FPGA入门指导:DDR3 读写——紫光盘古系列50K开发板实验教程

紫光同创FPGA入门指导:DDR3 读写——紫光盘古系列50K开发板实验教程

DDR3 SDRAM的IP核调取流程

lattice DDR3 IP核的生成及调用过程

Gowin DDR3 Memory Interface IP用户指南

FPGA学习-DDR3

基于AXI总线的DDR3读写测试

DDR3约束规则与IP核时钟需求

DDR3约束规则与IP核时钟需求

评论