时序不满足约束,会导致以下问题:

• 编译时间长的令人绝望

• 运行结果靠运气——时对时错

导致时序问题的成因及其发生的概率如下表:

由上表可见,造成时序问题的主要原因除了约束不完整,就是路径问题,本文就时序路径分析问题作一介绍:

1、时钟网络分析

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。

报告时钟网络命令可以从以下位置运行:

① Vivado®IDE中的Flow Navigator

② Tcl命令:report_clock_networks -name {network_1}

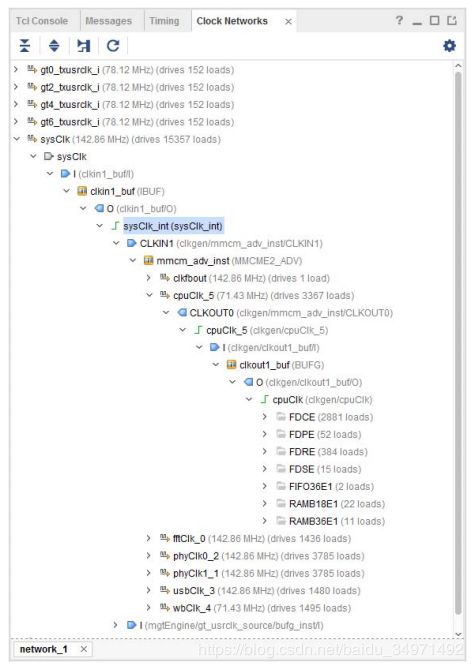

报告时钟网络提供设计中时钟树的树视图。 如下图。每个时钟树显示从源到端点的时钟网络,端点按类型排序。

时钟树:

• 显示由用户定义或由工具自动生成的时钟。

• 报告从I / O端口加载的时钟。

• 可用于查找驱动其他BUFGs的BUFGs。

• 显示驱动非时钟负载的时钟。

温馨提醒:完整的时钟树仅在报告的GUI形式中详细说明。此报告的文本版本仅显示时钟根的名称。

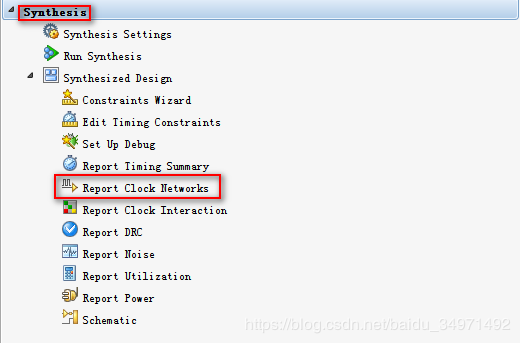

以vivado自带的例子wavegen为例。点击Synthesis的Report CLock Networks如下图所示:

时钟clk_pin_p从输入引脚输入之后,经过IBUFDS,再通过MMCM生成时钟,同时显示了各个时钟的频率。如果我们未添加时钟约束,报告将显示Unconstrained(未约束的时钟,root clock).可以选中未约束的时钟右击选择Create Clock创建时钟。

如下图所示:

2、 跨时钟域路径分析

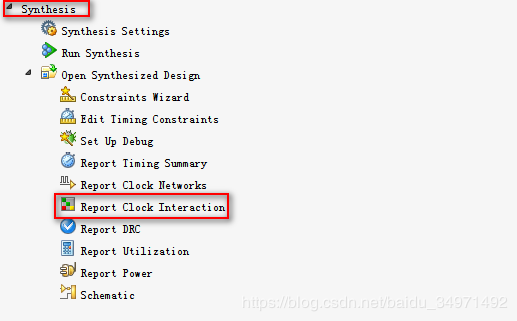

若要查看跨时钟域路径分析报告,可选择以下内容之一来查看:

• Reports > Timing > Report Clock Interaction

• Flow Navigator > Synthesis > Report Clock Interaction

• Flow Navigator > Implementation > Report Clock Interaction

• Tcl command: report_clock_interaction -name clocks_1

如下图所示,点击Synthesis–>Report Clock Interaction.

跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。跨时钟域路径分析报告有助于识别可能存在数据丢失或亚稳态问题的情况.

运行“Report Clock Interaction”命令后,结果将在“时钟交互”窗口中打开。如下图所示,时钟交互报告显示为时钟域矩阵,源时钟位于垂直轴,目标时钟位于水平轴。

No Path --用黑色框来表示:没有从源时钟到目标时钟的定时路径。在这种情况下,没有时钟交互,也没有任何报告。

Timed – 用绿色框来表示:源时钟和目标时钟具有同步关系,并安全地被约束在一起。当两个时钟具有共同的主时钟和简单的周期比时,该状态由定时引擎确定。

User Ignored Paths–用深蓝色框来表示:用户定义的假路径或时钟组约束涵盖从源时钟到目标时钟的所有路径。

Partial False Path–用淡蓝色框来表示:用户定义的伪路径约束覆盖了从源时钟到目标时钟的一些时序路径,其中源时钟和目标时钟具有同步关系。

Timed (Unsafe)–用红色框来表示:源时钟和目标时钟具有异步关系。在这种情况下,没有共同的主时钟或没有可扩展的时段。

Partial False Path (Unsafe)–用橘橙色框来表示:此类别与Timed(Unsafe)相同,只是由于伪路径异常,从源时钟到目标时钟的至少一条路径被忽略。

Max Delay Datapath Only --用紫色框来表示:set_max_delay -datapath_only约束涵盖从源时钟到目标时钟的所有路径。

Report_clock_interaction呈现的报告并不是根据时序约束生成的,但是和时序约束有关,它反映出用户定义的伪路径。

以wavegen工程为示例,点击Report Clock Interaction,如下图所示:

ID: 正在显示的源/目标时钟对的数字ID。

Source Clock: 路径源时钟域。

Destination Clock: 路径终端的时钟域。

Edges (WNS):用于计算最大延迟分析(设置/恢复)的最差裕度的时钟边缘。

WNS (Worst Negative Slack):为跨越指定时钟域的各种路径计算的最差裕度时间。负裕量时间表示路径违反了所需的建立(或恢复)时间的问题。

TNS (Total Negative Slack):属于跨越指定时钟域的路径的所有端点的最差松弛违规的总和。

Failing Endpoints (TNS): 交叉路径中的端点数量无法满足时序要求。违规的总和对应于TNS。

Total Endpoints (TNS):交叉路径中端点的总数。

Path Req (WNS):定时路径要求对应于WNS列中报告的路径。如果两个时钟中的至少一个时钟的上升沿和下降沿都有效,则在任何时钟对之间可能存在若干路径要求,或者在两个时钟之间的路径上应用了一些时序异常。本专栏中报告的值并不总是最具挑战性的要求。

Clock Pair Classification: 提供有关公共节点和时钟对之间的公共周期的信息。从最高优先级到最低优先级:忽略,虚拟时钟,无公共时钟,无公共周期,部分公共节点,无公共节点和清除。

Inter-Clock Constraints: 显示源时钟和目标时钟之间所有路径的约束摘要。

-

Vivado

+关注

关注

19文章

860浏览量

71396 -

时序路径

+关注

关注

0文章

12浏览量

1523

发布评论请先 登录

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

vivado时序分析相关经验

移植E203到Genesys2开发板时遇到时序问题的常见原因

在Windows10上运行vivado使用tcl文件创建E203项目路径错误的问题

win10环境下使用vivado生成.bit与.mcs文件

E203内核移植到FPGA开发板时出现时序违例的解决方式

时序约束问题的解决办法

关于综合保持时间约束不满足的问题

E203分享之DDR扩展方案实施流程(下)

京东:调用用户行为API分析购买路径,优化页面跳转逻辑

技术资讯 I Allegro 设计中的走线约束设计

Vivado无法选中开发板的常见原因及解决方法

西门子再收购EDA公司 西门子宣布收购Excellicon公司 时序约束工具开发商

详细解析vivado约束时序路径分析问题

详细解析vivado约束时序路径分析问题

评论