对话框的约束部分下,选择默认约束设置作为活动约束设置;包含在Xilinx设计约束(XDC)文件中捕获的设计约束的一组文件,可以将其应用于设计中。两种类型的设计约束是: 1) 物理约束:这些约束定义引脚

2020-11-23 14:16:36 6670

6670

引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2022-07-25 10:13:44 5970

5970 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 2392

2392 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 1938

1938

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 12757

12757

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 4234

4234 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 3055

3055 在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。

2023-06-26 14:47:16 3379

3379

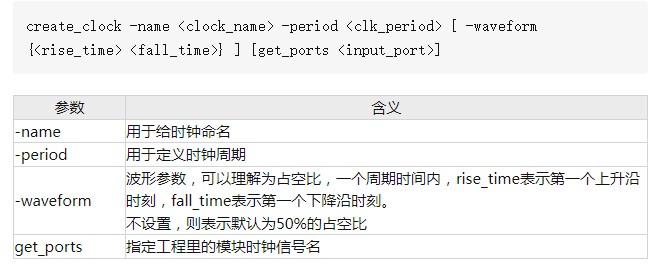

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 3030

3030

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 5117

5117

今天给大侠带来 Xilinx ISE14.7 LVDS应用,话不多说,上货。

最近项目需要用到差分信号传输,于是看了一下FPGA上差分信号的使用。Xilinx FPGA中,主要通过原语实现差分信

2024-06-13 16:28:52

,FPGA上的全局时钟管脚用完了就出现不够用的情况。FPGA全局时钟约束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

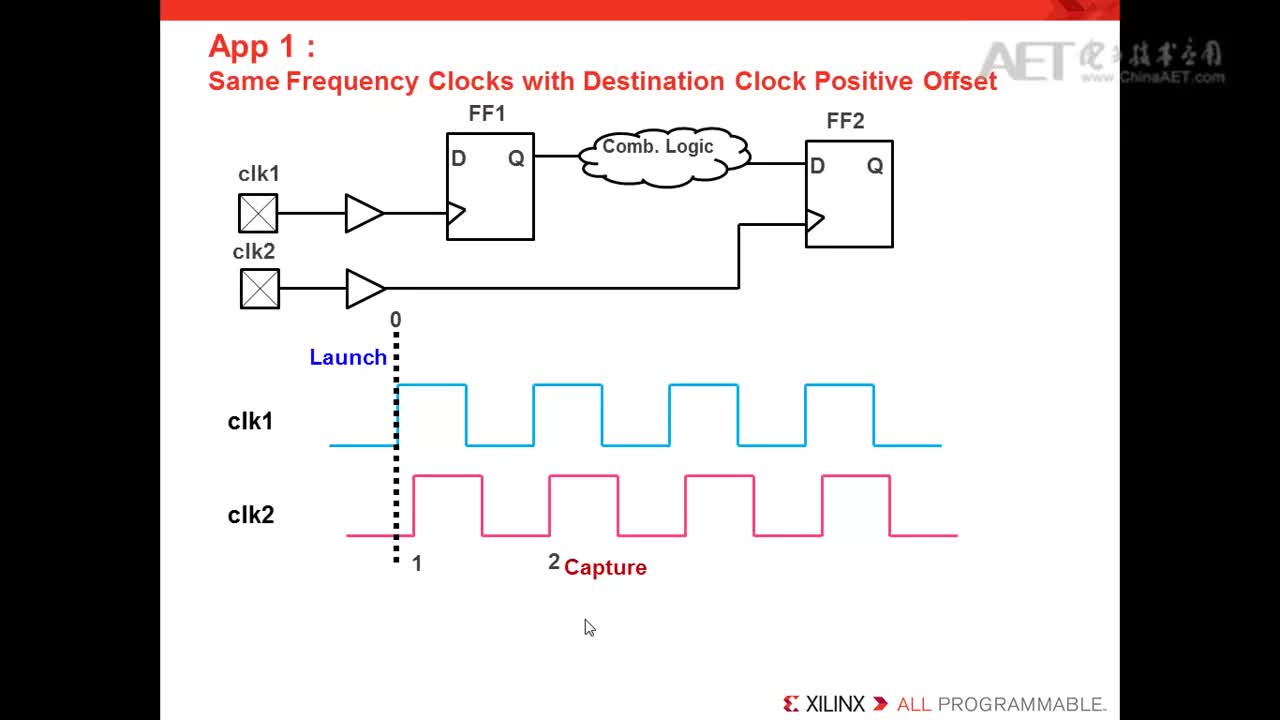

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束

2016-06-02 15:54:04

不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束+时序例外约束+I/O约束 I/O约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时

2017-12-27 09:15:17

你好: 现在我使用xilinx FPGA进行设计。遇到问题。我不知道FPGA设计是否符合时序要求。我在设计中添加了“时钟”时序约束。我不知道如何添加其他约束。一句话,我不知道哪条路径应该被禁止。我

2019-03-18 13:37:27

FPGA的DCM模块,40MHz时钟输入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。对40MHz时钟添加了约束,系统不是会自动对三个输出时钟进行约束

2017-05-25 15:06:47

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

本帖最后由 china198 于 2013-8-30 12:28 编辑

XILINX的作品---时序约束,写的非常棒

2013-08-30 12:26:47

各位大神,请问Xilinx FPGA中的DCI是如何使用的?我知道是把每个Bank的VRP、VRN管脚分别下拉、上拉,除此之外,在HDL代码和约束中应该如何写呢?查了半天资料没有查到,所以来论坛问问。@LQVSHQ

2017-08-20 20:51:57

大家好!想请教一下,Xilinx FPGA可以设置引脚带内部上拉电阻吗? 怎么设置?

2013-10-11 20:59:26

本帖最后由 eehome 于 2013-1-5 09:52 编辑

不可多得的Xilinx FPGA中文培训材料教程,涉及到virtel的基本架构、赛灵思设计流程、如何阅读报告、时序约束等经典

2012-03-02 09:51:53

用notepad++的关联设置Lesson07 特权Xilinx FPGA SF-SP6入门指南 -- ISE与Modelsim联合仿真之库编译Lesson08 特权Xilinx FPGA SF-SP6入门

2015-07-22 11:49:20

今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为

2024-04-12 17:39:04

今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为

2024-05-06 15:51:23

(TX_CLK_o)。我想使用下面的约束命令来设置时钟转发,但我在合成时发现了警告。警告是什么意思?// constraints命令create_generated_clock -name TX_CLK_o

2020-05-04 08:04:41

在给 FPGA 做逻辑综合和布局布线时,需要在工具中设定时序的约束。通常,在 FPGA 中都包含有4 种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入 到输出的纯组合逻辑

2012-03-05 15:02:22

Xilinx_fpga_设计:全局时序约束及试验总结

2012-08-05 21:17:05

完成顶层模块的实现并且仿真正确后,还需要编写用户约束文件,其中引脚约束文件是必不可少的,它将模块的端口和 FPGA 的管脚对应起来。具体步骤如下。(1)创建约束文件。新建一个源文件,在代码类型中选

2018-09-29 09:18:05

大家好, 谁能告诉我如何在RTL或xilinx spartan fpga的约束文件中插入1.56ns延迟缓冲区?这是为了避免xilinx工具在进行合成后报告的保持时间违规。问候马赫什以上来自于谷歌

2019-06-18 07:18:04

1.工艺节点 首先不管选择什么厂家的产品,都建议在其主流产品中选择合适的芯片。 以上是目前 Xilinx 主流的也是常用的几个 FPGA 产品系列,这里不谈传说中的后两个系列

2020-12-23 17:21:03

大家好我正在使用Virtex5 FPGA,我在设计中添加了一个OFFSET IN约束,如下所示。NET“Sysclk”TNM_NET =“Sysclk”;TIMESPEC“TS_Sysclk

2020-06-13 19:23:05

FPGACPLD设计工具——Xilinx ISE使用详解的主要内容:第1章 ISE系统简介第2章 工程管理器与设计输入工具第3章 ModelSim仿真工具第4章 ISE中集成的综合工具第5章 约束第6章

2009-07-24 16:06:58 198

198 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、Verilog HDL开发基础与进阶、Xilinx FPGA电路原理与系统设计

2012-07-31 16:20:42 12480

12480

本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 Xilinx FPGA设计进阶(提高篇)

有需要的下来看看

2015-12-29 15:45:48 12

12 轻松高效地设置 PCB 设计约束的八个步骤

2016-01-06 14:49:57 0

0 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 52

52 Xilinx时序约束设计,有需要的下来看看

2016-05-10 11:24:33 18

18 轻松高效地设置 PCB 设计约束的八个步骤

2022-05-11 16:44:57 0

0 FPGA学习资料教程之Xilinx时序约束培训教材

2016-09-01 15:27:27 0

0 FPGA学习资料教程之Xilinx-FPGA-引脚功能详细介绍

2016-09-01 15:27:27 0

0 FPGA学习资料教程之Xilinx-FPGA高级开发工具,感兴趣的可以看看。

2016-09-01 15:27:27 0

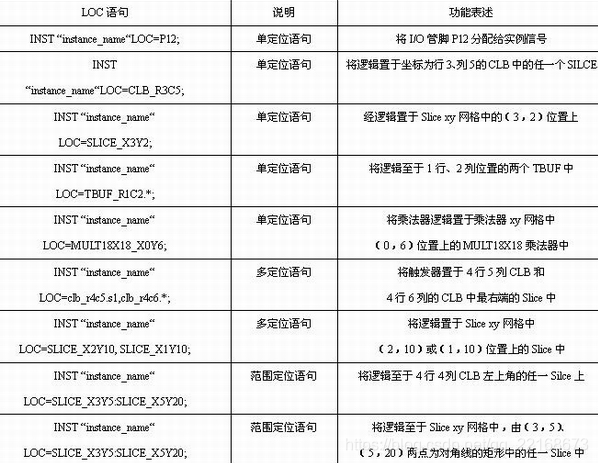

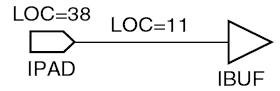

0 引脚和区域约束也就是LOC约束(location)。定义了模块端口和FPGA上的引脚的对应关系。 那么我们应该怎么写呢?

2018-07-14 02:49:00 11898

11898 Xilinx FPGA编程技巧常用时序约束介绍,具体的跟随小编一起来了解一下。

2018-07-14 07:18:00 5223

5223

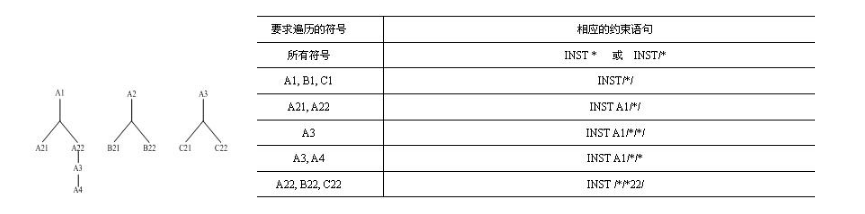

FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。

2017-02-11 06:33:11 2023

2023 其中“location”可以是FPGA芯片中任一或多个合法位置。如果为多个定位,需要用逗号“,”隔开,如下所示

2017-02-11 11:00:12 1373

1373 xilinx 约束实现

2017-03-01 13:12:47 15

15 FPGAs have changed dramatically since Xilinx first introduced them just 15 years ago. In the ast

2017-09-20 18:41:55 14

14 Xilinx FPGA的Maxim参考设计

2017-10-31 09:59:24 23

23 一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2967

2967

针对八通道采样器AD9252的高速串行数据接口的特点,提出了一种基于FPGA时序约束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行数据,利用FPGA内部的时钟管理模块DCM、位置约束

2017-11-17 12:27:01 7352

7352

XDC中的I/O约束虽然形式简单,但整体思路和约束方法却与UCF大相径庭。加之FPGA的应用特性决定了其在接口上有多种构建和实现方式,所以从UCF到XDC的转换过程中,最具挑战的可以说便是本文将要

2017-11-17 19:01:00 8137

8137

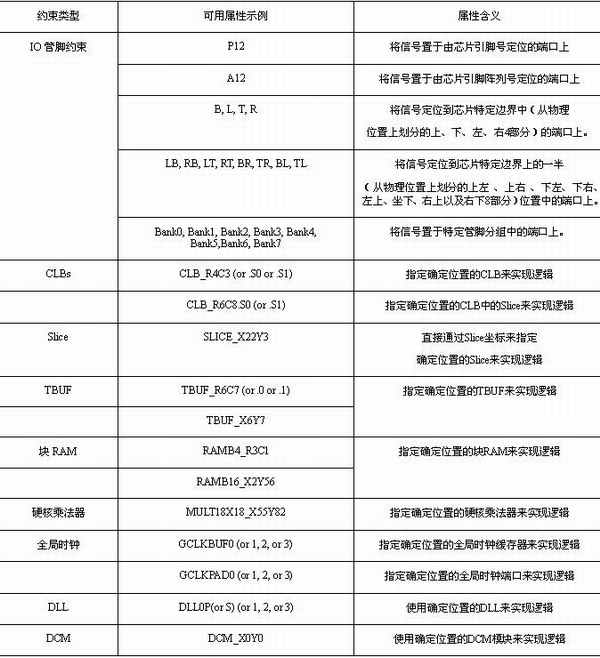

本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。 Xilinx定义了如下几种约束类型

2017-11-24 19:59:29 4435

4435

摘要:本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。 Xilinx定义了如下几种约束类型

2017-11-25 01:27:02 7029

7029

详细讲解了xilinx的时序约束实现方法和意义。包括:初级时钟,衍生时钟,异步时终域,多时终周期的讲解

2018-01-25 09:53:12 6

6 介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,才可能满足约束,约束反过来检查

2018-06-25 09:14:00 7199

7199 FPGA本身是有专门的时钟cell的,以xilinx FPGA为例,就是primitive库中的BUFG。

2018-12-22 15:33:59 2175

2175 了解如何将Altera的SDC约束转换为Xilinx XDC约束,以及需要更改或修改哪些约束以使Altera的约束适用于Vivado设计软件。

2018-11-27 07:17:00 5883

5883 只需要简单地用鼠标点击几下,就可定义、编辑和查看 PADS 原理图环境中的网络约束。为高速、布线和间距设置网络和网络类约束,为差分对设置特殊约束,或定义匹配长度组。高级工具提示会显示如何操作。

2019-05-17 06:14:00 3415

3415

本文主要介绍Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 6756

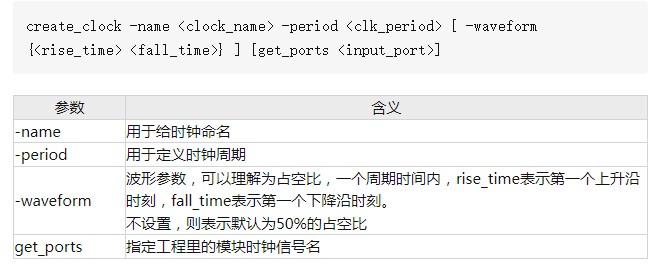

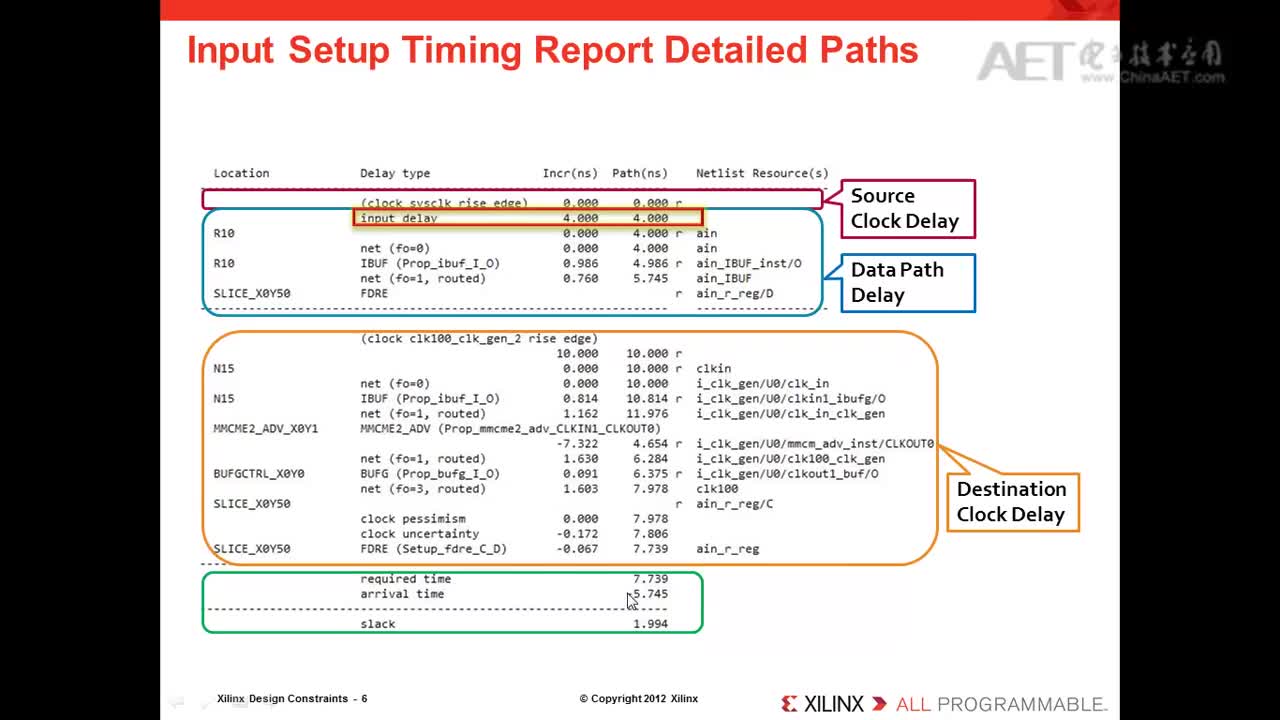

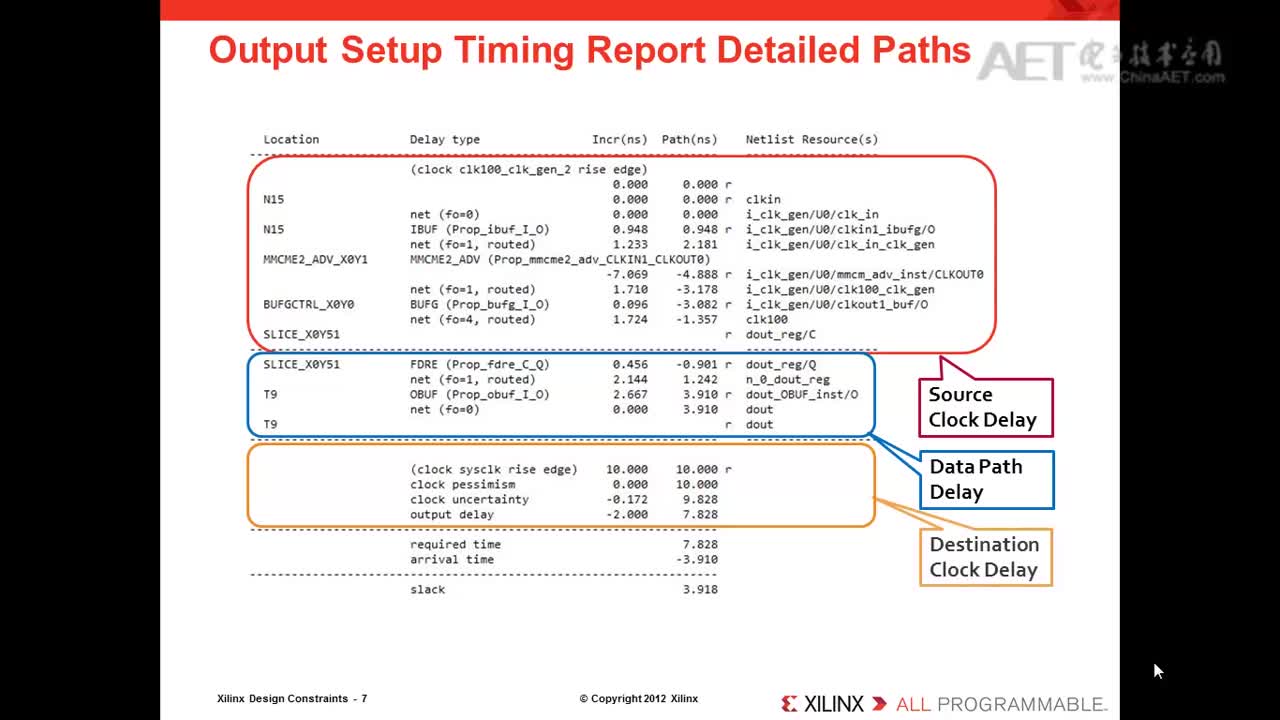

6756 1 I/O延迟约束介绍 要在设计中精确建模外部时序,必须为输入和输出端口提供时序信息。Xilinx Vivado集成设计环境(IDE)仅在FPGA边界内识别时序,因此必须使用以下命令指定超出这些边界

2020-11-29 10:01:16 6236

6236 本文档的主要内容详细介绍的是Xilinx的时序设计与约束资料详细说明。

2021-01-14 16:26:51 34

34 有人希望能谈谈在做FPGA设计的时候,如何理解和使用过约束。我就以个人的经验谈谈: 什么是过约束; 为什么会使用过约束; 过约束的优点和缺点是什么; 如何使用过约束使自己的设计更为健壮。 什么是过

2021-03-29 11:56:24 6891

6891

PCB设计-设置布线约束条件说明。

2021-04-13 09:54:24 0

0 AD5933 pmod Xilinx FPGA参考设计

2021-04-21 18:41:19 3

3 AD7780 pmod Xilinx FPGA参考设计

2021-04-22 13:35:23 15

15 引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2021-04-27 10:36:59 6127

6127

ADT7420 pmod Xilinx FPGA参考设计

2021-05-12 08:08:26 3

3 ADXL345 pmod Xilinx FPGA参考设计

2021-05-16 19:45:16 8

8 ADP5589 pmod Xilinx FPGA参考设计

2021-05-16 20:37:58 1

1 AD5628 pmod Xilinx FPGA参考设计

2021-05-19 14:34:17 4

4 AD7193 pmod Xilinx FPGA参考设计

2021-05-19 15:18:13 2

2 AD7091R pmod Xilinx FPGA参考设计

2021-05-19 18:31:59 7

7 AD7156 pmod Xilinx FPGA参考设计

2021-05-20 12:32:16 10

10 AD7991 pmod Xilinx FPGA参考设计

2021-05-20 12:37:26 12

12 AD5781 pmod Xilinx FPGA参考设计

2021-05-24 10:29:20 20

20 DDR4布线之allegro约束规则设置综述

2021-09-08 10:34:29 0

0 上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 2166

2166

Xilinx FPGA开发实用教程资料包免费下载。

2022-04-18 09:43:46 29

29 本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-05-11 10:07:56 4989

4989

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 3757

3757

约束文件是FPGA设计中不可或缺的源文件。那么如何管理好约束文件呢? 到底设置几个约束文件? 通常情况下,设计中的约束包括时序约束和物理约束。前者包括时钟周期约束、输入/输出延迟约束、多周期路径约束

2022-12-08 13:48:39 2150

2150 FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 2404

2404 Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 1252

1252

FPGA设计中,时序约束对于电路性能和可靠性非常重要。

2023-06-26 14:53:53 6881

6881

ALLEGRO约束规则设置步骤(以DDR为例)

2022-12-30 09:19:29 12

12 Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 5686

5686 xilinx FPGA IOB约束使用以及注意事项 一、什么是IOB约束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距离IO最近的寄存器,同时位置固定。当你输入或者输出

2025-01-16 11:02:01 1657

1657

Vivado中时序分析工具默认会分析设计中所有时钟相关的时序路径,除非时序约束中设置了时钟组或false路径。使用set_clock_groups命令可以使时序分析工具不分析时钟组中时钟的时序路径,使用set_false_path约束则会双向忽略时钟间的时序路径

2025-04-23 09:50:28 1079

1079

电子发烧友App

电子发烧友App

评论