约束衍生时钟

系统中有4个衍生时钟,但其中有两个是MMCM输出的,不需要我们手动约束,因此我们只需要对clk_samp和spi_clk进行约束即可。约束如下:

create_generated_clock -name clk_samp -source [get_pins clk_gen_i0/clk_core_i0/clk_tx] -divide_by 32 [get_pins clk_gen_i0/BUFHCE_clk_samp_i0/O] create_generated_clock -name spi_clk -source [get_pins dac_spi_i0/out_ddr_flop_spi_clk_i0/ODDR_inst/C] -divide_by 1 -invert [get_ports spi_clk_pin]

这里需要注意的是,如果该约束中使用get_pins(即产生的时钟并非输出到管脚),那么无论是source的时钟还是我们衍生的时钟,在get_pins后面的一定是这个时钟最初的产生位置。在视频中我们会具体展示)。

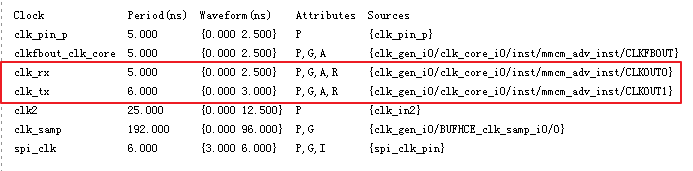

我们再运行report_clocks,显示如下:

我们在理论篇的“create_generated_clock”一节中讲到,我们可以重新设置Vivado自动生成的衍生时钟的名字,这样可以更方便我们后续的使用。按照前文所讲,只需设置name和source参数即可,其中这个source可以直接从report_clocks中得到,因此我们的约束如下:

create_generated_clock -name clk_tx -source [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1] [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT1] create_generated_clock -name clk_rx -source [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1] [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT0]

大家可以对比下report_clocks的内容和约束指令,很容易就能看出它们之间的关系。

把上述的约束指令在tcl中运行后,我们再运行一遍report_clocks,显示如下:

在时序树的分析中,我们看到,clk_samp和clk2两个异步时钟之间存在数据交互,因此要进行约束,如下:

set_clock_groups -asynchronous -group [get_clocks clk_samp] -group [get_clocks clk2]

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22502浏览量

639070 -

Vivado

+关注

关注

19文章

860浏览量

71394

发布评论请先 登录

相关推荐

热点推荐

FPGA主时钟约束详解 Vivado添加时序约束方法

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

发表于 06-06 18:27

•1.3w次阅读

FPGA时序约束之衍生时钟约束和时钟分组约束

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟

发表于 06-12 17:29

•4496次阅读

FPGA时序约束之建立时间和保持时间

FPGA中时序约束是设计的关键点之一,准确的时钟约束有利于代码功能的完整呈现。进行时序约束,让软件布局布线后的电路能够满足使用的要求。

发表于 08-14 17:49

•2368次阅读

FPGA实战演练逻辑篇56:VGA驱动接口时序设计之3时钟约束

VGA驱动接口时序设计之3时钟约束本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 如图8.2

发表于 07-30 22:07

FPGA时钟约束问题

FPGA的DCM模块,40MHz时钟输入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。对40MHz时钟添加了约束,系统不是会自动对三个输出

发表于 05-25 15:06

FPGA设计约束技巧之XDC约束之I/O篇(下)

XDC中的I/O约束虽然形式简单,但整体思路和约束方法却与UCF大相径庭。加之FPGA的应用特性决定了其在接口上有多种构建和实现方式,所以从UCF到XDC的转换过程中,最具挑战的可以说便是本文将要

发表于 11-17 19:01

•8299次阅读

FPGA时序约束之设置时钟组

Vivado中时序分析工具默认会分析设计中所有时钟相关的时序路径,除非时序约束中设置了时钟组或false路径。使用set_clock_groups命令可以使时序分析工具不分析时钟组中

FPGA案例之衍生时钟约束

FPGA案例之衍生时钟约束

评论