本章的实验任务是在 PL 端自定义一个 AXI4 接口的 IP 核,通过 AXI_HP 接口对 PS 端 DDR3 进行读写测试,读写的内存大小是 4K 字节。

2025-11-24 09:19:42 3467

3467

microblaze和jtag-to-axi(jtag2axi)虽然也提供了访问axi总线的能力,但是依赖于xilinx平台。而uart-to-axi(uart2axi4)桥接器并不依赖任何平台

2025-12-02 10:05:43 1842

1842

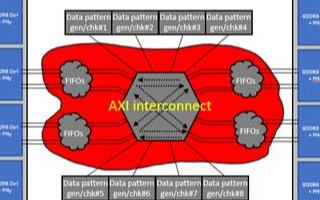

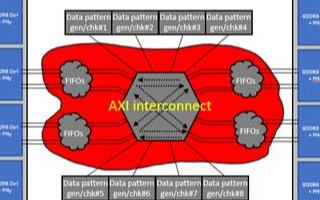

对于AXI interconnect模块,我们采用Github上开源的AXI4总线连接器来实现,这个AXI4总线连接器将4个AXI4总线主设备连接到8个AXI4总线从设备,源代码可以在参考文献2

2020-09-03 12:39:38 1181

1181

Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,专用于和元器件内的控制寄存器进行通信。AXI-Lite允许构建简单的元件接口。这个接口规模较小,对设计和验证方面的要求更少

2020-09-27 11:33:02 9821

9821

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI4

2020-12-04 12:22:44 9054

9054

构成的传输数据的通道, 一般由数据线、地址线、 控制线构成。 Xilinx从6系列的 FPGA 开始对 AXI 总线提供支持, 此时 AXI 已经发展到

2020-12-25 14:07:02 6724

6724

麻烦,灵活性也比较差,本节课程讲解如何直接通过AXI总线来读写PS端ddr的数据,这里面涉及到AXI4协议,vivado的FPGA调试等。

2021-01-30 09:54:00 16464

16464

赛灵思 AXI Verification IP (AXI VIP) 是支持用户对 AXI4 和 AXI4-Lite 进行仿真的 IP。它还可作为 AXI Protocol Checker 来使用。

2022-07-08 09:24:17 2976

2976 在 AXI 基础第 2 讲 一文中,曾提到赛灵思 Verification IP (AXI VIP) 可用作为 AXI 协议检查工具。在本次第4讲中,我们将来了解下如何使用它在 AXI4 (Full) 主接口中执行验证(和查找错误)。

2022-07-08 09:31:38 4371

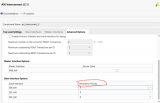

4371 AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互连以及其他AXI4系统外设上生成特定序列(流量)。它根据IP的编程和选择的操作模式生成各种类型的AXI事务。是一个比较好用的AXI4协议测试源或者AXI外设的初始化配置接口。

2023-11-23 16:03:45 5162

5162

AWID[3:0]与ARID[3:0]:对于只有一个主机从机设备,该值可设置为任意。

2025-01-22 15:04:01 4096

4096

AXI接口FIFO是从Native接口FIFO派生而来的。AXI内存映射接口提供了三种样式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的应用外,AXI FIFO还可以用于AXI系统总线和点对点高速应用。

2025-03-17 10:31:11 1914

1914

VLANs 5.内嵌ARP 6.用XGMII高速接口连接10G PMA-PCS PHY 7.一个工作在156.25MHz的64bit的axi4—stream接口让用户调试使用 8.可通过一个32bit

2016-03-11 10:57:58

最近在搞AXI4总线协议,有一个问题困扰了两天,真的,最后知道真相的我,差点吐血。 问题是这样的,我设置了突发长度为8,结果,读了两个轮回不到,断了,没有AWREDATY信号了,各种找,最后发现设置

2016-06-23 16:36:27

如果在仿真的时候出现可以写,可以读,但是读出来的数据一直是那么几个的问题,很有可能,你和我一样,是个马大哈了,去看DQ,是不是地址也来来去去就那么几个?是的话,可以考虑考虑你的地址的问题,AXI4

2016-06-24 16:25:38

AXI4协议基于猝发式传输机制。在地址通道上,每个交易有地址和控制信息,这些信息描述了需要传输的数据性质。主从设备间的数据传输有两种情况,一种是主设备经过写通道向从设备写数据(简称写交易

2021-01-08 16:58:24

AXI4-Stream跟AXI4的区别在于AXI4-Stream没有ADDR接口,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时,允许无限制的数据突发传输规模

2021-01-08 16:52:32

1、AXI接口协议详解 AXI 总线 上面介绍了AMBA总线中的两种,下面看下我们的主角—AXI,在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线

2022-10-14 15:31:40

AXI 总线上面介绍了AMBA总线中的两种,下面看下我们的主角—AXI,在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线分别为:AXI4

2022-04-08 10:45:31

到新的通道。错误的处理例化了一个Axi4ReadOnlySlaveError:可以看到,只有所有slave端口的地址段大小总和小于Axi4总线能覆盖的地址范围时方例化

2022-08-04 14:28:56

除数和商通道以及必要的时钟和复位逻辑接口。每个AXI总线通道总是包括tdata tuser tlast 和握手信号tvalid tready,其中tuser为附加信息,tlast表示流模式下最后一个

2018-08-13 09:27:32

Xilinx FPGA入门连载47:FPGA片内RAM实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述该工程

2016-01-20 12:28:28

实例内部系统功能框图如图所示。我们通过IP核例化一个FIFO,定时写入数据,然后再读出所有数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察FPGA片内FIFO的读写时序。 2 模块

2016-02-26 10:26:05

`Xilinx FPGA入门连载55:FPGA 片内异步FIFO实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

)读写、DMA读写和数据擦除功能,提供用户一个简单高效的接口实现高性能存储解决方案。NVMe AXI4 Host Controller IP读写的顺序传输长度是RTL运行时动态可配置的,最小

2025-11-14 22:40:50

您可以将协议断言与任何旨在实现AMBA®4 AXI4的接口一起使用™, AXI4 Lite™, 或AXI4流™ 协议通过一系列断言根据协议检查测试接口的行为。

本指南介绍SystemVerilog

2023-08-10 06:39:57

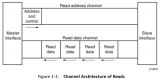

XHB将AXI4协议转换为AHB-Lite协议,并具有AXI4从接口和AHB-Lite主接口。有关AXI4事务如何通过XHB桥接到AHB-Lite的信息,请参阅第2-2页的表2-1

2023-08-02 06:51:45

,突发长度最大支持256。

AXI4-Lite:是AXI4-Full总线的简化版本,主要用于寄存器配置。与AXI4总线相似,AXI4-Lite也具有五个通道。但AXI4-Lite不支持高级功能如突发

2025-06-02 23:05:19

向高速数据流传输的AXI4-Stream接口。如表1所示展示了三种类型接口的主要特点对比。

表1 三种类型AXI4接口对比

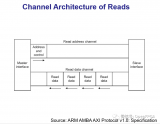

AXI4总线具有读写地址、数据通道分离的特性,使控制通道与数据通道分离、读通道

2025-05-17 10:27:56

的fifo接口),用户只要操作fifo接口,无需关心PCIE的内部驱动。为了便于读者更加明白,可以深入了解PCIE,我们将会制作一个PCIE的连载系列。今天,首先说一下自定义AXI4的IP核,至于AXI4

2019-12-13 17:10:42

AXI 总线是一种高速片内互连总线,其定义于由 ARM 公司推出的 AMBA 协议中,主要用于高性能、高带宽、低延迟、易集成的片内互连需求。AXI4 总线是第四代 AXI 总线,其定义了三种总线接口

2025-06-24 18:00:11

这里以功能完备的 AXI4 接口举例说明 AXI4 总线的相关特点。AXI4 总线采用读写通道分离且数据通道与控制通道分离的方式,这样的总线通道使其具有多主多从的连接特性和并行处理的能力,能够

2025-06-24 18:02:23

这是SoC Designer AXI4协议包的用户指南。该协议包包含SoC Designer组件、探针和ARM AXI4协议的事务端口接口(包括对AMBA4 AXI的支持)。

2023-08-10 06:30:18

data.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。AXI4总线和AXI4-Lite总线具有相同的组成部分:(1)读地址通道,包含ARVALID, ARADDR, ARREADY

2018-01-08 15:44:39

主从设备间直接进行数据的读写,主要用于高速数据传输的场合,如视频、高速AD等。AXI-lite:可用于单个数据传输,主要用于访问一些低速外设。3) AXI接口具有5个独立通道:WriteAddress

2016-12-16 11:00:37

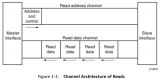

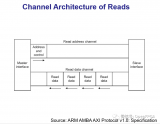

重点介绍AXI4接口,它由五个独立的通道构成:1、读地址2、读数据3、写地址4、写数据5、写响应下面是使用读地址和读数据通道实现读传输过程的示意图:图 9.1.1 读传输过程示意图从上图中可以看到,在

2020-10-22 15:16:34

,Xilinx在IP核中继续使用AXI协议。本章我们对AXI协议作一个简单介绍,并在Vivado中实现一个AXI4接口的IP核,用于对ZYNQ PS端的DDR3进行读写测试。本章包括以下几个部分:1515.1

2020-09-04 11:10:32

,等)构建起连续的数据流。这种接口适合做实时信号处理。 AXI4和AXI4-Lite接口包含5个不同的通道: Read Address Channel Write Address Channel

2021-01-07 17:11:26

的基础上进行扩展,增加到 8 个 AXI4 总线主设备连接到 8 个 AXI4 总线从设备,同时加上了跨时钟域逻辑。为了进行对比,我们用另外一个设计,目的还是用这 8 个读写模块去访问 8 个

2020-09-07 15:25:33

国外的融合技术专家展示了一项基于FPGA的数据采集系统,用于合成孔径成像技术。采用了Xilinx ISE设计软件,支持ARM AMBA AXI4接口。文风犀利,观点新颖,FPGA中使用ARM及AMBA总线中不可多得的资料在赛灵思FPGA中使用ARM及AMBA总线[hide][/hide]

2012-03-01 15:48:17

对应axi4stream_vip_pkg。第二个import是导入刚才例化的vip的pkg,格式为import {Component Name}_pkg

2022-10-09 16:08:45

在这个代码的基础上进行扩展,增加到8个AXI4总线主设备连接到8个AXI4总线从设备,同时加上了跨时钟域逻辑。为了进行对比,我们用另外一个设计,目的还是用这8个读写模块去访问8个GDDR6通道

2020-10-20 09:54:00

多选一的抉择相较于Axi4写通路,多通路的多选一就容易多了。对于Axi4ReadOnlyArbiter,其仅需处理两个问题:Ar通路多端口仲裁,其处理和写通路aw通路基本相同,采用多端口RR调度即可

2022-08-08 14:32:20

元素(如混合端序结构)的支持。

本文档重点介绍AXI4中定义的AXI的关键概念,并强调了差异

适用时,适用于AXI3。AXI5扩展了AXI4,并引入了一些性能和Arm

架构特征。此处描述的关键概念仍然适用,但

AXI5在此未涵盖

2023-08-09 07:37:45

使用AXI4流快速读取?如果这不是一个不错的方法,还有其他方法可以使用Virtex-7来解决这个问题吗?以上来自于谷歌翻译以下为原文Hey all. I'm currently working

2019-05-05 13:14:10

` 1概述Zynq将ARM和FPGA整合到了一个芯片上,它的过人之处不仅是功耗、面积、成本的优化,更多的是将二者之间原本极为受限的数据交互方式转移到芯片内部完成,4条AXI GP通道(2个从机、2个

2019-11-12 10:23:42

芯片可以做到了最优状态。因此,对于用Zynq做开发的工程师而言,如何玩转AXI HP总线就成为了必修课。本实例(zstar_ex56)通过一个简单的AXIHP总线主机的读时序和写时序逻辑,来带领读者掌握

2019-11-26 09:47:20

` 1概述用于PL与DDR3交互的AXI HP总线,它的性能到底如何?吞吐量是否能满足我们的应用?必须4个通道同时使用?还是只使用1个通道?时钟频率的高低对AXI HP总线的带宽有什么影响?这些

2019-11-28 10:11:38

的FPGA开始引入的一个接口协议(AXI3)。在ZYNQ中继续使用,版本是AXI4,ZYNQ内部设备都有AXI接口。AXI4-Lite则是AXI4的一个简化版本,实现AXI4运行起来的最少接口

2019-05-06 16:55:32

读写分离的设计在Axi4总线中,读和写通道是完全相互独立,互不干扰。故而无论是在设计Decoder还是Arbiter时,均可以采用读写分离的方式。如前文所述,SpinalHDL在基于Axi4总线

2022-08-03 14:27:09

。writeIssuingCapability:指明AXI4总线写最大同时支持的指令个数。combinedIssuingCapability:其值应不小于前两者,用于在AXI4总线读写地址通道共用的场景

2022-08-02 14:28:46

microblaze通过串口读写FPGA内部axi4总线上的寄存器

2020-12-23 06:16:11

Xilinx ISE Design Suite 12.4 现在将更好地帮助您全面提升和改进设计。

Spartan-6 FPGA 将静态功耗削减 30%,性能提升 12%

AMBA 4 AXI4 工具和 IP 支持现已开始投产,可满足即插即用

2010-12-23 21:55:07 1310

1310 目的是利用嵌入在Xilinx FPGA中的MicroBlaze核实现基于AXI总线的双核嵌入式系统设计以及共享实现LED灯的时控.

2012-03-09 14:17:01 91

91 Xilinx的视频的IP CORE 一般都是 以 AXI4-Stream 接口。 先介绍一下, 这个IP的作用。 下面看一下这个IP 的接口: 所以要把标准的VESA信号 转为

2017-02-08 08:36:19 886

886

的FPGA开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。在ZYNQ中继续使用,版本是AXI4,所以我

2017-02-08 18:34:11 339

339

基于AXI4Stream总线协议,在Xilinx公司提供的FPGA上实现了一个具有缺陷像素校正、色彩滤波阵列插值、图像降噪实时图像采集与显示功能的视频系统。AXI4Stream总线协议由ARM公司

2017-11-17 08:58:01 5344

5344 1、AXI 总线通道,总线和引脚的介绍 AXI接口具有五个独立的通道: (1)写地址通道(AW):write address channel (2)写数据通道( W): write data

2018-01-05 08:13:47 11271

11271

;樊博等使用UI接口,DDR3通信的最大带宽可达3.8 Gb/s;张宇嘉等设计的基于AXI4的DDR3多端口方案虽然传输速率有所提高,但由于AXI4协议本身的复杂性增加了开发使用的难度。本文实现并验证了

2018-08-01 15:25:11 3972

3972

AXI是ARM在1996年提出的微控制器总线家族AMBA中的一部分。AXI是高级扩展接口,在AMBA3.0中提出,AMBA4.0将其修改升级为AXI4.0。AMBA4.0 包括: AXI4:主要面向

2018-10-02 07:09:09 1518

1518 AXI总线是一种多通道传输总线,将地址、读数据、写数据、握手信号在不同的通道中发送,不同的访问之间顺序可以打乱,用BUSID来表示各个访问的归属。主设备在没有得到返回数据的情况下可发出多个读写操作。读回的数据顺序可以被打乱,同时还支持非对齐数据访问。

2019-12-19 10:02:05 6029

6029 AXI-4 Memory Mapped也被称之为AXI-4 Full,它是AXI4接口协议的基础,其他AXI4接口是该接口的变形。总体而言,AXI-4 Memory Mapped由五个通道构成,如下图所示:写地址通道、写数据通道、写响应通道、读地址通道和读数据通道。

2020-09-23 11:20:23 6924

6924

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite或

2020-09-24 09:50:30 7201

7201

对于地址递增或地址循回的猝发,并且要求传输数据的宽度比数据总线上的要窄,这中猝发过程中,每次数据传输,使用不同的字节通道,这些通道对应于猝发中每一个时钟节拍。一个固定格式的猝发,其地址保持不变,每拍数据传输都使用相同的字节通道。

2020-09-24 10:29:53 21669

21669

在FPGA程序设计的很多情形都会使用到AXI接口总线,以PCIe的XDMA应用为例,XDMA有两个AXI接口,分别是AXI4 Master类型接口和AXI-Lite Master类型接口,可通过

2020-10-30 12:32:37 5116

5116

新的赛灵思器件设计中不可或缺的一部分。充分了解其基础知识对于赛灵思器件的设计和调试都很有帮助。 本篇博文将介绍赛灵思器件上的 AXI3/AXI4 的相关基础知识。首先,我们将从一些通俗易懂的知识、理论

2020-09-27 11:06:45 7722

7722

ZYNQ中DMA与AXI4总线 为什么在ZYNQ中DMA和AXI联系这么密切?通过上面的介绍我们知道ZYNQ中基本是以AXI总线完成相关功能的: 图4‑34连接 PS 和 PL 的 AXI 互联

2020-11-02 11:27:51 5032

5032

本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

2021-03-17 21:40:29 25

25 AXI是个什么东西呢,它其实不属于Zynq,不属于Xilinx,而是属于ARM。它是ARM最新的总线接口,以前叫做AMBA,从3.0以后就称为AXI了。

2021-04-09 17:10:10 7245

7245

本文介绍了AMBA 3.0 AXI的结构和特点,分析了新的AMBA 3.0 AXI协议相对于AMBA 2. 0的优点。它将革新未来高性能SOC总线互连技术,其特点使它更加适合未来的高性能、低延迟

2021-04-12 15:47:39 28

28 学习内容 近期设计需要用到AXI总线的IP,所以就对应常用的IP进行简要的说明,本文主要对AXI互联IP进行介绍。 基础架构IP 基础的IP是用于帮助组装系统的构建块。基础架构IP往往是一个通用IP

2021-05-11 14:52:55 7870

7870

AXI总线学习AXI协议的主要特征主要结构通道定义读写地址通道读数据通道写数据通道写操作回应信号接口和互联寄存器片基本传输Read burstOverlapping read burstWrite

2021-12-05 16:21:03 5

5 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文...

2022-02-07 11:36:33 4

4 XI4-Stream跟AXI4的区别就是AXI4-Stream去除了地址线,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时。由于AXI4-Stream协议(amba4_axi4_stream_v1_0_protocol_spec.pdf)没有时序图,

2022-06-23 10:08:47 3052

3052 AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解

2022-07-04 09:40:14 10523

10523 本文主要介绍了AXI通道以及在每个通道下信号的概述。

2022-08-04 10:49:17 12560

12560 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

2022-08-29 14:58:44 2981

2981 AXI (高性能扩展总线接口,Advanced eXtensible Interface)是ARM AMBA 单片机总线系列中的一个协议,是计划用于高性能、高主频的系统设计的。AXI协议是被优化

2022-10-10 09:22:22 11273

11273 Xilinx vivado下通常的视频流设计,都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read -->

2022-10-11 14:26:03 7574

7574 上面两图的区别是相比AXI3,AXI4协议需要确认AWVALID、AWREADY握手完成才能回复BVALID。为什么呢?

2023-03-30 09:59:49 1851

1851 AXI4 协议定义了五个不同的通道,如 AXI 通道中所述。所有这些通道共享基于 VALID 和 READY 信号的相同握手机制

2023-05-08 11:37:50 2039

2039

上文FPGA IP之AXI4协议1_协议构架对协议框架进行了说明,本文对AXI4接口的信号进行说明。

2023-05-24 15:05:46 2767

2767

上文FPGA IP之AXI4协议1_信号说明把AXI协议5个通道的接口信息做了说明,本文对上文说的信号进行详细说明。

2023-05-24 15:06:41 2083

2083

AXI4协议是ARM的AMBA总线协议重要部分,ARM介绍AXI4总线协议是一种性能高,带宽高,延迟低的总线协议。

2023-06-19 11:17:42 5676

5676

从 FPGA 应用角度看看 AMBA 总线中的 AXI4 总线。

2023-06-21 15:21:44 3091

3091

AXI4:高性能内存映射需求(如读写DDR、使用BRAM控制器读写BRAM等),为了区别,有时候也叫这个为 AXI4-Full;

2023-06-25 16:23:14 2574

2574

外部存储器接口( EMIF )通信常用于FPGA和DSP之间的数据传输,即将FPGA作为DSP的外部SRAM、或者协同处理器等。Xilinx提供了AXI-EMC IP核,将其挂载到AXI总线用于

2023-08-31 11:25:41 11848

11848

本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

2023-09-01 16:20:37 7275

7275

以AXI4为例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种: •AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 2142

2142

基于vivado2020.1和zcu102开发板(rev1.1)开发项目,工程涉及DDR4(MIG)和PL端多个读写接口交互的问题,通过AXI interconnect进行互联和仲裁(采用默认配置)。

2023-12-01 09:04:23 2380

2380

在介绍AXI之前,先简单说一下总线、 接口 以及协议的含义 总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。 总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由

2023-12-16 15:55:01 1876

1876 本文主要集中在AMBA协议中的AXI4协议。之所以选择AXI4作为讲解,是因为这个协议在SoC、IC设计中应用比较广泛。

2024-01-17 12:21:22 4273

4273

Transaction Layer的所有功能特性,不仅内置DMA控制器,而且具备AXI4用户接口,提供一个高性能,易于使用,可定制化的PCIe-AXI互连解决方案,同时适用于ASIC和FPGA。

2024-02-21 15:15:03 2109

2109

AXI总线由一些核心组成,包括AXI主处理器接口(AXI4)、AXI处理器到协处理器接口(AXI4-Lite)、AXI主外设接口(AXI4)、AXI外设到主处理器接口(AXI4-Lite)等。

2024-04-18 11:41:39 2500

2500 AXI4和AXI3是高级扩展接口(Advanced eXtensible Interface)的两个不同版本,它们都是用于SoC(System on Chip)设计中的总线协议,用于处理器和其它外设之间的高速数据传输。

2024-05-10 11:29:50 13096

13096

NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用高性能、顺序

2024-07-18 09:17:19 1440

1440

AMBA AXI4(高级可扩展接口 4)是 ARM 推出的第四代 AMBA 接口规范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 凭借半导体产业首个符合 AXI4 标准的即插即用型 IP 进一步扩展了 AMD 平台设计方法。

2024-10-28 10:46:42 1383

1383

NVMe需要用AXI总线进行高速传输。而AXI总线是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)协议中的重要组成部分,主要面向高性能、高带宽、低延时的片内互连需求。这里简要介绍AXI总线区别,以及读写架构基本原理

2025-05-21 09:29:51 658

658

AXI4 总线是第四代 AXI 总线,其定义了三种总线接口,分别为:AXI4、AXI4-Lite 和 AXI4-Stream接口。其中 AXI4 也称为 AXI4-Full 是一种基于地址的高性能

2025-06-24 23:22:33 523

523

电子发烧友App

电子发烧友App

评论