概述

外部存储器接口( EMIF )通信常用于FPGA和DSP之间的数据传输,即将FPGA作为DSP的外部SRAM、或者协同处理器等。Xilinx提供了AXI-EMC IP核,将其挂载到AXI总线用于EMIF通信,也可方便地实现 PL (FPGA)和 PS (MicroBlaze或者ARM)之间的数据交互功能。

本文主要介绍一下该IP核的使用,以及创建Vivado工程对EMIF通信功能进行板上测试。

软硬件平台

软件平台 :Vivado 2017.4;

硬件平台 :xc7a35tftg256-1;

AXI-EMC

功能特性

AXI-EMC IP核是一种可以支持各种型号内存的控制器,和EMIF接口类似,利用它可以实现数据的交互和通信。该IP核有以下功能特性:

- 接口采用AXI4 Slave Memory Map,位宽支持32、64bits;

- 支持AXI4增量和包传输,支持窄带和非对其传输;

- 最多支持4个外部存储器;

- 支持奇偶校验和流水线级同步SRAM等;

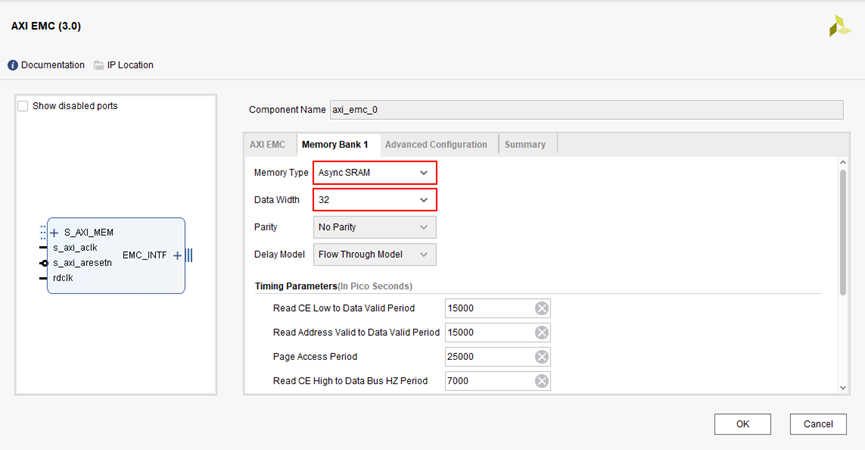

参数配置

- AXI Data Width:AXI总线位宽选择32位;

- Number of Memory Banks:存储器个数这里选择1即可;

- AXI ID位宽和存储空间地址选择默认配置;

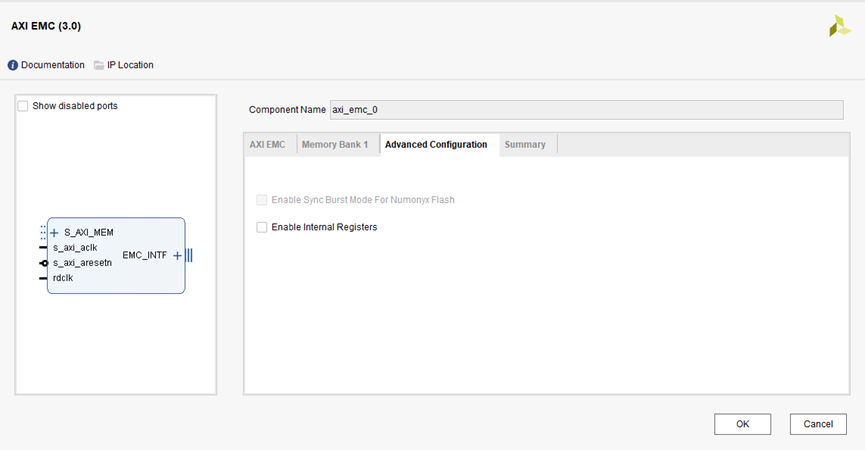

- Advanced Configuration:高级配置选项保持默认,不用配置IP核内部寄存器;

Vivado工程创建

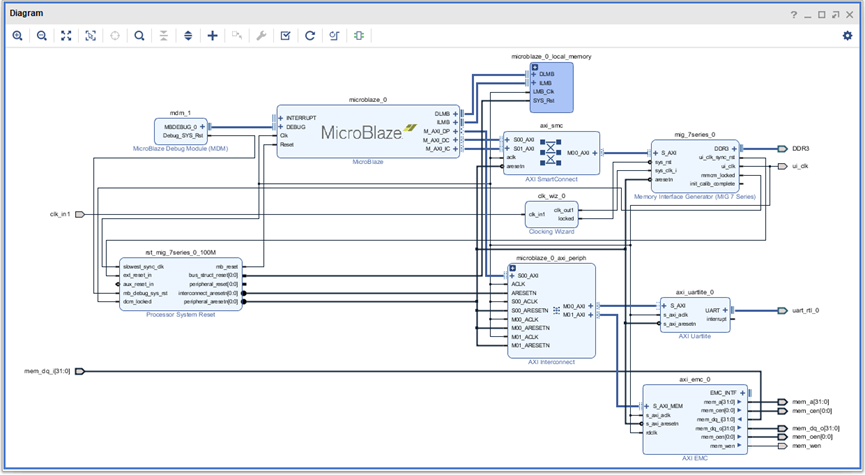

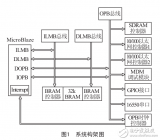

本工程是在MicroBlaze最小系统工程基础上进行创建,利用AXI-EMC在MicroBlaze软核端对FPGA端进行EMIF数据读写,进而实现PS和PL端数据交互功能。

搭建Block Design

- 在MicroBlaze最小系统的Block Design工程中添加AXI-EMC IP核,并对参数进行配置;

- 将IP核的 rdclk 接口以及 s_axi_aclk 接口与MIG IP提供的100MHZ用户时钟接口 ui_clk 进行连接;

- 将 mem_a (地址)、 mem_cen (片选)、 mem_dq_o (输出数据)、 mem_dq_i (输入数据)、 mem_oen (读使能)、 mem_wen (写使能)接口引出,在顶层文件中会进行调用。

最终搭建完成的Block Design如下图所示:

修改顶层文件

在生成的顶层文件中添加以下代码,用于实现FPGA端基本的EMIF通信功能,以及添加ILA模块实现对EMIF接口信号的实时观察。

reg [31:0] data_reg,mem_dq_i_reg;

reg [2:0] mem_wen_r,mem_oen_r;

assign mem_dq_i = mem_dq_i_reg;

always@(posedge ui_clk) begin

mem_wen_r <= {mem_wen_r[1:0],mem_wen};

mem_oen_r <= {mem_oen_r[1:0],mem_oen};

end

always@(posedge ui_clk)

if(mem_wen_r[2:1] == 2'b10) begin

case(mem_a[17:2])

16'h5555:

data_reg <= mem_dq_o;

default:

data_reg <= data_reg;

endcase

end

always@(posedge ui_clk)

if(mem_oen_r[2:1] == 2'b10) begin

case(mem_a[17:2])

16'haaaa:

mem_dq_i_reg <= data_reg;

default:

mem_dq_i_reg <= mem_dq_i_reg;

endcase

end

ila_0 ila_0_u0

(

.clk (ui_clk),

.probe0 (mem_a),

.probe1 (mem_cen),

.probe2 (mem_dq_i),

.probe3 (mem_dq_o),

.probe4 (mem_oen),

.probe5 (mem_wen),

.probe6 (uart_rtl_0_txd)

);

创建SDK工程

在SDK软件中,采用Xilinx提供的Hello World工程,在helloworld.c文件中添加以下代码,用于实现MicroBlaze软核每隔一定时间在FPGA端0x55554地址下写入32位十进制数据:111,并从0xaaaa4地址将该数据读出。

#include < stdio.h >

#include "platform.h"

#include "xil_io.h"

#include "xparameters.h"

#include "xuartlite.h"

#include "xuartlite_l.h"

int ii,data;

int main()

{

init_platform();

print("EMIF TESTnr");

while(1)

{

Xil_Out32(XPAR_EMC_0_S_AXI_MEM0_BASEADDR+0x5555*4,111);

data=Xil_In32(XPAR_EMC_0_S_AXI_MEM0_BASEADDR+0xaaaa*4);

for(ii=0;ii< 100;ii++);

}

cleanup_platform();

return 0;

}

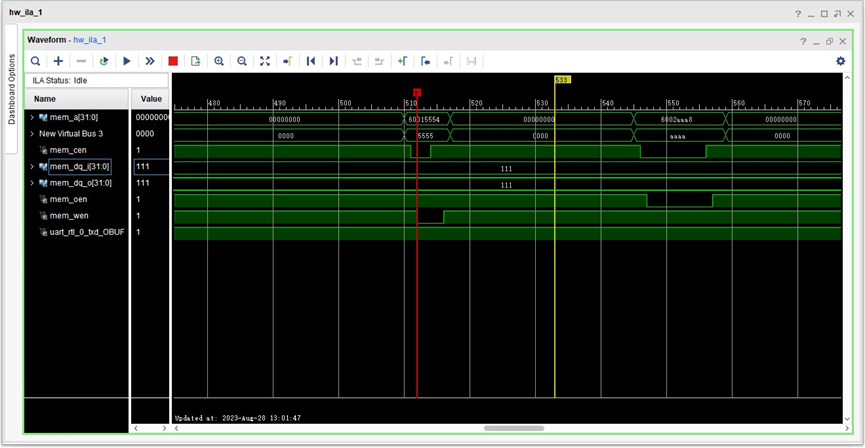

功能测试

该Vivado工程利用AXI-EMC IP核实现异步SRAM接口,在MicroBlaze软核CPU和FPGA之间进行基础的EMIF通信。该工程为实现PS和PL之间的数据交互功能提供一种很好的思路。

FPGA板上测试结果如上图所示,MicroBlaze软核往FPGA 0x55554地址下写入32位十进制数据111,FPGA将该数据进行寄存,供软核从0xaaaa4地址下读出。

-

处理器

+关注

关注

68文章

20336浏览量

255065 -

dsp

+关注

关注

561文章

8276浏览量

368311 -

FPGA

+关注

关注

1664文章

22504浏览量

639341 -

存储器

+关注

关注

39文章

7757浏览量

172210 -

通信

+关注

关注

18文章

6453浏览量

140270 -

Xilinx

+关注

关注

73文章

2208浏览量

131926

发布评论请先 登录

Xilinx zynq AXI总线全面解读

XILINX FPGA IP之AXI Traffic Generator

请教DSP的EMIF总线和ARM的AXI总线转换的问题

请问KC705上的AXI EMC核心硬件测试例子哪里可以找到?

AXI 代码 不通过 AXI Protocol Checker IP 的检测

使用EMIF将Xilinx FPGA与TI DSP平台接口

Xilinx的LogiCORE IP Video In to AXI4

基于TCP/IP通信技术在Xilinx FPGA上的实现

基于Xilinx FPGA AXI-EMC IP的EMIF通信测试

基于Xilinx FPGA AXI-EMC IP的EMIF通信测试

评论