在FPGA程序设计的很多情形都会使用到AXI接口总线,以PCIe的XDMA应用为例,XDMA有两个AXI接口,分别是AXI4 Master类型接口和AXI-Lite Master类型接口,可通过M_AXI接口对数据进行读取操作,此时设计一个基于AXI-Slave接口的IP进行数据传输操作就非常的方便。

封装的形式并不复杂,只是略微繁琐,接下来一步一步演示如何封装AXI_SLAVE接口IP:

1、创建工程

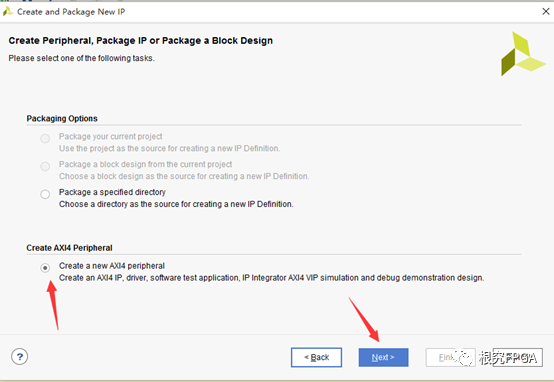

2、选择Create AXI4 Perpheral,点击next

设置保存路径,也可默认:

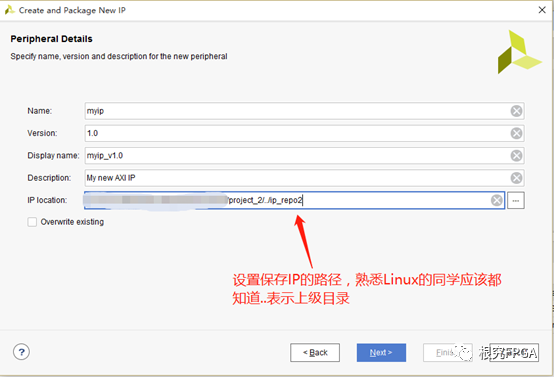

3、设置保存路径:

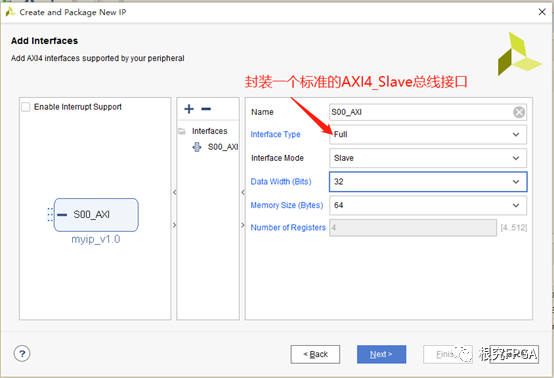

4、设置封装的接口类型:

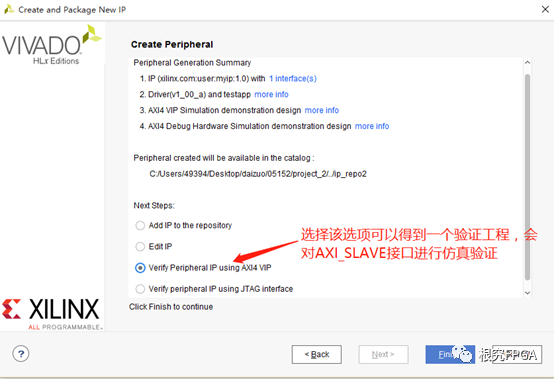

5、选择Verify Peripheral IP using AXI4 IP

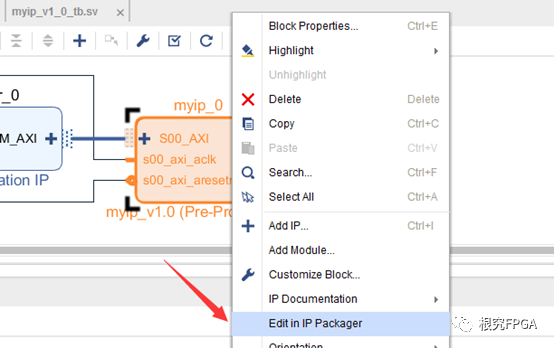

6、对IP进行修改:

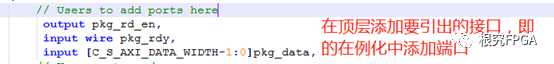

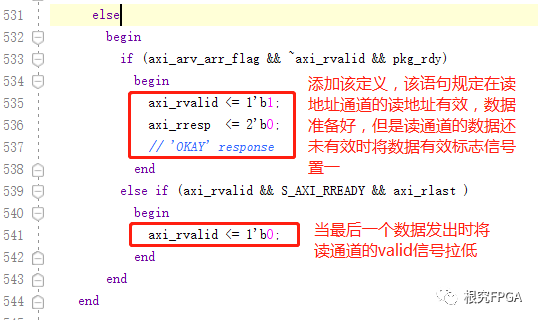

在S00_AXI.v中编辑:

7、保存工程

如果不慎将初始的IP封装界面关掉的话,在Tools下选择Create and Package New IP,选择Package your current project,NEXT之后选择open(你会看到的)。

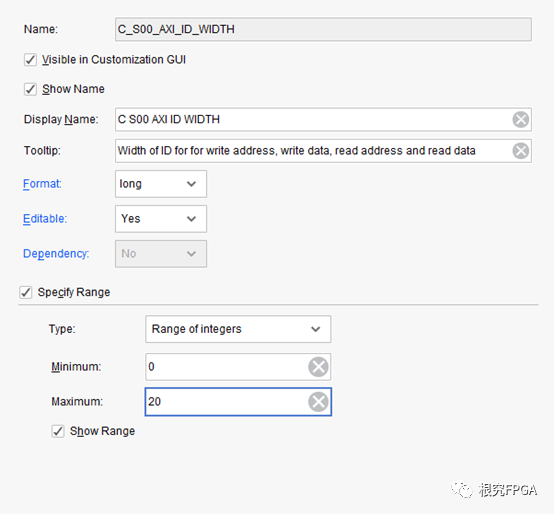

设置ID位宽,该选项主要用于outstanding传输:

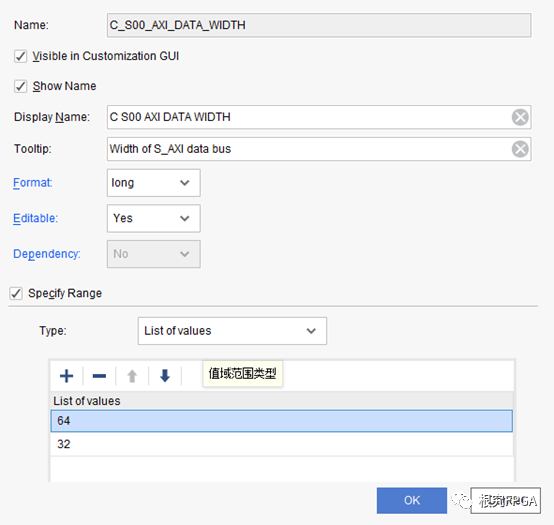

设置数据位宽,根据需要自行设计:

如果出现Merge提示的话,点击,选择覆盖参数。

最后选择重新封装IP,就得到属于自己的AXI_SLAVE接口IP啦!

在刚刚设置的ip_repo2文件目录下可以看到IP:

编辑:hfy

-

FPGA

+关注

关注

1664文章

22504浏览量

639302 -

AXI

+关注

关注

1文章

145浏览量

18020

发布评论请先 登录

利用开源uart2axi4实现串口访问axi总线

RDMA设计6:IP架构2

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

NVMe高速传输之摆脱XDMA设计43:如何上板验证?

将e203 例化AXI总线接口

VDMA IP核简介

AXI GPIO扩展e203 IO口简介

RDMA over RoCE V2设计2:ip 整体框架设计考虑

NVMe IP之AXI4总线分析

NVMe控制器IP设计之接口转换

智多晶eSPI_Slave IP介绍

FPGA程序设计:如何封装AXI_SLAVE接口IP

FPGA程序设计:如何封装AXI_SLAVE接口IP

评论