AXI4和AXI3是高级扩展接口(Advanced eXtensible Interface)的两个不同版本,它们都是用于SoC(System on Chip)设计中的总线协议,用于处理器和其它外设之间的高速数据传输。以下是它们之间的一些主要区别:

1.AXI4加大Burst Length

AXI3最大突发长度(Burst Length)是16 beats,其AxLEN信号位宽为4位。

AXI4扩展了对突发长度的支持,最大可以达到256 beats,AxLEN信号位宽增加到8位。注意,这种扩展主要是针对INCR(Incrementing)突发类型,而WRAP和FIXED突发类型的最大长度仍然限制在16 beats,并且CPU的突发一般不会超过16拍,突发太长会一直占用总线,而且一旦开始突发传输是不能取消的,只能等突发传输完成。

注意,大型SoC系统中,AXI4和AXI3往往混用,如果总线从AXI4转为AXI3实len直接从[7:0]截位为[3:0],则需要控制源头激励,len不能大于15。否则会无响应进而挂死,推荐使用协议桥来完成转换。

2. AXI4新增QoS

AXI4引入了新的信号来支持服务质量(QoS),例如4bit的AWQOS和4bit的ARQOS信号,这些信号允许系统根据事务的重要性分配不同的服务级别。主要针对不同写/读事务的优先级,如果不使用,建议设置为default value 4'b0000。

AXI4协议没有规定QoS的用法,一般由具体SoC架构特性决定,协议中希望互联组件中有可配置寄存器,在传输中可以修改Qos信号值。一般尽量在系统级统一规划QoS,并且设置为可编程QoS。QoS值越大,优先级越高,当然也有AxQoS越低,优先级越高的SoC。

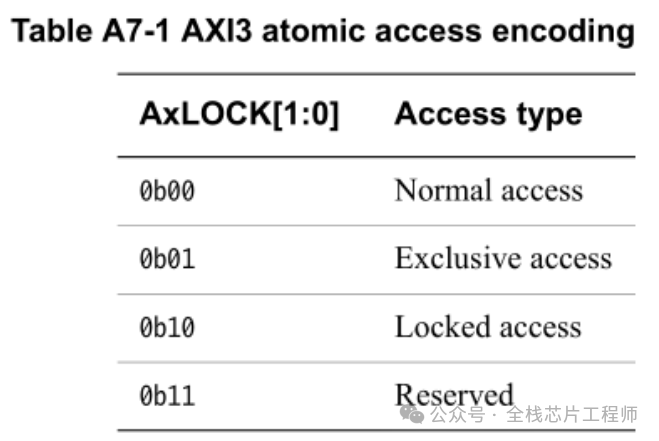

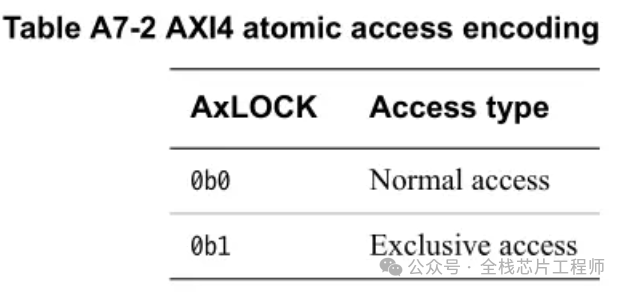

3.AXI4取消锁定事务

AXI4去除了对锁定事务的支持,这是为了提高协议的简洁性。在AXI3中,锁定事务允许一个主设备锁定对从设备的访问,直到它完成其事务。AXI4中,AxLOCK信号从2位减少到了1位,不再支持Locked access,只支持Normal access、Exclusive access。请问,Locked access和Exclusive access区别是啥?

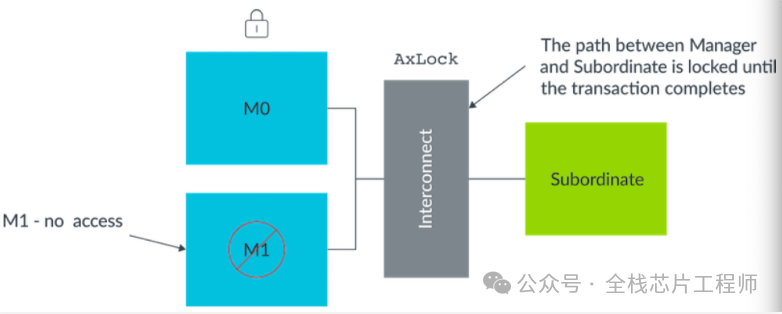

请问,什么是locked access?

答:a locked sequence of transcations forces the interconnect to reject access to subordinate from any orther manager。即强制interconnect 拒绝其他master访问subordinate(slave)。

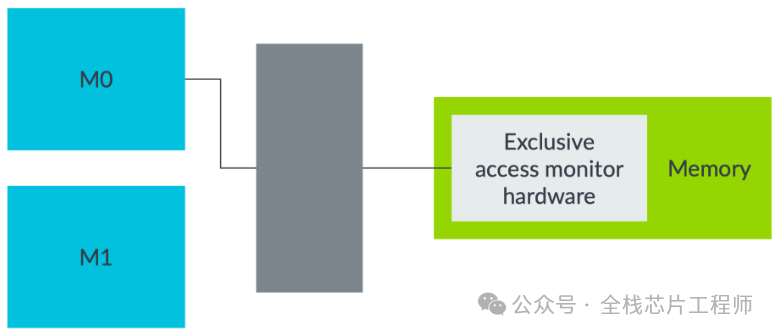

如上图,当M0发起locked access的时候,必须确保没有在途的transaction,之前的transaction必须完成。然后M0使用AxLOCK发起locked transaction,然后interconnect通过内部仲裁器确保只有M0能访问到subordinate,任何其他的manager(M1)访问Sub都会被Blocked,直到M0发起一个非locked transaction表示locked sequence完成。

因此,Locked access作用的对象是总线,而Exclusive access 作用的对象是对应的Slave。现在SoC系统都非常复杂,Master也非常多,某一个Master lock住总线导致其他master不能使用总线对系统的性能影响太大,AXI4就取消Lock机制了。而Exclusive access机制实现在Slave模块里,支持Exclusive access机制的slave会实现一个Exclusive access Monitor。

什么是Exclusive access Monitor?

当M0发起一次独占访问读操作后,subordinate中的monitor会有如下可能响应。

EXOKAY:读操作已经执行,独占访问成功,并且事务ID已经记录下,memory range和manager已经记录下。

OKAY:读操作已经执行,但是subordinate不支持独占访问,独占访问错误。

如果当M0接受到EXOKAY的响应,那么M0可以尝试完成exclusive sequence,即进行一次独占写,这次独占写需要有相同的事务ID以及相同的地址范围。接下来可能接受到来自subordinate的响应为:

EXOKAY:没有其他manager对先去读事务的地址范围进行写操作,所以M0的独占写事务成功,在这种情况下,独占写事务更新了memory。

OKAY:有别的manager,例如M1,在M0发起写事务之前已经对独占地址范围进行了写操作,独占写失败。

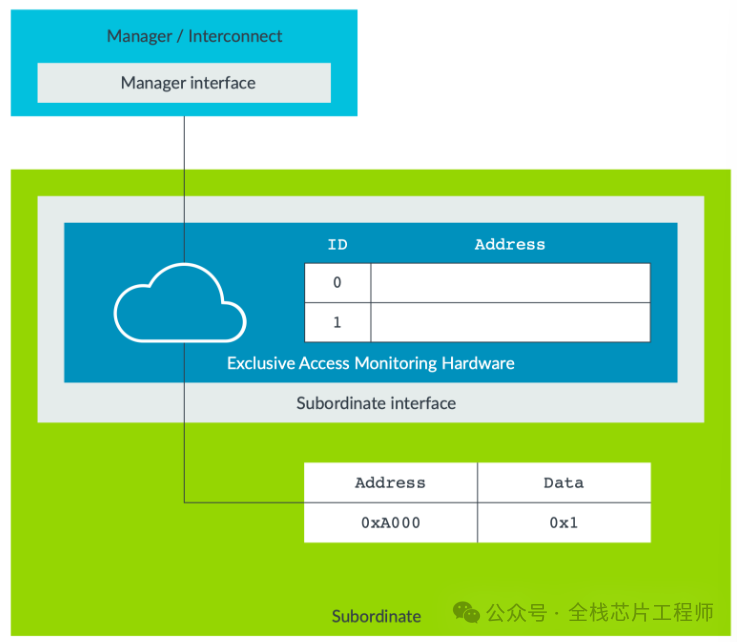

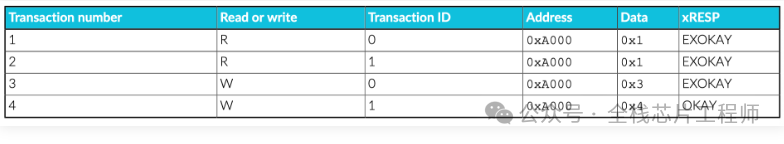

要实现exclusive access,需要每个transaction ID都记录一个地址,用来标记不同序列的独占访问地址。举个例子,如下图:

当manager发起两笔独占访问,第一笔独占访问transaction ID是0,第二笔是1,对相同的独占访问地址进行读操作,subordinate都会给出EXOKAY的响应,因为该subordinate支持独占访问操作,并且读操作成功执行。

然后manager发送一笔写事务,transaction ID是0,然后subordinate检查该笔transaction ID是否记录在monitor中,检查后发现该地址被记录在monitor的table中,因此独占访问写操作成功,返回EXOKAY响应,同时由于地址0xA000已经被写入修改了,monitor将所有地址为0xA000的独占记录移除。

然后manager再次发送一笔写事务,transaction ID为1,此时monitor再次检查内部的独占记录发现没有独占记录,因为在上一个exclusive sequence已经清除掉所有地址为0xA000的独占记录了,因此独占写事务失败,返回OKAY,并且内存中的数据不会更新,也就是data 0x4并不会写入到地址中。

这个例子演示了独占访问如何实现非阻塞行为。与LOCK访问相比,提供了更大的系统吞吐量。

4.AXI4S升级AxCACHE

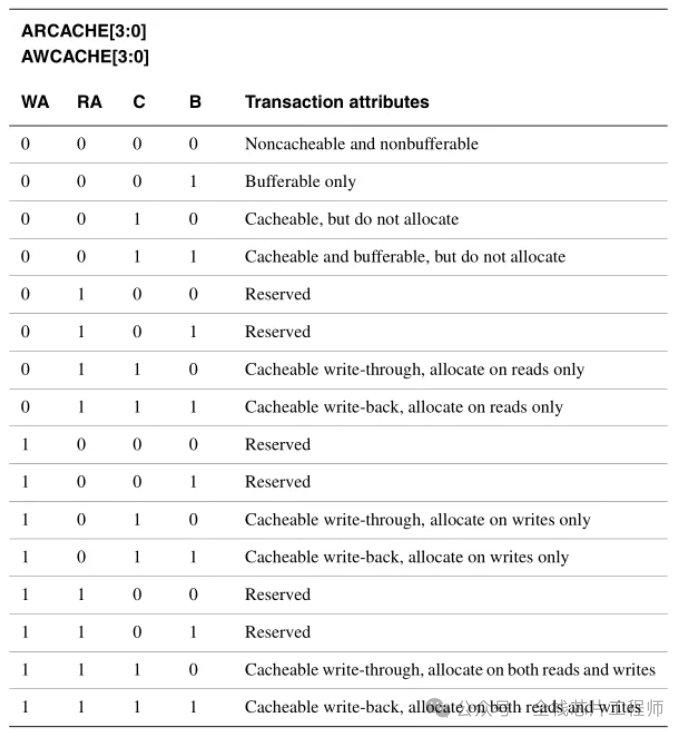

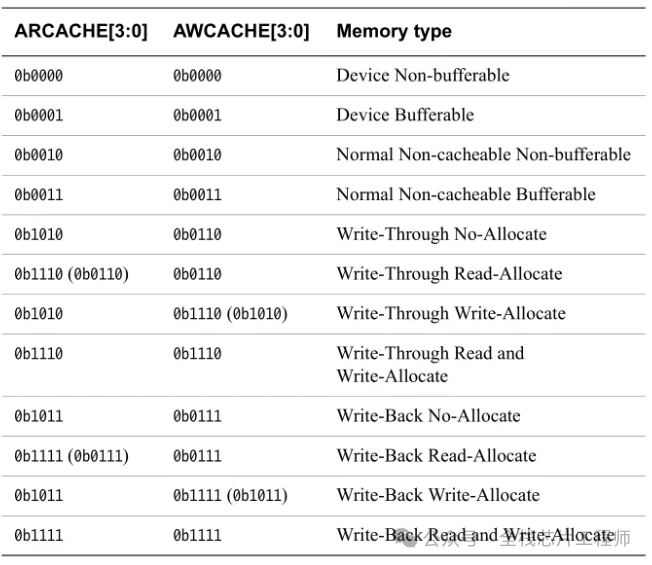

AXI4中AWCACHE和ARCACHE信号的含义发生了变化,以适应ARM CPU架构的发展和对内存属性更复杂的定义。

在AXI3中,4bit数据分别是buffer、cache、read allocate、write allocate。

bufferable用在写操作中,表示可以由一个中间节点来返回response信号。Normally, the Bufferable attribute is only relevant to writes.

cacheable在读操作中,表示可以prefetch一些数据,在写操作中,表示可以将不同的write merged together。RA针对读操作。WA针对写操作。只有在cacheable有效的情况下,这两个bit才有效。在AXI4中,cache bit改名为modefiable,RA,WA的概念被更新,将不用的allocate bit改为other allocate。

AXI3 中AWCACHE[3:0] 和ARCACHE[3:0]的含义如下图所示:

AXI3中cache=0,对数据不做处理。cache=1,矩阵会对读写数据进行合并或拆分处理。一般是矩阵的downsize/upsize对数据进行处理。cache[0],Bufferable,一般针对写操作,表示interconnect,或者其他类似component,可以先返回resp,之后再写向final distination。cache[1],1)与RA,WA配合,控制cache。2)表示transaction的属性,可以在中间被更改。对写操作,表示数据可以被merge。对于读操作,表示地址可以被prefetch。

AXI4中AWCACHE[3:0] 和ARCACHE[3:0]的含义如下图所示(括号内的是AXI3的编号):

5. AXI4升级写响应(Write Response Channel)

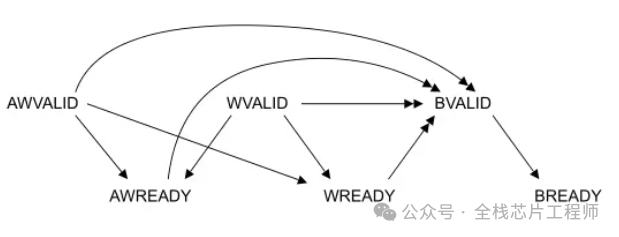

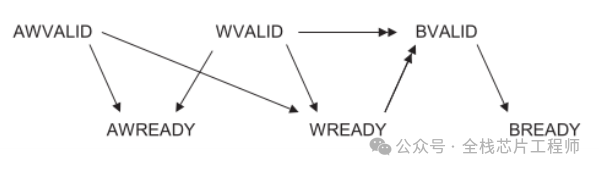

AXI4规定了更严格的写响应条件,必须等到地址通路和数据通路都准备好,并且明确了要等WLAST信号后,从设备才能发出BVALID进行写响应,这保证了事务真正完成时才发送响应。也就是说AXI4必须等到AWVALID,AWREADY,WVALID, WREADY, and WLAST 都为高后,SLAVE才能发BVALID进行写响应,进一步避免了deadlock。

AXI3则是等到了WVALID和WREADY后就能把BVALID置高来响应,也就是说只要slave接收了W通道所有写数据(WLAST拉起)就可以B通道响应,没管地址通道,SLAVE就可以发写响应。显然AXI4更严谨。

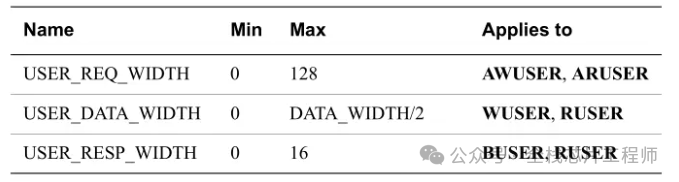

6.AXI4升级AxUSER

在AXI3中,USER信号没有具体规定,而在AXI4中,USER信号的位宽和用法被进一步定义和标准化,以支持更广泛的应用。考虑到IP的兼容性问题,IP厂商一般不用USER信号,其主要还是应用在SoC内部。AXI4的USER信号规定如下:

AXI4在写控制通道、写数据通道、写反馈通道和读控制通道中引入了额外的用户自定义信号,如AWUSER、WUSER、BUSER、ARUSER和RUSER,以支持更广泛的应用场景。考虑到IP的兼容性问题,IP厂商一般不用USER信号,其主要还是应用在SoC内部。

AXI4在写控制通道、写数据通道、写反馈通道和读控制通道中引入了额外的用户自定义信号,如AWUSER、WUSER、BUSER、ARUSER和RUSER,以支持更广泛的应用场景。考虑到IP的兼容性问题,IP厂商一般不用USER信号,其主要还是应用在SoC内部。

7.AXI4取消WID

AXI4取消WID,写通道不再支持write data interleave功能,虽然AXI3支持Write interleaving,但是大家在设计的时候,master基本都没支持Write interleaving,因为写数据一般都是in order有序发送的。这样可以减少pin count,减少设计复杂度。

8.AXI4新增AxREGION

相比AXI3,AXI4增加了2个4bit AxREGION信号,4bit可以表示16个region。主要作用是简化slave中的address decode,由interconnect在做address decode时产生,同样必须在4k范围内。AxREGION是可选的功能,一般用的较少。

总结,AXI4和AXI3在互联时需要注意信号的兼容性,例如AWID、AxLOCK、AxLEN等信号的处理方式有所不同。

审核编辑:刘清

-

处理器

+关注

关注

68文章

20148浏览量

247106 -

寄存器

+关注

关注

31文章

5589浏览量

129057 -

数据传输

+关注

关注

9文章

2076浏览量

67172 -

SoC系统

+关注

关注

0文章

52浏览量

11144 -

AXI总线

+关注

关注

0文章

68浏览量

14717

原文标题:SoC系统中AXI4与AXI3兼容性与exclusive access

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

看看在SpinalHDL中AXI4总线互联IP的设计

学习架构-AMBA AXI简介

何谓 AXI?关于AXI3/AXI4的相关基础知识

深入AXI4总线一握手机制

AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI3与AXI4写响应的依赖区别

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】

SoC设计中总线协议AXI4与AXI3的主要区别详解

SoC设计中总线协议AXI4与AXI3的主要区别详解

评论