NVMe需要用AXI总线进行高速传输。这里,AXI总线是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)协议中的重要组成部分,主要面向高性能、高带宽、低延时的片内互连需求。AXI4总线则是AXI总线的第四代版本,主要包含三种类型的接口,分别是面向高性能地址映射通信的AXI4接口、面向轻量级单次地址映射通信的AXI4-Lite接口和面向高速数据流传输的AXI4-Stream接口。如表1所示展示了三种类型接口的主要特点对比。

表1 三种类型AXI4接口对比

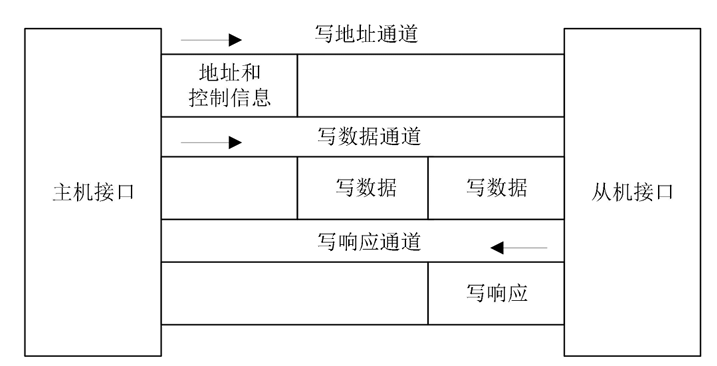

AXI4总线具有读写地址、数据通道分离的特性,使控制通道与数据通道分离、读通道与写通道分离,从而具有并行处理的能力,大幅提高了总线传输带宽和传输效率。AXI4总线可分为写通道和读通道。写通道由写地址通道、写数据通道、写响应通道组成。写地址通道数据流从主机指向从机,主要传递地址和控制信息;写数据通道数据流从主机指向从机,主要传递数据信息;写响应通道数据流从从机指向主机,主要反馈写请求事务的响应信息。如图2所示为写通道组成结构。

AXI 写通道架构示意图

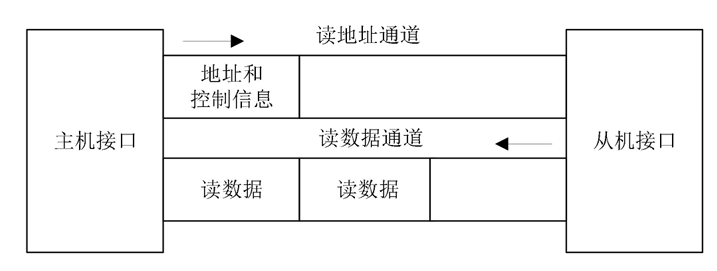

读通道与写通道有相似的结构,由读地址通道和读数据通道组成。读地址通道数据流从主机指向从机,实现地址和控制信息的传递;读数据通道数据流由从机指向主机,实现数据的传输。与写通道相比,读通道没有单独的响应通道,读响应信息包含在读数据通道中由从机反馈到主机。如图3所示为读通道组成结构。

图3 AXI 读通道架构

审核编辑 黄宇

-

接口

+关注

关注

33文章

9601浏览量

157628 -

总线

+关注

关注

10文章

3060浏览量

91869 -

AXI

+关注

关注

1文章

145浏览量

18020 -

nvme

+关注

关注

0文章

300浏览量

23914

发布评论请先 登录

NVMe简介之AXI总线

NVMe简介之AXI总线

评论