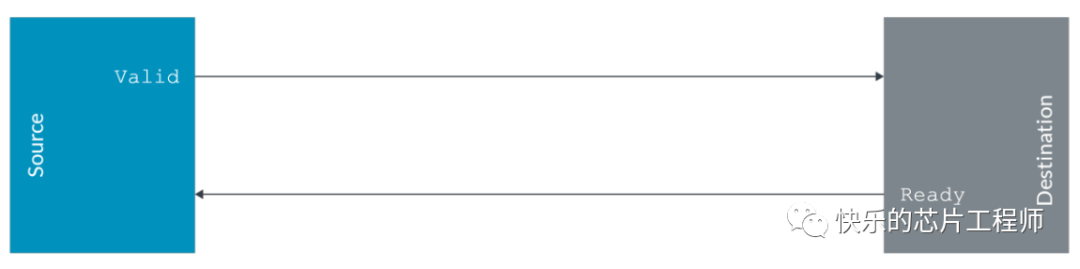

AXI4 协议定义了五个不同的通道,如 AXI 通道中所述。所有这些通道共享基于 VALID 和 READY 信号的相同握手机制,如下图所示:

VALID 信号从源到目标,READY 从目标到源。

源或目标是 manager 还是 subordinate 取决于正在使用的通道。例如,manager是读取地址通道的源,但是读取数据通道的目标。

源使用 VALID 信号来指示有效信息何时可用。VALID 信号必须保持断言,即设置为高电平,直到目的地接受该信息。以这种方式保持有效的信号称为粘性信号(sticky signals)。

目的地指示它何时可以使用 READY 信号接受信息。READY 信号从通道目标发送到通道源。

此机制不是异步握手,需要时钟的上升沿才能完成握手。

在设计互连结构时,您必须了解所连接的 manager 和subordinate的能力。了解此信息后,您就可以包含足够的缓冲、跟踪和解码逻辑,以支持各种数据传输排序的可能性,从而提高更快设备的性能。

使用标准术语可以更轻松地理解连接组件之间的交互。AXI 区分了传输和事务:

传输是一次信息交换,带有一次 VALID 和 READY 握手。

一个事务是一个完整的传输突发,包含一个地址传输、一个或多个数据传输,以及对于写序列,一个响应传输。

审核编辑:刘清

-

时钟

+关注

关注

11文章

2000浏览量

135275 -

axi协议

+关注

关注

0文章

8浏览量

2457

原文标题:【AXI--06】Channel handshake

文章出处:【微信号:快乐的芯片工程师,微信公众号:快乐的芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

NVMe IP之AXI4总线分析

【正点原子FPGA连载】第九章AXI4接口之DDR读写实验--摘自【正点原子】达芬奇之Microblaze 开发指南

看看在SpinalHDL中AXI4总线互联IP的设计

SoC Designer AXI4协议包的用户指南

AMBA 4 AXI4、AXI4-Lite和AXI4-流协议断言用户指南

深入AXI4总线一握手机制

AXI3与AXI4写响应的依赖区别

漫谈AMBA总线-AXI4协议的基本介绍

AMBA AXI4接口协议概述

AXI4协议五个不同通道的握手机制

AXI4协议五个不同通道的握手机制

评论