AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互连以及其他AXI4系统外设上生成特定序列(流量)。它根据IP的编程和选择的操作模式生成各种类型的AXI事务。是一个比较好用的AXI4协议测试源或者AXI外设的初始化配置接口。

ATG(AXI Traffic Generator)IP的GUI如下图所示。

AXI Traffic Generator是一个完全可综合的符合AXI4标准的核心,具有以下特点:

- 可根据不同的流量配置选项生成和接受数据。

- 可配置的主AXI4接口地址宽度。

- 支持读/写主端口之间的相关/独立事务,并具有可配置的延迟。

- 可编程的重复计数,对于每个事务可以使用恒定/递增/随机地址。

- 在AXI接口上为预定义的协议生成特定IP流量。

该IP的主要特性为:

- AXI4 接口适用于寄存器访问和数据传输;

- 支持多种模式工作(AXI4 Master,AXI4-Lite Master, and AXI4-Stream Master);

- 高度灵活的数据位宽:32/64/128/256/512 axistream:8-1024;

- 高度灵活的地址位宽:32-64;

- 可为处理器资源较少系统中的系统初始化提供 AXI4-Lite 主接口支持;

- 中断引脚,指示内核已完成流量生成;

- 错误中断引脚,指示内核工作期间出现的错误。可通过读取错误寄存器,了解所出现的错误;

- 内部 RAM(CMDRAM、PARAMRAM 和 MSTRAM)的初始化支持允许用户针对所需的流量特性分析初始化所有 RAM 的内容;

它支持6种工作模式:

如下图所示,在IP生成的时候可以在AXI4选项下选择Advanced、Basic、Static三种模式;

AXI4-Stream模式如下图所示:

如下图所示,在IP生成的时候AXI4-Lite选项可以选择System Init和Test Mode两种模式;

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22537浏览量

640181 -

寄存器

+关注

关注

31文章

5622浏览量

130542 -

接口

+关注

关注

33文章

9623浏览量

157726 -

Xilinx

+关注

关注

73文章

2208浏览量

132086 -

AXI

+关注

关注

1文章

145浏览量

18047

发布评论请先 登录

相关推荐

热点推荐

Xilinx zynq AXI总线全面解读

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使

ARM+FPGA开发:基于AXI总线的GPIO IP创建

FPGA+ARM是ZYNQ的特点,那么PL部分怎么和ARM通信呢,依靠的就是AXI总线。这个实验是创建一个基于AXI总线的GPIO IP,利用PL的资源来扩充GPIO资源。通过这个实验

XILINX FPGA IP之Clocking Wizard详解

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明

发表于 06-12 17:42

•9419次阅读

XILINX FPGA IP之MMCM PLL DRP时钟动态重配详解

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重

发表于 06-12 18:24

•1.8w次阅读

Xilinx FPGA IP之Block Memory Generator功能概述

Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

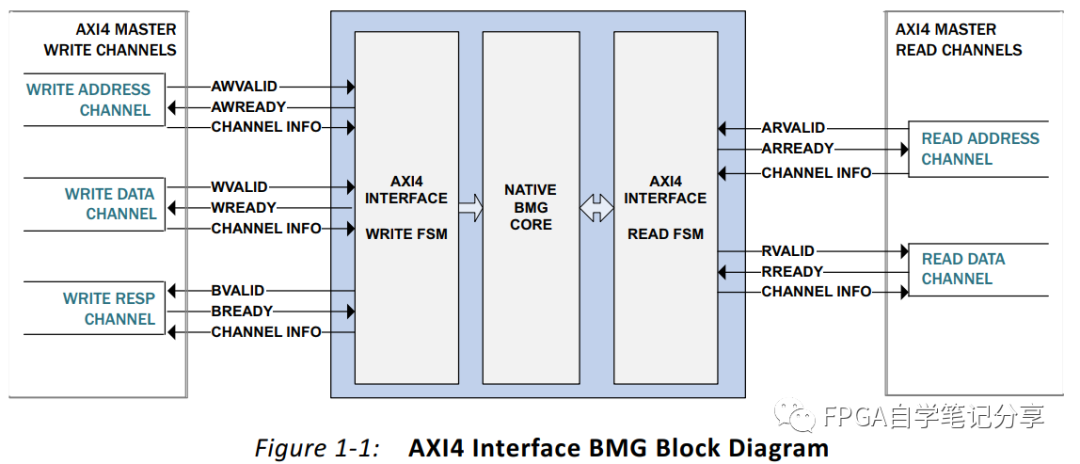

Xilinx FPGA IP之Block Memory Generator AXI接口说明

之前的文章对Block Memory Generator的原生接口做了说明和仿真,本文对AXI接口进行说明。

Xilinx FPGA片内ROM实例之ROM配置

Xilinx FPGA入门连载44:FPGA片内ROM实例之ROM配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

发表于 01-09 16:02

AXI 代码 不通过 AXI Protocol Checker IP 的检测

Checker IP 的检测呢 ? https://www.xilinx.com/support/documentation/ip_documentation/axi_protoco

发表于 02-28 13:44

Xilinx的LogiCORE IP Video In to AXI4

Xilinx的视频的IP CORE 一般都是 以 AXI4-Stream 接口。 先介绍一下, 这个IP的作用。 下面看一下这个IP 的接口

发表于 02-08 08:36

•930次阅读

FPGA开发之算法开发System Generator

的对应关系: System generator 安装之后会在Simulin模块库中添加一些Xilinx FPGA专用的模块库,包括Basic Element,Communication,Control

发表于 11-17 14:29

•9184次阅读

如何使用Xilinx AXI进行验证和调试

了解如何使用Xilinx AXI验证IP有效验证和调试AXI接口。

该视频回顾了使用的好处,以及如何使用示例设计进行模拟。

基于Xilinx FPGA AXI-EMC IP的EMIF通信测试

外部存储器接口( EMIF )通信常用于FPGA和DSP之间的数据传输,即将FPGA作为DSP的外部SRAM、或者协同处理器等。Xilinx提供了AXI-EMC

XILINX FPGA IP之AXI Traffic Generator

XILINX FPGA IP之AXI Traffic Generator

评论