AXI 总线是一种高速片内互连总线,其定义于由 ARM 公司推出的 AMBA 协议中,主要用于高性能、高带宽、低延迟、易集成的片内互连需求。AXI4 总线是第四代 AXI 总线,其定义了三种总线接口,分别为:AXI4、AXI4-Lite 和 AXI4-Stream接口。其中 AXI4 也称为 AXI4-Full 是一种基于地址的高性能传输接口,其支持乱序传输、突发传输等传输方式,同时通过独立的地址总线,实现高性能的数据地址映射;

AXI4-Lite 则在 AXI4 的基础上去掉了乱序传输、突发传输、Outstanding 等特性,主要用于简单的单次地址映射通信。而 AXI4-Stream 则为点对点连接总线,其去掉了地址总线,主要用于点对点间的高速数据流传输。三种接口的对比如表 1 所示:

表1 AXI4、AXI4-Lite 和 AXI4-Stream接口总线

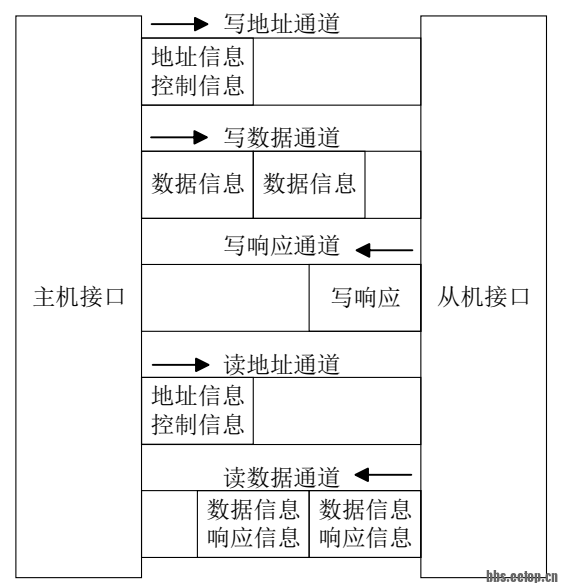

这里以功能完备的 AXI4 接口举例说明 AXI4 总线的相关特点。AXI4 总线采用读写通道分离且数据通道与控制通道分离的方式,这样的总线通道使其具有多主多从的连接特性和并行处理的能力,能够大幅提高总线的数据吞吐量。AXI4 总线共有五个通道。其中,写地址通道和写数据通道数据流由主机指向从机,分别用于发送地址信息和数据信息。写响应通道数据流由从机指向主机,用于反馈写指令的完成状态。

读通道与写通道类似,读地址通道由主机指向从机,用于发送地址信息和控制信息,读数据通道数据流由从机指向主机,用于从发送数据信息。但与写通道不同的是,读通道并没有响应通道,读响应信息包含在读数据通道中,与数据流一同反馈给主机。AXI4 总线的通道结构如图 1所示。

图1 AXI4 总线的通道结构图

相关视频感兴趣者,请搜B站用户名: 专注与守望

或链接:

https://space.bilibili.com/585132944/upload/video

审核编辑 黄宇

-

RDMA

+关注

关注

0文章

85浏览量

9558 -

AXI

+关注

关注

1文章

143浏览量

17791

发布评论请先 登录

RDMA设计5:RoCE V2 IP架构

RDMA设计4:技术需求分析2

RDMA设计2:开发必要性之性能简介

RDMA设计1:开发必要性1之设计考虑

RDMA over RoCE V2设计1:通用,稳定及高性能!

RDMA over RoCE V2设计1:通用,稳定及高性能!

RDMA简介9之AXI 总线协议分析2

RDMA简介8之AXI 总线协议分析1

RDMA简介4之ROcE V2初析

RDMA简介3之四种子协议对比

RDMA简介2之A技术优势分析

RDMA简介1之RDMA开发必要性

NVMe简介之AXI总线

RDMA简介8之AXI分析

RDMA简介8之AXI分析

评论