AXI4-Stream去掉了地址项,允许无限制的数据突发传输规模;

二、握手机制

只有当VALID和READY同时为高时,才能进行传输。

VALID和READY信号的先后顺序有一下三种形式:

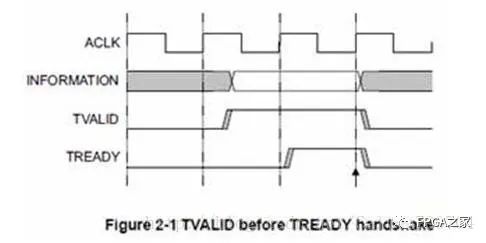

2.1VALID早于READY信号

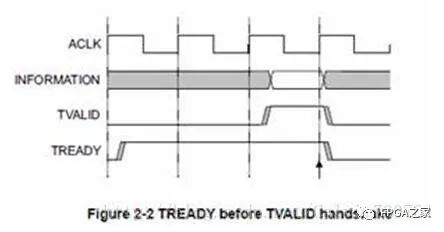

2.2READY信号早于VALID信号

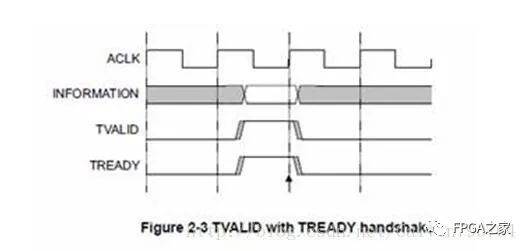

2.3 VALID信号与READY信号同时

三、基本事务

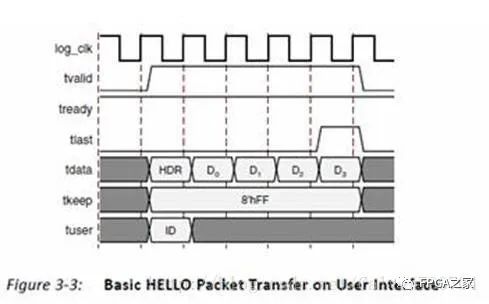

AXI4-Stream跟AXI4的区别就是AXI4-Stream去除了地址线,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时。由于AXI4-Stream协议(amba4_axi4_stream_v1_0_protocol_spec.pdf)没有时序图,因此,我使用XILINX公司的产品指导手册(pg007_srio_gen2_v3_1.pdf)里的一个时序图来演示AXI4-Stream各个信号的关系。如下图所示:

上图中,tready信号一直处于高电平,表示从设备做好了接收数据准备。tvalid变为高电平的同时,tdata、tkeep、tuser也同时进行发送。在tdata最后一个字节数据时,tlast发送一个高电平脉冲。数据发送完成后,tvalid变为低电平。这样一次传输就完成了。

审核编辑 :李倩

-

信号

+关注

关注

11文章

2901浏览量

79652 -

Stream

+关注

关注

0文章

21浏览量

8218

原文标题:AXI4-Stream协议总结

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

利用开源uart2axi4实现串口访问axi总线

使用AXI4接口IP核进行DDR读写测试

RDMA设计4:技术需求分析2

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

关于AXI Lite无法正常握手的问题

RDMA简介9之AXI 总线协议分析2

RDMA简介8之AXI 总线协议分析1

NVMe IP之AXI4总线分析

NVMe简介之AXI总线

NVMe协议简介之AXI总线

一文详解Video In to AXI4-Stream IP核

关于AXI4-Stream协议总结分享

关于AXI4-Stream协议总结分享

评论