本文以Kintex-7系列XC7K410T FPGA芯片和两片MT41J128M16 DDR3 SDRAM芯片为硬件平台,设计并实现了基于FPGA的视频图形显示系统的DDR3多端口存储管理。##每片

2015-04-07 15:52:10 13985

13985

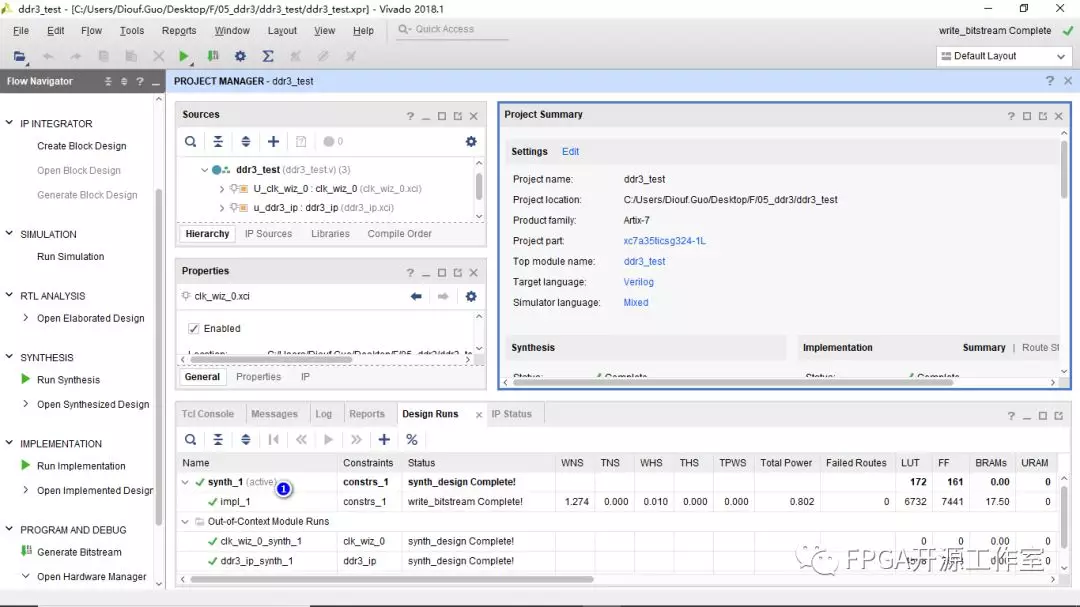

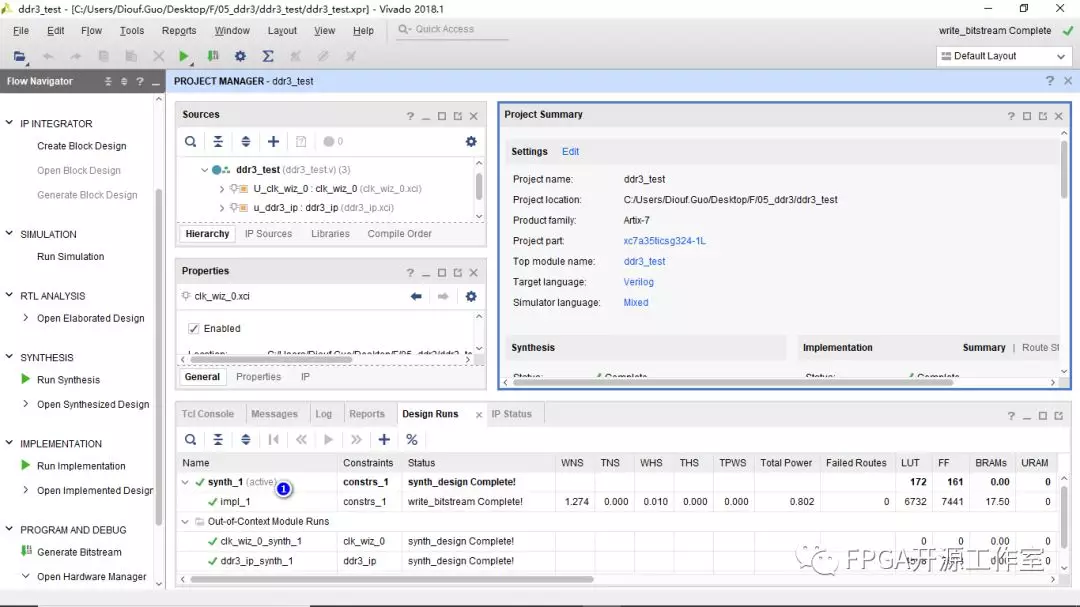

将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA

2020-12-15 16:45:16 3617

3617

讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。 软件

2021-01-01 10:09:00 5266

5266

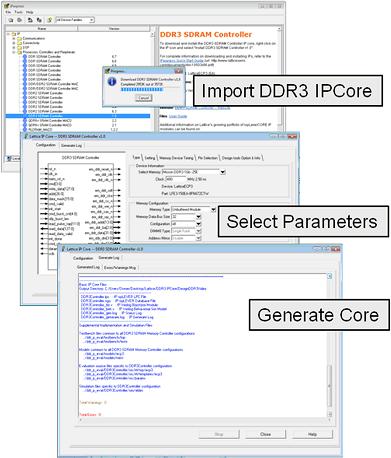

本实验为后续使用DDR3内存的实验做铺垫,通过循环读写DDR3内存,了解其工作原理和DDR3控制器的写法,由于DDR3控制复杂,控制器的编写难度高,这里笔者介绍采用第三方的DDR3 IP控制器情况下的应用,是后续音频、视频等需要用到DDR3实验的基础。

2021-02-05 13:27:00 10988

10988

和 x16 配置中均可提供高达 2133Mbps 的数据传输速率,并可与1.5V DDR3实现100%兼容。目前,华邦的 DRAM 产品布局包括1Gb-4Gb DDR3、128Mb-2Gb DDR

2022-04-20 16:04:03 3594

3594

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代产品,相较于DDR2,DDR3有更高的运行性能与更低的电压。

2025-04-10 09:42:53 3930

3930

请教各位大虾:

怎样实现6678和DDR3间的EDMA操作,哪位高手有相关的代码可以共享哈

还有就是当从DDR3中将数据一维搬至DSP中,处理完后再将DSP中的数据二维放至DDR3中时需要配置哪些寄存器,具体怎样配置 谢谢!!~

2018-06-21 16:49:06

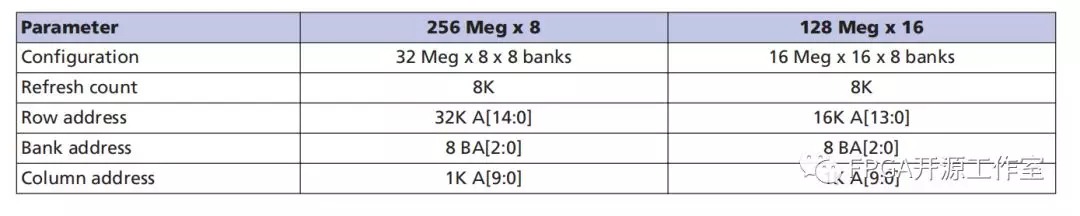

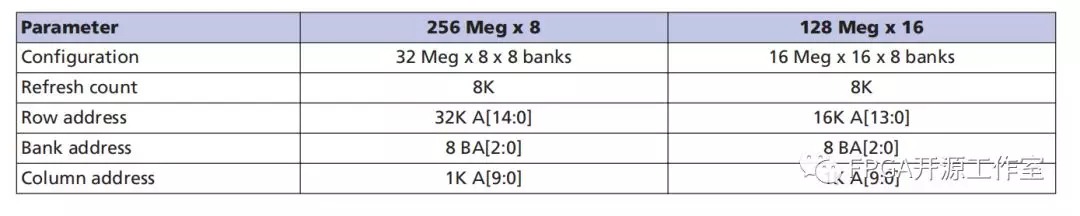

麻烦大家帮我看下,图片里面的DDR3模组(SO-DIMM)支持多大容量的内存条?我记得计算内存容量的话,是要知道行地址、列地址,bank数的,从图片的设计上能看出来行地址和列地址是多少吗?另外,如果进行多通道的设计应该怎么做?是数据线,地址线公用的吗?怎么控制不同的通道呢?

2017-10-25 19:53:33

使用microblaze处理器。我必须通过DDR3内存发送一些固定值,如8位数据(X'FF'),即我将该数据写入Genesys2 DDR3内存并从内存中读出数据。我已经通过Xilinx网络设备视频手册

2019-05-05 15:29:38

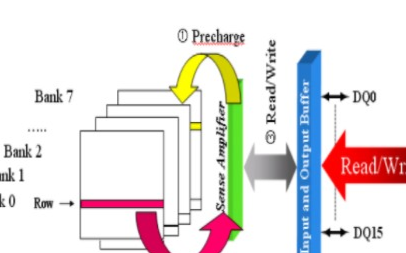

转载DDR3内存详解,存储器结构+时序+初始化过程2017-06-17 16:10:33a_chinese_man阅读数 23423更多分类专栏:硬件开发基础转自:首先,我们先了解一下内存的大体结构工作流程,这样会比较容量理解这些参数在其...

2021-07-27 07:10:34

DDR3基础详解最近在IMX6平台下做DDR3的测试接口开发,以前在学习嵌入式时,用的是官方源码,没有做过多的研究。此时需要仔细研究DDR3的引脚与时序,此篇是我在学习DDR3做的归纳与总结,其中有

2021-07-28 09:02:52

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA进出。DDR3存储器系统在大多数情况下可以为这些基于FPGA的系统

2019-05-24 05:00:34

DDR3芯片读写控制及调试总结,1. 器件选型及原理图设计(1) 由于是直接购买现成的开发板作为项目前期开发调试使用,故DDR3芯片已板载,其型号为MT41J256M16HA-125,美光公司生产的4Gb容量DDR3芯片。采...

2021-07-22 08:33:54

更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM DIMM条的接口设计呢? 关键字:均衡(leveling)如果FPGA I/O结构中没有包含均衡功能,那么它与DDR3

2019-04-22 07:00:08

各位大虾,我想设计一个检测FPGA的外挂DDR3硬件是否有问题的程序。目前先做初级阶段工作,主要实现以下几点:1、检测DDR3数据线DQ是否有错连和漏连(虚焊)的情况,如有找到对应的错误处;2

2013-04-12 13:00:45

DDR3的理论带宽怎么计算?用xilinx的控制器输入时钟200M。fpga与DDR的接口如下:

2016-02-17 18:17:40

FPGA如何对引脚进行分块?是由VCC的电压不同进行自行设计分块?还是每个块的引脚都是固定的?在进行DDR3与FPGA的硬件连接时,由FPGA的芯片手册得采用SSTL_15电压标准,即VDDQ

2021-11-29 16:10:48

各位专家,我使用altera的cyclone5的DDR3硬核控制器,输入时钟是国产的125兆50PPM有源晶振,现在调试时发现对DDR3的读写偶尔出错。我们测试DDR3接口的差分时钟,发现左右抖动

2018-05-11 06:50:41

六通道24bit192kHz芯片WM8746资料下载内容包括:WM8746功能和特点WM8746引脚功能WM8746内部方框图

2021-03-26 07:58:59

我是一名labview FPGA程序员,使用的是NI 7975 fpga模块,它具有kintex 7 fpga。该模块具有外部DDR3 DRAM 0f 2GB以及kintex 7 fpga资源。数据应该从芯片到芯片之间会有多少延迟?这是DDR3 DRAM双端口(同时读写操作可能??)???

2020-05-20 14:42:11

因为工作的需要,最近做了下DDR3 IP核的读写仿真,仿真过程中DDR写数据正常,但在对DDR读取数据时出现以下的情况:1.MEM_DQ、MEM_DQS、MEM_DQSN始终为高阻态

2019-12-26 23:11:56

DM8168,仅使用DDR0通道连接 4片8bit的ddr3,而DDR1通道不接ddr3,请问SD卡启动的时候需要有特殊配置吗?

现在是SD卡启动无打印输出,在无SD卡和NAND FLASH时候,打印有输出,但不是CCCCC,会是什么原因?

2018-06-21 12:33:25

。 HZD-W-B型六通道振动巡检仪功能说明 1、实现智能处理:报警ⅰ值、ⅱ值可通过面板按键任意设置 2、面板按键可调整量程值,无需电位器调整,方便现场调试3、一分钟不按操作键,可自行回到运行状态 4、报警

2017-06-05 11:03:22

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3资料。

2016-05-27 16:39:58

DDR3的IP核配置完毕后,产生了好多文件,请问如何调用这些文件实现DDR3的读写呢?看了一些文章,说是要等到local_init_done为高电平后,才能进行读写操作。请问DDR3的控制命令如

2016-01-14 18:15:19

labview被动接收arduino发送的六通道采集数据,有同步头判断,很少丢数据。没有全面显示,没有保存功能,只是简单的演示可以成功实现功能。

2013-05-31 12:00:06

稳定的工作。项目名称:DDR3。 具体要求:实现DDR3数据的读写。 系统设计:实现过程:1.新建工程之后打开Create BlockDesign,并修改Design name。2.按照系统设计依次添加

2021-07-30 11:23:45

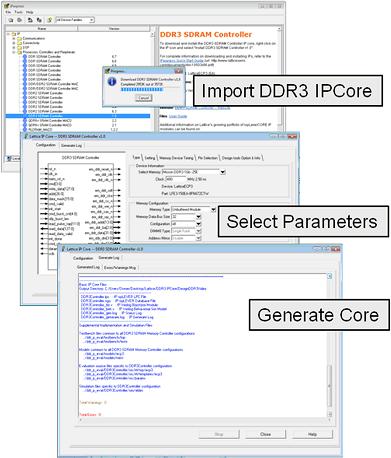

本视频是Combat FPGA开发板的配套视频课程,本章节课程主要介绍Gowin中DDR3 的基础知识、DDR3的IP core的特性和使用以及DDR3的IPcore例程的仿真。课程资料包含DDR3

2021-05-06 15:34:33

MT41J25616XX用于DDR3芯片。当我们使用MIG工具配置DDR3时,对于我们的FPGA,此DDR3组件未显示在支持的DDR3组件列表中。如果我们使用“创建自定义部件”添加我们的芯片,那么

2019-02-18 09:01:37

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA进出。DDR3存储器系统在大多数情况下可以为这些基于FPGA的系统

2019-05-27 05:00:02

了保证带宽率的相应措施。在此基础上,将FPGA的DDR3的读写控制模块封装成简单的类FIFO接口。并将其在Xilinx公司的Kintex-7 系列FPGA芯片上实现,工作稳定可靠、有较高的工作效率、接口简单、可移植性高,为DDR3在高速数据流缓存中的应用提供了便利。

2018-08-02 09:34:58

作者:张凤麒,张延彬,王忠勇;2018年电子技术应用第7期摘要: 为了解决期货行情数据加速处理中多个通道同时访问DDR3时出现的数据读写冲突问题,实现了一种基于FPGA的DDR3六通道读写防冲突

2018-08-02 09:32:45

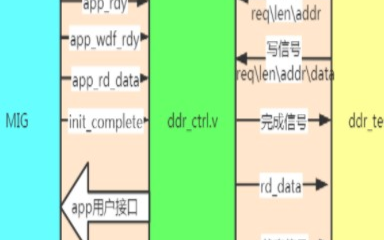

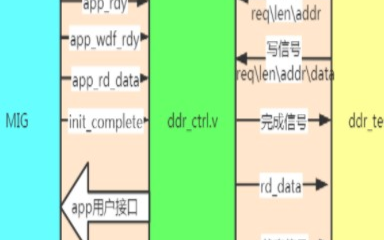

的冲突。帧地址控制模块控制帧地址的切换。为了提高并行处理的速度,简化数据读写冲突,将图形数据和视频数据分别存储在不同的DDR3中。2DDR3存储器控制模块设计MIG生成的DDR3控制器的逻辑框图[5

2018-08-02 11:23:24

今天给大侠带来《基于FPGA的DDR3多端口读写存储管理设计》,话不多说,上货。

摘要

为了解决视频图形显示系统中多个端口访问DDR3时出现的数据存储冲突问题,设计了一种基于FPGA

2024-06-26 18:13:42

Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,设计和实现了

2018-08-30 09:59:01

选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足

2019-06-24 06:07:53

基于Xilinx MIS IP的DDR3读写User Interface解析特权同学,版权所有,转载请注明出处参考文档:ug586_7Series_MIS.pdf1. Command时序首先,关于

2016-10-13 15:18:27

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

怎样对DDR3芯片进行读写控制呢?如何对DDR3芯片进行调试?

2021-08-12 06:26:33

包含代码、详细说明、物料表Diy arduino rc接收器和发射器,六通道强大功能!

2023-09-26 08:08:35

数据速率 800Mbps

一、实验要求

生成 DDR3 IP 官方例程,实现 DDR3 的读写控制,了解其工作原理和用户接口。

二、DDR3 控制器简介

GL50H 为用户提供一套完整的 DDR

2023-05-19 14:28:45

我输入125兆时钟给FPGA,经过FPGA内部的PLL产生300兆的时钟给FPGA内部的DDR3控制硬核,但是现在发现对外部ddr3的读写数据不稳定。请问各位专家,ddr3的时钟频率稳定度需要多少PPM以内?对输入时钟的jitter有要求吗?

2018-05-10 15:42:23

输入电压达到正负5v、精度比较高最好是12bit以上的,六通道的ADC芯片一般选哪几种,因为ADC之后是直接接FPGA处理的、最好是那种ADC芯片好呢、性能越好越好、

2025-01-22 06:47:30

SM9858 是一款六通道电子音量控制IC,采用CMOS 工艺制造。SM9858通过I2C 通信协议对六个通道的音频信号进行独立调节控制。每个通道的音量调节范围为0——79dB,步长为 1 dB/step。

2009-07-21 10:42:12 90

90 单片计算机应用系统在生物医学信号的采集及处理方面具有广阔的应用前景。作者根据实际需要研制了一款六通道数据采集及处理单片计算机应用系统,该系统在医学生生

2009-08-11 09:48:06 8

8 DDR3存储器系统可以大大提升各种数据处理应用的性能。然而,和过去几代(DDR和DDR2)器件相比,DDR3存储器器件有了一些新的要求。为了充分利用和发挥DDR3存储器的优点,使用一

2010-07-16 10:46:05 2064

2064

摘要:介绍了高精度六通道同步采样A/D芯片ADS8364的主要功能与特点,并结合高速浮点数字信号处理器(DSP)TMS320C6713与ALTERA公司的CPLDEPM7128在系统中的使用方法,介绍ADS8364在微惯性航姿系统中完成数据采集功能的具体应用。微惯性航姿系统通过ADS8364能够

2011-02-28 16:44:10 141

141 Microchip 美国微芯科技公司宣布,推出旗下首款独立的适用于三相电能计量的高精度六通道模拟前端(AFE) MCP3903

2011-07-28 09:43:22 5977

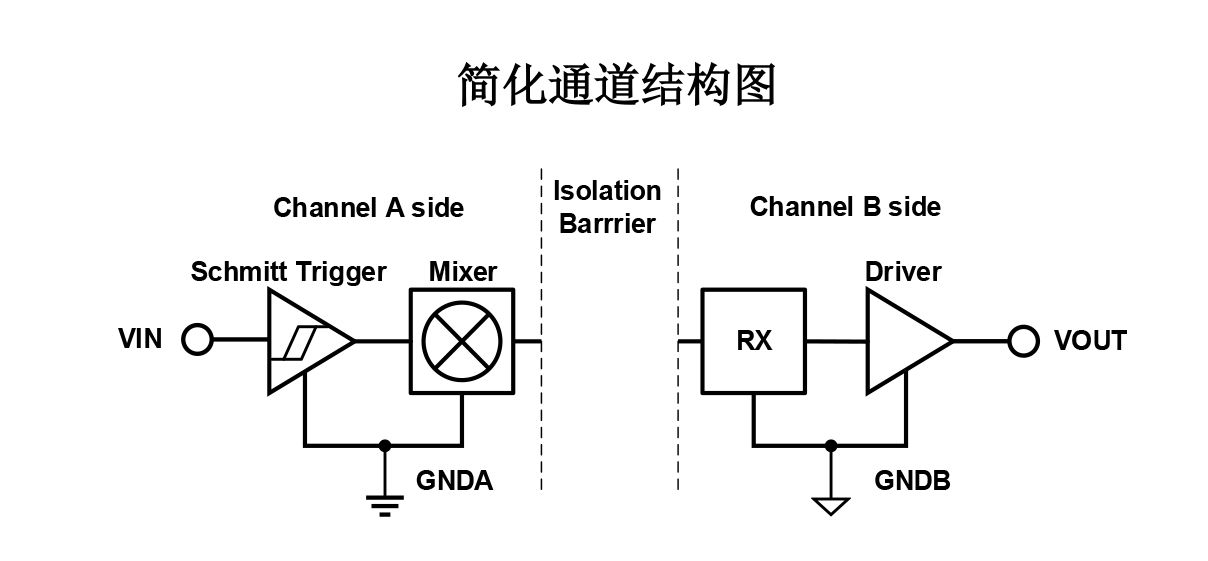

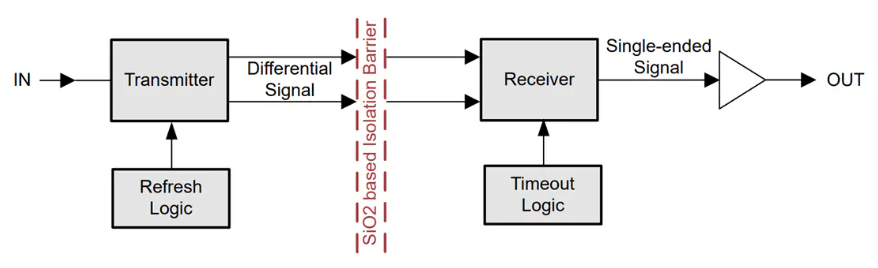

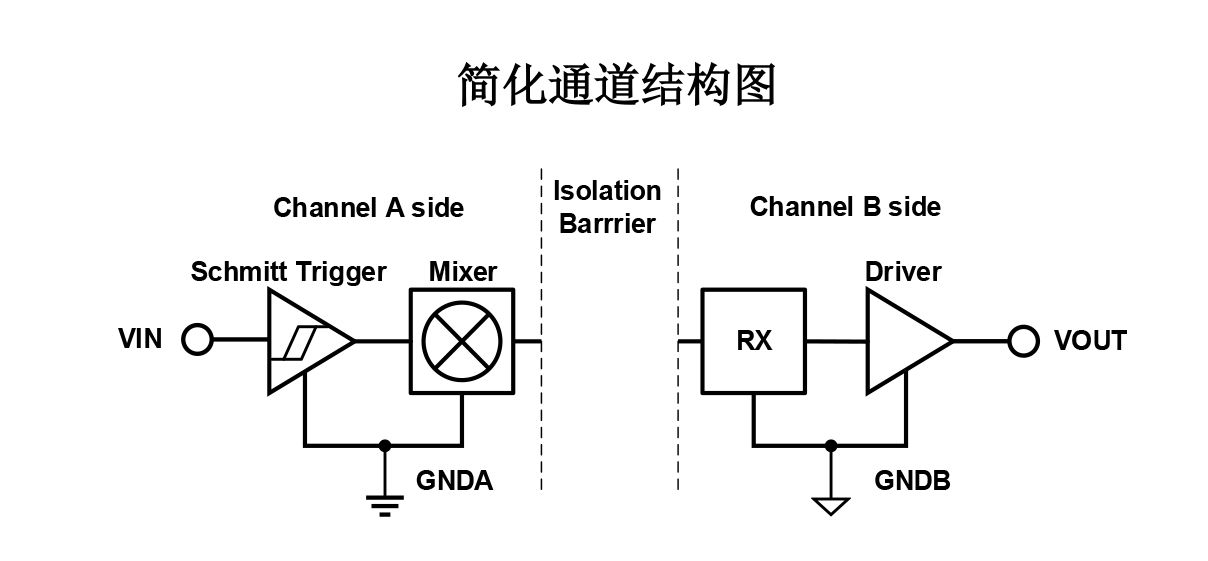

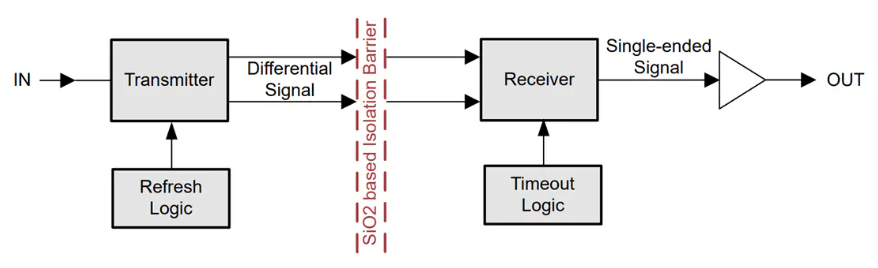

5977 MAX14850是一个六通道数字隔离器采用Maxim专有的工艺技术,其整体设计提供了一个紧凑和低成本的传输数字信号的电路不同的电源域之间。

2012-03-28 15:58:58 4286

4286

Xilinx FPGA工程例子源码:Xilinx DDR3最新VHDL代码(通过调试)

2016-06-07 14:54:57 77

77 六通道高速数据采集系统的设计

2017-01-17 19:54:24 11

11 。例如,下面的插图是取自指导手册关于DDR3地址总线和时钟总线设计的说明。 与上面的插图相比,下面的是指导手册中关于DDR4的地址总线,指

2017-02-08 10:04:09 2134

2134

和PL端的Master IP核,共同访问操作一个Slave端即DDR3 Controllor。 本次实验就是构建一个这样的验证系统。当然了在真正的工程系统中,还需要设计良好的读写同步,防止竞争冲突,这就属于系统设计层面的了,本实验依靠按钮触发有用户来进行读写同步。

2017-09-15 16:35:01 25

25 构建SoC系统,毕竟是需要实现PS和PL间的数据交互,如果PS与PL端进行数据交互,可以直接设计PL端为从机,PS端向PL端的reg写入数据即可,本节研究如何再实现PL端对DDR3的读写操作。

2017-09-18 11:08:55 23

23 DDR3是目前DDR的主流产品,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。最开始的DDR, 芯片采用的是TSOP封装,管脚露在芯片两侧的,测试起来相当方便;但是,DDRII和III就不一样了,

2017-11-06 13:44:10 9412

9412

Group具备独立启动操作读、写等动作特性,Bank Group 数据组可套用多任务的观念来想象,亦可解释为DDR4 在同一频率工作周期内,至多可以处理4 笔数据,效率明显好过于DDR3。

2017-11-07 10:48:51 55965

55965

虽然新一代电脑/智能手机用上了DDR4内存,但以往的产品大多还是用的DDR3内存,因此DDR3依旧是主流,DDR4今后将逐渐取代DDR3,成为新的主流,下面我们再来看看DDR4和DDR3内存都有哪些区别。相比上一代DDR3,新一代DDR4内存主要有以下几项核心改变:

2017-11-08 15:42:23 32469

32469 为解决超高速采集系统中的数据缓存问题,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行

2017-11-16 14:36:41 25160

25160

为了满足高速图像数据采集系统中对高带宽和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的设计方法,提出了一种基于Verilog-HDL 语言的DDR3 SDRAM

2017-11-17 14:14:02 4071

4071

本文详细介绍了在Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取

2017-11-17 14:26:43 26092

26092

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR3

2017-11-18 18:51:25 7989

7989

针对采用DDR3接口来设计的新一代闪存固态盘(SSD)需要完成与内存控制器进行通信与交互的特点,提出了基于现场可编程门阵列( FPGA)的DDR3协议解析逻辑方案。首先,介绍了DDR3内存工作原理

2017-12-05 09:34:44 10

10 DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走线的建议,这些建议同样也适用于高密度、紧凑型的电路板设计。

2018-06-16 07:17:00 10446

10446

该讲座主要讲述:MCP3903 六通道模拟前端采样芯片

2018-06-06 13:46:00 4637

4637

说明:

MCP3913 是 3V 六通道模拟前端(Analog Front End,

AFE),包括六个同步采样的 Δ−Σ 模数转换器(Analogto-Digital

Converter

2018-06-30 11:23:00 21

21 DR3 在高频时数据出现了交错,因此,高速DDR3存储器设计有一定的难度。如果FPGA I/O 结构中没有直接内置调平功能,那么连接DDR3 SDRAM DIMM的成本会非常高,而且耗时,并且需要

2018-06-22 02:04:00 4421

4421 、QDR,当然,还有DDR3 UDIMM插槽。因此,我们所要做的就是通过Quartus软件来下载一个简单设计,FPGA进行简单的数据写入并读回。

我们还采用了一些测试设备来帮助进行演示,Nexus

2018-06-22 05:00:00 9486

9486 使用中速Kintex-7 325T FPGA演示DDR3控制器和接口,运行速度高于1866 Mbps数据速率。

2018-11-30 06:21:00 6366

6366

这展示了DDR3内存的Kintex-7 FPGA接口功能。

2018-11-30 06:23:00 7144

7144 我们通过Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封装,速度等级等信息。

2019-03-03 11:04:15 2626

2626

本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 通过之前的学习,CPU可以读写DDR3了,PL端的Master IP也可以读写DDR3了,那二者就可以以DDR3为纽带,实现大批量数据交互传输。

2020-07-27 08:00:00 16

16 用于 DDR 电源及终端的高效率、双通道、±3A同步降压型稳压器符合 DDR / DDR2 / DDR3 标准

2021-03-19 08:44:50 13

13 这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

2021-05-02 09:05:00 4228

4228

LTC2937:带EEPROM数据表的可编程六通道序列器和电压监控器

2021-05-19 16:02:05 2

2 POD模式; 增加ACT_n控制指令为增强数据读写可靠性增加的变更点主要有: DBI; Error Detection;1 电源变化DDR3与DDR4的96 Ball封装pin定义...

2021-11-06 20:36:00 30

30 CA-IS376x 高速六通道数字隔离器

2021-11-26 15:25:46 1463

1463

为了更方便的对DDR读写,我们对DDR再次封装成可复用的读写模块。

2022-02-26 17:34:37 2634

2634

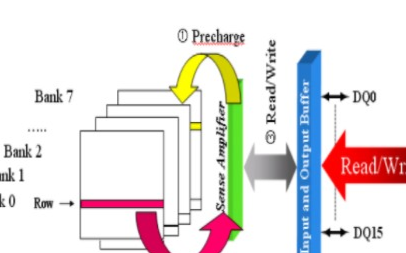

,是指DDR3中的数据掉电无法保存,且需要周期性的刷新,才能保持数据;所谓随机存取,即可以随机操作任一地址的数据;所谓double-data-rate,即时钟的上升沿和下降沿都发生数据传输。

2022-02-21 17:51:45 5363

5363

DP4361 是一款立体声六通道线性输出的数模转 换 器,内含插值滤波器、Multi-Bit 数模转换 器、模 拟输出滤波器,支持主流的音频数据格式。

2022-08-01 16:39:03 0

0 的读取写入是按时钟同步的;所谓动态,是指DDR3中的数据掉电无法保存,且需要周期性的刷新,才能保持数据;所谓随机存取,即可以随机操作任一地址的数据;所谓double-data-rate,即时钟的上升沿

2022-12-21 18:30:05 5149

5149 视频图形显示系统理想的架构选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。 与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足吞吐量大、功耗低的需求,因此

2023-06-08 03:35:01 2788

2788 DDR3的速度较高,如果控制芯片封装较大,则不同pin脚对应的时延差异较大,必须进行pin delay时序补偿。

2023-07-04 09:25:38 936

936

电子发烧友网站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中应用.pdf》资料免费下载

2023-07-24 09:50:47 3

3 本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

2023-09-01 16:20:37 7275

7275

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 3353

3353

DDR3是2007年推出的,预计2022年DDR3的市场份额将降至8%或以下。但原理都是一样的,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。

2023-10-18 16:03:56 1889

1889

电子发烧友网站提供《通用六通道增强型数字隔离器 ISO676x数据表.pdf》资料免费下载

2024-02-28 11:08:07 0

0 电子发烧友网站提供《DS92LV1260六通道10位BLVDS解串器数据表.pdf》资料免费下载

2024-07-01 09:41:54 0

0 六通道CAN集线器 --SG-CanHub-600 功能概述 SG_CanHub_600是一款具有六路通道的工业级智能 CAN数字隔离中继集线器。 SG_CanHub_600能够实现信号再生、延长

2024-11-13 09:42:44 1338

1338

Texas Instruments ISO6163六通道3/3数字隔离器是高性能数字隔离器,设计用于需要高达~5000VRMS~ 隔离等级(符合UL 1577标准)的高能效成本敏感型应用。这些器件

2025-07-04 15:30:27 722

722

的讲解数据线等长设计。 在另一个文件《AD设计DDR3时等长设计技巧-地址线T型等长》中着重讲解使用AD设计DDR地址线走线T型走线等长处理的方法和技巧。

2025-07-28 16:33:12 4

4

电子发烧友App

电子发烧友App

评论