本章的实验任务是在 PL 端自定义一个 AXI4 接口的 IP 核,通过 AXI_HP 接口对 PS 端 DDR3 进行读写测试,读写的内存大小是 4K 字节。

2025-11-24 09:19:42 3467

3467

microblaze和jtag-to-axi(jtag2axi)虽然也提供了访问axi总线的能力,但是依赖于xilinx平台。而uart-to-axi(uart2axi4)桥接器并不依赖任何平台

2025-12-02 10:05:43 1842

1842

)是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。 AXI4-Stream:(For high-speed streaming data.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。 AXI4总线和AXI4-Lite总线具有相同的

2018-01-09 14:10:42 9365

9365

Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,专用于和元器件内的控制寄存器进行通信。AXI-Lite允许构建简单的元件接口。这个接口规模较小,对设计和验证方面的要求更少

2020-09-27 11:33:02 9821

9821

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI4

2020-12-04 12:22:44 9054

9054

构成的传输数据的通道, 一般由数据线、地址线、 控制线构成。 Xilinx从6系列的 FPGA 开始对 AXI 总线提供支持, 此时 AXI 已经发展到

2020-12-25 14:07:02 6724

6724

赛灵思 AXI Verification IP (AXI VIP) 是支持用户对 AXI4 和 AXI4-Lite 进行仿真的 IP。它还可作为 AXI Protocol Checker 来使用。

2022-07-08 09:24:17 2976

2976 在这篇新博文中,我们来聊一聊如何将 AXI VIP 添加到 Vivado 工程中,并对 AXI4-Lite 接口进行仿真。随后,我们将在仿真波形窗口中讲解用于AXI4-Lite 传输事务的信号。

2022-07-08 09:27:14 2741

2741 在 AXI 基础第 2 讲 一文中,曾提到赛灵思 Verification IP (AXI VIP) 可用作为 AXI 协议检查工具。在本次第4讲中,我们将来了解下如何使用它在 AXI4 (Full) 主接口中执行验证(和查找错误)。

2022-07-08 09:31:38 4371

4371 AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互连以及其他AXI4系统外设上生成特定序列(流量)。它根据IP的编程和选择的操作模式生成各种类型的AXI事务。是一个比较好用的AXI4协议测试源或者AXI外设的初始化配置接口。

2023-11-23 16:03:45 5162

5162

AXI接口FIFO是从Native接口FIFO派生而来的。AXI内存映射接口提供了三种样式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的应用外,AXI FIFO还可以用于AXI系统总线和点对点高速应用。

2025-03-17 10:31:11 1914

1914

Video In to AXI4-Stream IP核用于将视频源(带有同步信号的时钟并行视频数据,即同步sync或消隐blank信号或者而后者皆有)转换成AXI4-Stream接口形式,实现了接口转换。该IP还可使用VTC核,VTC在视频输入和视频处理之间起桥梁作用。

2025-04-03 09:28:14 2418

2418

,SG)功能还可以将数据移动任务从位于于处理器系统中的中央处理器(CPU)中卸载出来。可以通过一个AXI4-Lite从接口访问初始化、状态和管理寄存器。如图4. 8展现了DMA IP的功能构成核心。

2025-04-03 09:32:24 2246

2246

此信号。 从机(slave)控制的信号 11.TREADY 握手信号 一个AXI-stream传输的时序图: 图4‑59 AXI-stream example AXI4-stream主从

2021-01-08 16:52:32

我必须通过AXI4-lite接口配置Jesd204b核心,或者我可以简单地将AXI4-lite端口保持未连接状态(强制接地)?Jesd204核心示例top没有提供有关AXI4-Lite端口配置的指导。

2020-05-15 09:30:54

最近在搞AXI4总线协议,有一个问题困扰了两天,真的,最后知道真相的我,差点吐血。 问题是这样的,我设置了突发长度为8,结果,读了两个轮回不到,断了,没有AWREDATY信号了,各种找,最后发现设置

2016-06-23 16:36:27

如果在仿真的时候出现可以写,可以读,但是读出来的数据一直是那么几个的问题,很有可能,你和我一样,是个马大哈了,去看DQ,是不是地址也来来去去就那么几个?是的话,可以考虑考虑你的地址的问题,AXI4

2016-06-24 16:25:38

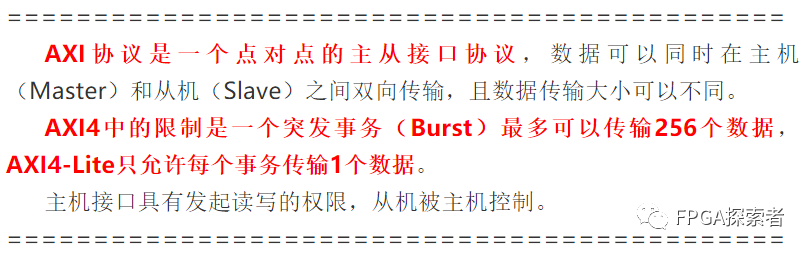

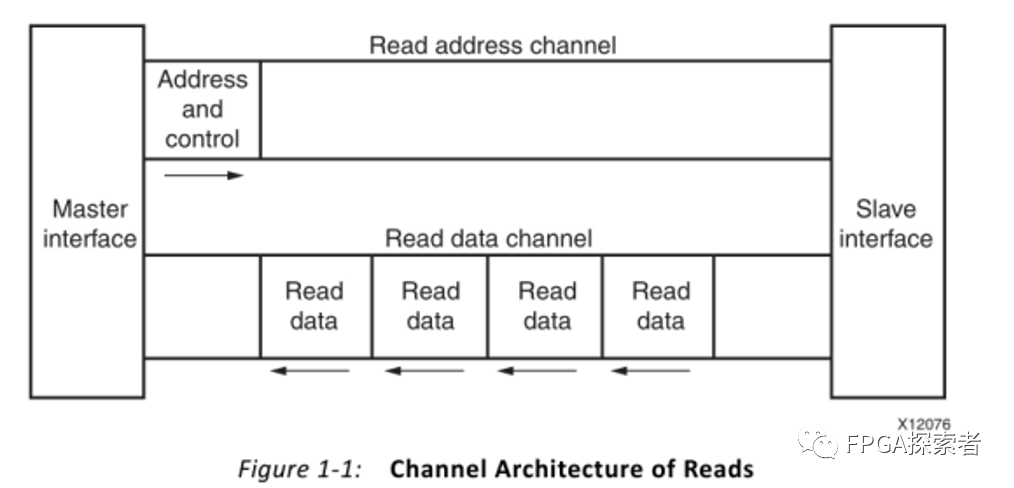

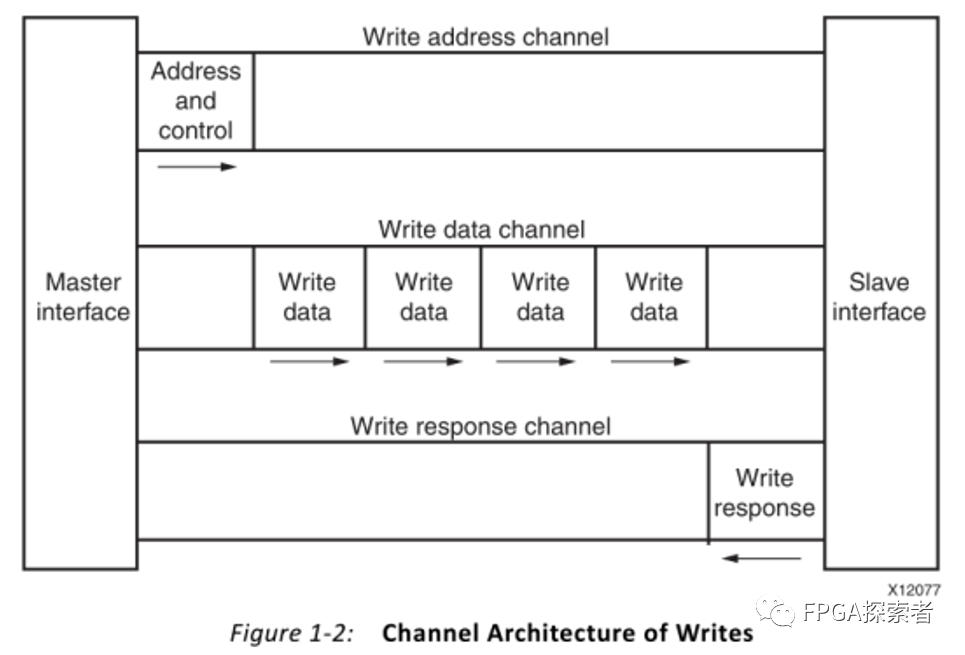

AXI4协议基于猝发式传输机制。在地址通道上,每个交易有地址和控制信息,这些信息描述了需要传输的数据性质。主从设备间的数据传输有两种情况,一种是主设备经过写通道向从设备写数据(简称写交易

2021-01-08 16:58:24

AXI有哪些性能?AXI的特点是什么?AXI4有哪些工作模式?

2021-06-23 08:13:52

是主机,而第一个字母 “S” 表示 PS 是从机。在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现

2022-04-08 10:45:31

突发传输; AXI4-Lite:(For simple, low-throughput memory-mapped communication)是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元

2022-10-14 15:31:40

到新的通道。错误的处理例化了一个Axi4ReadOnlySlaveError:可以看到,只有所有slave端口的地址段大小总和小于Axi4总线能覆盖的地址范围时方例化

2022-08-04 14:28:56

NVMe AXI4 Host Controller IP1介绍NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令

2025-11-14 22:40:50

您可以将协议断言与任何旨在实现AMBA®4 AXI4的接口一起使用™, AXI4 Lite™, 或AXI4流™ 协议通过一系列断言根据协议检查测试接口的行为。

本指南介绍SystemVerilog

2023-08-10 06:39:57

XHB将AXI4协议转换为AHB-Lite协议,并具有AXI4从接口和AHB-Lite主接口。有关AXI4事务如何通过XHB桥接到AHB-Lite的信息,请参阅第2-2页的表2-1

2023-08-02 06:51:45

in the reference design consist of AXI4, AXI4-Lite, andAXI4-Stream interfaces as described in the AMBA AXI4

2012-01-26 18:57:03

针对不同的应用场景,制定了三个不同类型的接口,其中包括AXI4-Full、AXI4-Lite以及AXI4-Stream。表1为三种AXI4总线的对比。

表1三种AXI4总线对比

总线名称

2025-06-02 23:05:19

高性能、高带宽、低延时的片内互连需求。AXI4总线则是AXI总线的第四代版本,主要包含三种类型的接口,分别是面向高性能地址映射通信的AXI4接口、面向轻量级单次地址映射通信的AXI4-Lite接口和面

2025-05-17 10:27:56

的fifo接口),用户只要操作fifo接口,无需关心PCIE的内部驱动。为了便于读者更加明白,可以深入了解PCIE,我们将会制作一个PCIE的连载系列。今天,首先说一下自定义AXI4的IP核,至于AXI4

2019-12-13 17:10:42

,分别为:AXI4、AXI4-Lite 和 AXI4-Stream接口。其中 AXI4 也称为 AXI4-Full 是一种基于地址的高性能传输接口,其支持乱序传输、突发传输等传输方式,同时通过独立

2025-06-24 18:00:11

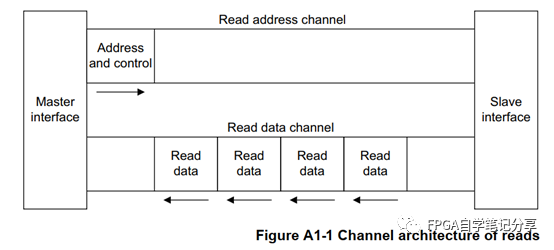

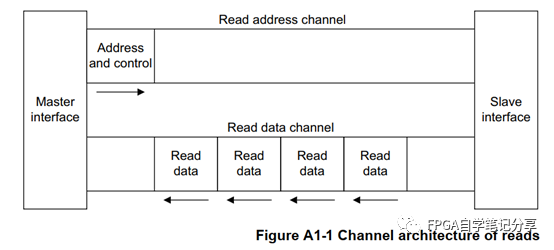

一同反馈给主机。AXI4 总线的通道结构如图 1所示。

图1 AXI4 总线的通道结构图

相关视频感兴趣者,请搜B站用户名: 专注与守望

或链接:

https://space.bilibili.com/585132944/upload/video

2025-06-24 18:02:23

这是SoC Designer AXI4协议包的用户指南。该协议包包含SoC Designer组件、探针和ARM AXI4协议的事务端口接口(包括对AMBA4 AXI的支持)。

2023-08-10 06:30:18

你好,我有一个关于XADC及其AXI4Lite接口输入的问题。我想在Microzed 7020主板上测试XADC,在通过AXI4Lite接口将Zynq PL连接到XADC向导(参见第一个附件)之后

2018-11-01 16:07:36

data.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。AXI4总线和AXI4-Lite总线具有相同的组成部分:(1)读地址通道,包含ARVALID, ARADDR, ARREADY

2018-01-08 15:44:39

AXI4总线协议,接下来我们将对该协议作一个更具体的介绍。AXI的英文全称是Advanced eXtensible Interface,即高级可扩展接口,它是ARM公司所提出的AMBA(Advanced

2020-10-22 15:16:34

按键控制LED实验》中的AXI4-Lite接口等。其中AXI4-Lite接口属于AXI4总线协议,接下来我们将对该协议作一个更具体的介绍。AXI的英文全称是Advanced eXtensible

2020-09-04 11:10:32

[]合成了内存),输出端口合成为ap_fifo,这意味着,由于AXi4Lite不支持fifo结构,因此只能使用AXI4Stream接口/总线从输出端口result []读取数据。我也是这个嵌入式总线和接口

2019-02-28 13:47:30

接口进行仿真验证),提前规避和发现一些不满足AXI总线规范的设计问题。本文就跟大家分享如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法。本文参考的Xilinx官方文档为

2022-10-09 16:08:45

多选一的抉择相较于Axi4写通路,多通路的多选一就容易多了。对于Axi4ReadOnlyArbiter,其仅需处理两个问题:Ar通路多端口仲裁,其处理和写通路aw通路基本相同,采用多端口RR调度即可

2022-08-08 14:32:20

大家好,我正在两个时钟域之间穿过AXI4-Stream,并尝试使用AXI4-Stream时钟转换器核心,使用tkeep端口但是在合成时它被Vivado 2015.2在实例化时删除了!这是综合警告

2020-05-08 08:56:14

元素(如混合端序结构)的支持。

本文档重点介绍AXI4中定义的AXI的关键概念,并强调了差异

适用时,适用于AXI3。AXI5扩展了AXI4,并引入了一些性能和Arm

架构特征。此处描述的关键概念仍然适用,但

AXI5在此未涵盖

2023-08-09 07:37:45

使用AXI4流快速读取?如果这不是一个不错的方法,还有其他方法可以使用Virtex-7来解决这个问题吗?以上来自于谷歌翻译以下为原文Hey all. I'm currently working

2019-05-05 13:14:10

你好是否可以使用带有AXI4接口的逻辑核心ip reed solomon编码器版本9。问候Rose Varghese

2020-05-20 15:44:58

的FPGA开始引入的一个接口协议(AXI3)。在ZYNQ中继续使用,版本是AXI4,ZYNQ内部设备都有AXI接口。AXI4-Lite则是AXI4的一个简化版本,实现AXI4运行起来的最少接口

2019-05-06 16:55:32

读写分离的设计在Axi4总线中,读和写通道是完全相互独立,互不干扰。故而无论是在设计Decoder还是Arbiter时,均可以采用读写分离的方式。如前文所述,SpinalHDL在基于Axi4总线

2022-08-03 14:27:09

,ar)共用一组信号的接口(arw,w,b,r)。关于总线互联的设计凡是设计中用到Axi4总线的设计总离不开总线互联。在Xilinx FPGA使用中,VIvado针对Axi4总线提供了丰富的IP,对于

2022-08-02 14:28:46

microblaze通过串口读写FPGA内部axi4总线上的寄存器

2020-12-23 06:16:11

我们可以使用AXI-Stream Broadcaster作为AXI开关吗?如果可能,我们需要控制切换哪个信号?我想开发小型应用程序,它涉及广播AXI流数据并将AXI流数据切换到特定的从站。在这个应用程序中,我们只有一个主站和8个从站。我们想在从站之间切换流数据。提前致谢。

2020-05-07 09:42:16

: AXI4-Stream—使用DMA时,从Zynq SoC的XDAC流式接口到内存映射,提供高性能输出 AXI4-Lite —配置和控制XADC以及DMA控制器 AXI4 —配置

2017-02-08 08:10:39 527

527 Xilinx的视频的IP CORE 一般都是 以 AXI4-Stream 接口。 先介绍一下, 这个IP的作用。 下面看一下这个IP 的接口: 所以要把标准的VESA信号 转为

2017-02-08 08:36:19 886

886

基于AXI4Stream总线协议,在Xilinx公司提供的FPGA上实现了一个具有缺陷像素校正、色彩滤波阵列插值、图像降噪实时图像采集与显示功能的视频系统。AXI4Stream总线协议由ARM公司

2017-11-17 08:58:01 5344

5344 1、AXI 总线通道,总线和引脚的介绍 AXI接口具有五个独立的通道: (1)写地址通道(AW):write address channel (2)写数据通道( W): write data

2018-01-05 08:13:47 11271

11271

了解System Generator如何提供AXI4-Lite抽象,从而可以将DSP设计融入嵌入式系统。

完全支持包括集成到IP目录,接口连接自动化和软件API。

2018-11-27 07:24:00 3713

3713 这将创建一个附带 BD 的 Vivado 工程,此 BD 包含 AXI VIP (设置为 AXI4-Lite 主接口) 和 AXI GPIO IP。这与我们在 AXI 基础第 3 讲一文 中完成的最终设计十分相似。

2020-04-30 16:24:50 3097

3097

在本教程中,我们将来聊一聊有关如何在 Vitis HLS 中使用 AXI4-Lite 接口创建定制 IP 的基础知识。

2020-09-13 10:04:19 7395

7395

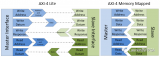

AXI-4 Lite可以看作是AXI-4 Memory Mapped的子集,从下面的示例图中就可见一斑。最直接的体现是AXI-4 Lite的突发长度是固定值1。

2020-09-23 11:18:06 4268

4268

AXI-4 Memory Mapped也被称之为AXI-4 Full,它是AXI4接口协议的基础,其他AXI4接口是该接口的变形。总体而言,AXI-4 Memory Mapped由五个通道构成,如下图所示:写地址通道、写数据通道、写响应通道、读地址通道和读数据通道。

2020-09-23 11:20:23 6924

6924

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite或

2020-09-24 09:50:30 7201

7201

在FPGA程序设计的很多情形都会使用到AXI接口总线,以PCIe的XDMA应用为例,XDMA有两个AXI接口,分别是AXI4 Master类型接口和AXI-Lite Master类型接口,可通过

2020-10-30 12:32:37 5116

5116

新的赛灵思器件设计中不可或缺的一部分。充分了解其基础知识对于赛灵思器件的设计和调试都很有帮助。 本篇博文将介绍赛灵思器件上的 AXI3/AXI4 的相关基础知识。首先,我们将从一些通俗易懂的知识、理论

2020-09-27 11:06:45 7722

7722

DMA的总结 ZYNQ中不同应用的DMA 几个常用的 AXI 接口 IP 的功能(上面已经提到): AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP----AXI-Stream

2020-10-09 18:05:57 8938

8938

在《AXI-Lite 自定义IP》章节基础上,添加ilavio等调试ip,完成后的BD如下图: 图4‑53 添加测试信号 加载到SDK,并且在Vivado中连接到开发板。 Trigger Setup

2020-10-30 17:10:22 2960

2960

和接口的构架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过

2020-11-02 11:27:51 5032

5032

AXI-Stream代码详解 AXI4-Stream跟AXI4的区别在于AXI4-Stream没有ADDR接口,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时,允许无限制的数据

2020-11-05 17:40:36 4705

4705

本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

2021-03-17 21:40:29 25

25 学习内容 近期设计需要用到AXI总线的IP,所以就对应常用的IP进行简要的说明,本文主要对AXI互联IP进行介绍。 基础架构IP 基础的IP是用于帮助组装系统的构建块。基础架构IP往往是一个通用IP

2021-05-11 14:52:55 7870

7870

本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文...

2022-02-07 11:36:33 4

4 XI4-Stream跟AXI4的区别就是AXI4-Stream去除了地址线,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时。由于AXI4-Stream协议(amba4_axi4_stream_v1_0_protocol_spec.pdf)没有时序图,

2022-06-23 10:08:47 3052

3052 本文主要介绍关于AXI4-Stream Video 协议和AXI_VDMA的IP核相关内容。为后文完成使用带有HDMI接口的显示器构建图像视频显示的测试工程做准备。

2022-07-03 16:11:05 10565

10565 AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解

2022-07-04 09:40:14 10523

10523 您是否想创建自己带有 AXI4-Lite 接口的 IP 却感觉无从着手?本文将为您讲解有关如何在 Vitis HLS 中使用 C 语言代码创建 AXI4-Lite 接口的基础知识。

2022-07-08 09:40:43 2808

2808 前面简单学习了关于GPIO的操作,本次将使用PL 端调用 AXI GPIO IP 核, 并通过 AXI4-Lite 接口实现 PS 与 PL 中 AXI GPIO 模块的通信。

2022-07-19 17:36:52 6442

6442 在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP

2022-08-02 09:43:05 1247

1247

本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

2022-08-29 14:58:44 2981

2981 Xilinx vivado下通常的视频流设计,都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read -->

2022-10-11 14:26:03 7574

7574 上面两图的区别是相比AXI3,AXI4协议需要确认AWVALID、AWREADY握手完成才能回复BVALID。为什么呢?

2023-03-30 09:59:49 1851

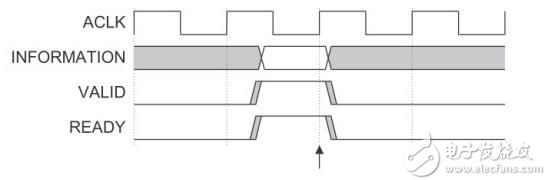

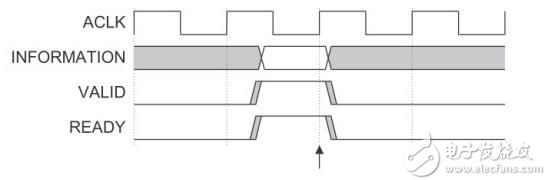

1851 AXI4 协议定义了五个不同的通道,如 AXI 通道中所述。所有这些通道共享基于 VALID 和 READY 信号的相同握手机制

2023-05-08 11:37:50 2039

2039

AMBA AXI协议支持高性能、高频系统设计。

2023-05-24 15:05:12 1916

1916

上文FPGA IP之AXI4协议1_协议构架对协议框架进行了说明,本文对AXI4接口的信号进行说明。

2023-05-24 15:05:46 2767

2767

上文FPGA IP之AXI4协议1_信号说明把AXI协议5个通道的接口信息做了说明,本文对上文说的信号进行详细说明。

2023-05-24 15:06:41 2083

2083

ACLK,ARESETn,AXI所有信号都在时钟的上升沿采样.

2023-06-07 15:24:12 4012

4012

AXI4协议是ARM的AMBA总线协议重要部分,ARM介绍AXI4总线协议是一种性能高,带宽高,延迟低的总线协议。

2023-06-19 11:17:42 5676

5676

AXI4协议是一个点对点的主从接口协议,数据可以同时在主机(Master)和从机(Slave)之间**双向** **传输** ,且数据传输大小可以不同。

2023-06-21 15:26:43 4254

4254

AXI4:高性能内存映射需求(如读写DDR、使用BRAM控制器读写BRAM等),为了区别,有时候也叫这个为 AXI4-Full;

2023-06-25 16:23:14 2574

2574

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个 AXI4-Lite 源码进行分析。

2023-06-25 16:31:25 4882

4882

以AXI4为例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种: •AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 2142

2142

本文主要集中在AMBA协议中的AXI4协议。之所以选择AXI4作为讲解,是因为这个协议在SoC、IC设计中应用比较广泛。

2024-01-17 12:21:22 4273

4273

Transaction layer的所有功能特性,不仅内置DMA控制器,而且具备AXI4用户接口,提供一个高性能,易于使用,可定制化的PCIe-AXI互连解决方案,同时适用于ASIC和FPGA。

2024-02-22 09:15:46 3

3 AXI总线由一些核心组成,包括AXI主处理器接口(AXI4)、AXI处理器到协处理器接口(AXI4-Lite)、AXI主外设接口(AXI4)、AXI外设到主处理器接口(AXI4-Lite)等。

2024-04-18 11:41:39 2500

2500 AXI4和AXI3是高级扩展接口(Advanced eXtensible Interface)的两个不同版本,它们都是用于SoC(System on Chip)设计中的总线协议,用于处理器和其它外设之间的高速数据传输。

2024-05-10 11:29:50 13096

13096

NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用高性能、顺序

2024-07-18 09:17:19 1440

1440

AMBA AXI4(高级可扩展接口 4)是 ARM 推出的第四代 AMBA 接口规范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 凭借半导体产业首个符合 AXI4 标准的即插即用型 IP 进一步扩展了 AMD 平台设计方法。

2024-10-28 10:46:42 1383

1383

AXI4 总线是第四代 AXI 总线,其定义了三种总线接口,分别为:AXI4、AXI4-Lite 和 AXI4-Stream接口。其中 AXI4 也称为 AXI4-Full 是一种基于地址的高性能

2025-06-24 23:22:33 523

523

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接口,其中AXI4-Lite 和 AXI4 总线接口均可抽象为总线事务,而 PCIe 接口信号可被

2025-08-25 18:53:01 2816

2816

电子发烧友App

电子发烧友App

评论