AD的IP核哪里有?

AD的IP核哪里有

相关推荐

热点推荐

核磁检测同步光调节治疗

各位坛友好!

我们正在推进核磁(MRI)检测同步光调节治疗的项目,核心设备是

LED 阵列头帽+驱动控制板,目前卡在核磁兼容这一关键难题上。

需要实现的目标:设备既不干扰 MRI成像,又能在强磁场

2025-12-30 11:01:10

【乾芯QXS320F开发板试用】ipc核间通信测试过程

先对核0的ipc_ex1_basic中ipc_core0编译:

再对核1的ipc_ex1_basic中ipc_core1编译:导入后就可以编译了

对核0实时调试先调试核0,断点打在开核1时钟后面,将

2025-12-10 16:10:33

隼瞻科技:以DSA技术为核,IP+EDA工具双驱,赋能端侧AI NPU算力效率跃升

设计的需求变化,以及隼瞻科技自研EDA、IP产品如何积极助力客户成功等话题。 端侧AI芯片设计的痛点 “隼瞻科技定位于服务半导体设计公司,提供IP核及EDA工具等解决方案,助力客户芯片构筑核心竞争力,是我们产品的核心价值所在。RISC-V作为一

2025-12-05 13:37:45 4964

4964

4964

4964为什么会有TCP/IP协议?

见了面,完全不能交流信息。因而他们需要定义一些共通的东西来进行交流,TCP/IP就是为此而生。TCP/IP不是一个协议,而是一个协议族的统称。

里面包括了IP协议,IMCP协议,TCP协议,以及我们更加熟悉

2025-12-03 06:28:00

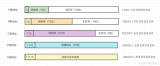

RDMA设计6:IP架构2

扩展的通用 IP 核,在 RoCE v2 高速数据传输系统担任网络物理层的角色。其提供一组主 AXI-Stream 接口和一组从 AXI-Stream接口,用以传输网络包。同时 CMAC 集成块也负责 ETH 层 FCS 的生成与校验,并提供一组寄存器接口用于用户判断链路状态及反馈错误信息等。

2025-11-26 10:24:54

基于AXI DMA IP核的DDR数据存储与PS端读取

添加Zynq Processing System IP核,配置DDR控制器和时钟。7000系列的Zynq可以参考正点原子DMA回环测试设置。

2025-11-24 09:25:50 2881

2881

2881

2881

使用AXI4接口IP核进行DDR读写测试

本章的实验任务是在 PL 端自定义一个 AXI4 接口的 IP 核,通过 AXI_HP 接口对 PS 端 DDR3 进行读写测试,读写的内存大小是 4K 字节。

2025-11-24 09:19:42 3467

3467

3467

3467

IP5219应用方案认证测试放电有辐射超标问题

我们在设计IP5219方案中出现认证测试放电有辐射120M,超标。有高手协助改进吗,如需加外围元件可在下面电路帮我标注下,谢谢。

2025-11-19 15:27:57

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

NVMe AXI4 Host Controller IP1介绍NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令

2025-11-14 22:40:50

Video Processing Subsystem与HDMI示例设计

在撰写本文时,HDMI Transmitter Subsystem IP 核与 Video Processing Subsystem IP 核均有多个示例设计可供使用,但并没有演示将两者功能结合在一起来使用的设计。

2025-11-07 10:35:33 498

498

498

498

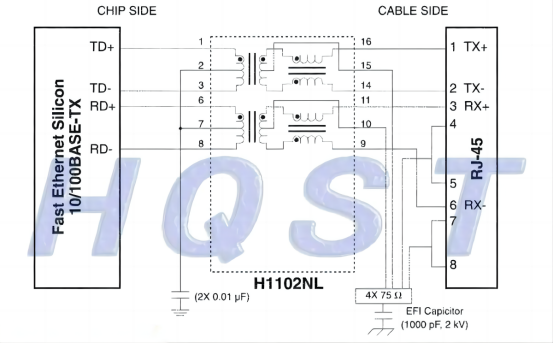

常用的百兆网络变压器与RJ45网口的参考连接电路有哪些,主要注意事项在哪里呢?

Hqst华强盛(石门盈盛)电子导读:一起来了解常用的百兆网络变压器与RJ45网口的参考连接电路有哪些,主要注意事项在哪里呢?

2025-11-06 13:49:58 401

401

401

401

复杂的软件算法硬件IP核的实现

硬件加速 IP 核 HDL 文件的生成分为两个步骤,首先根据将要接入的 SOPC 系统的总线的特性,将算法做适当的包装、暴露相关的接口以及调用方法,即适配总线接口。不同的 SOPC 总线有不同的时序以及

2025-10-30 07:02:09

E203软核提高CPU时钟频率方法

本文将分享我们团队提高E203软核主频的办法。

查阅芯来科技官方出版的《手把手教你设计CPU——RISC-V处理器篇》教材,我们发现,原本设计的E203主时钟域应该是100MHZ

2025-10-29 06:19:19

VDMA IP核简介

VDMA端口信号

S_AXI_LITE:PS端可以通过AXI_LITE协议对IP核进行控制;

S_AXIS_S2MM:视频流(AXI STREAM)输入到IP核的FIFO中

2025-10-28 06:14:54

使用rk3568开发板,核0\\1\\3运行linux,核2运行hal,在核0中怎么关闭核2

使用rk3568开发板,核0\\\\1\\\\3运行linux,核2运行hal,想在内核中通过smc指令完成核0对核2得启动和关闭,文件系统中/sys/rk_amp目录下有个boot_cpu文件,可以发起对核2得开启和关闭操作,但是目前会返回错误,请问如果解决呢

2025-10-27 10:09:54

蜂鸟E203移植到FPGA开发板前的IP核例化工作

的开发板的芯片型号选择对应的芯片。引脚约束文件可以暂时先不加入。

完成创建工程后,将system.v文件设为顶层

例化IP核

由于蜂鸟内部CLK有两个,分别是16MHz高频时钟

2025-10-27 07:35:23

板子的差分时钟如何正确地转化为单端

本组使用的板子是GENESYS2,输入时钟信号为差分时钟信号,而E203使用的时钟都是单端的,所以需要将差分时钟信号转为单端。而通过网络检索,可以得到以下的一种解决方法

解决方法①

在分频IP核中

2025-10-27 07:29:41

E203移植genesys2(差分时钟板)生成比特流文件全过程

(e203_hbirdv2_masterfpgaddr200tsrcsystem.v),并设置为顶层文件。

3.添加IP核,e203需要两个平台相关的IP核,用于时钟控制核复位控制,分别是Processor

2025-10-27 07:16:17

移植蜂鸟e203内核到A7lite开发板上相关问题的解决办法

例化MMCM(可以在建立vivado工程时再例化)来产生上述两个时钟添加clk_div.v文件

代码如下:

可以发现clk_div.v文件与system.v文件的IP核相匹配。

第三步:

打开IP

2025-10-27 06:35:36

蜂鸟E203的浮点指令集F的一些实现细节

数据的握手信号一致。而我们在实现时,无IP核的模块从简,不给模式信号加握手。

有operation信号的IP核:

需注意的是,IP核可以选择添加时钟使能信号,此信号会控制时钟是否翻转,用以

2025-10-24 08:57:20

Vivado浮点数IP核的握手信号

Vivado浮点数IP核的握手信号

我们的设计方案中,FPU计算单元将收到的三条数据和使能信号同步发给20多个模块,同时只有一个模块被时钟使能,进行计算,但结果都会保留,发给数选。计算单元还需接受

2025-10-24 07:01:36

Vivado浮点数IP核的一些设置注意点

Vivado浮点数IP核的一些设置注意点

我们在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定义其计算种类及多模式选择。有时多种计算可以用同一个IP核实

2025-10-24 06:25:22

ram ip核的使用

决定的。 ram 主要用来存放程序及程序执行过程中产生的中间数据、 运算结果等。

rom为只读存储器,只能读取数据而不能向里面写入数据。

本次讲解的ram ip核ram指的是bram,即block

2025-10-23 07:33:21

基于FPGA的DDR控制器设计

可以在Xilinx公司MIG(Memory Interface Generators)IP核的基础上设计得到的。IG IP核是Xilinx公司针对DDR存储器开发的IP,里面集成存储器控制模块,实现

2025-10-21 14:30:16

FPGA搭建DDR控制模块

公司MIG(Memory Interface Generators)IP核的基础上设计得到的。IG IP核是Xilinx公司针对DDR存储器开发的IP,里面集成存储器控制模块,实现DDR读写操作的控制

2025-10-21 10:40:28

用FPGA实现DDR控制模块介绍

Xilinx公司MIG(Memory Interface Generators)IP核的基础上设计得到的。IG IP核是Xilinx公司针对DDR存储器开发的IP,里面集成存储器控制模块,实现DDR读写操作

2025-10-21 08:43:39

灯具IP防护等级测试标准

一、IP防护等级的概念灯具在使用过程中常暴露于灰尘、水汽、雨淋等复杂环境中,为保证其长期稳定工作并防止触电或损坏,国际电工委员会(IEC)制定了防护等级标准,即IP

2025-10-17 16:13:49 1176

1176

1176

1176

配电柜IP等级测试

一、什么是IP等级?IP等级(防护等级)是国际标准化组织(ISO)对电子设备防护性能的一种评估方式,旨在显示设备对外界物质(如固体物体和液体)的保护能力。IP等级由两个数字构成,第一个数字代表防护

2025-10-17 11:37:45 323

323

323

323

学习Linux应该从哪里开始?

在工业控制、边缘计算、人工智能这些领域,有一句几乎约定俗成的话: “会不会 Linux,决定了你能走多远。” 但对很多刚入门的工程师来说,Linux 看起来像个庞大又神秘的世界——命令行、驱动、内核

2025-10-16 09:51:51 357

357

357

357

外壳防护等级(IP代码)全解读

什么是外壳防护等级(IP代码)IP代码,全称为“国际防护等级”,是由国际电工委员会制定的全球通用标准。这一标准旨在为电子设备外壳的防护能力提供一个清晰、统一的评判体系。简单来说,IP代码就是电子设备

2025-10-14 12:13:08 574

574

574

574

安防硬件设备中的防水防尘IP等级代表什么?IP66是什么水平

我们在选择安防硬件厂家的产品时,在规格表或产品详情页中常常会看到一个防护等级的指标,有的是IP65.有的是IP66等级,这些安防设备产品的IP等级高低又分别代表什么呢?下面让天波小编为你简单科普一下

2025-10-13 10:16:19 1648

1648

1648

1648

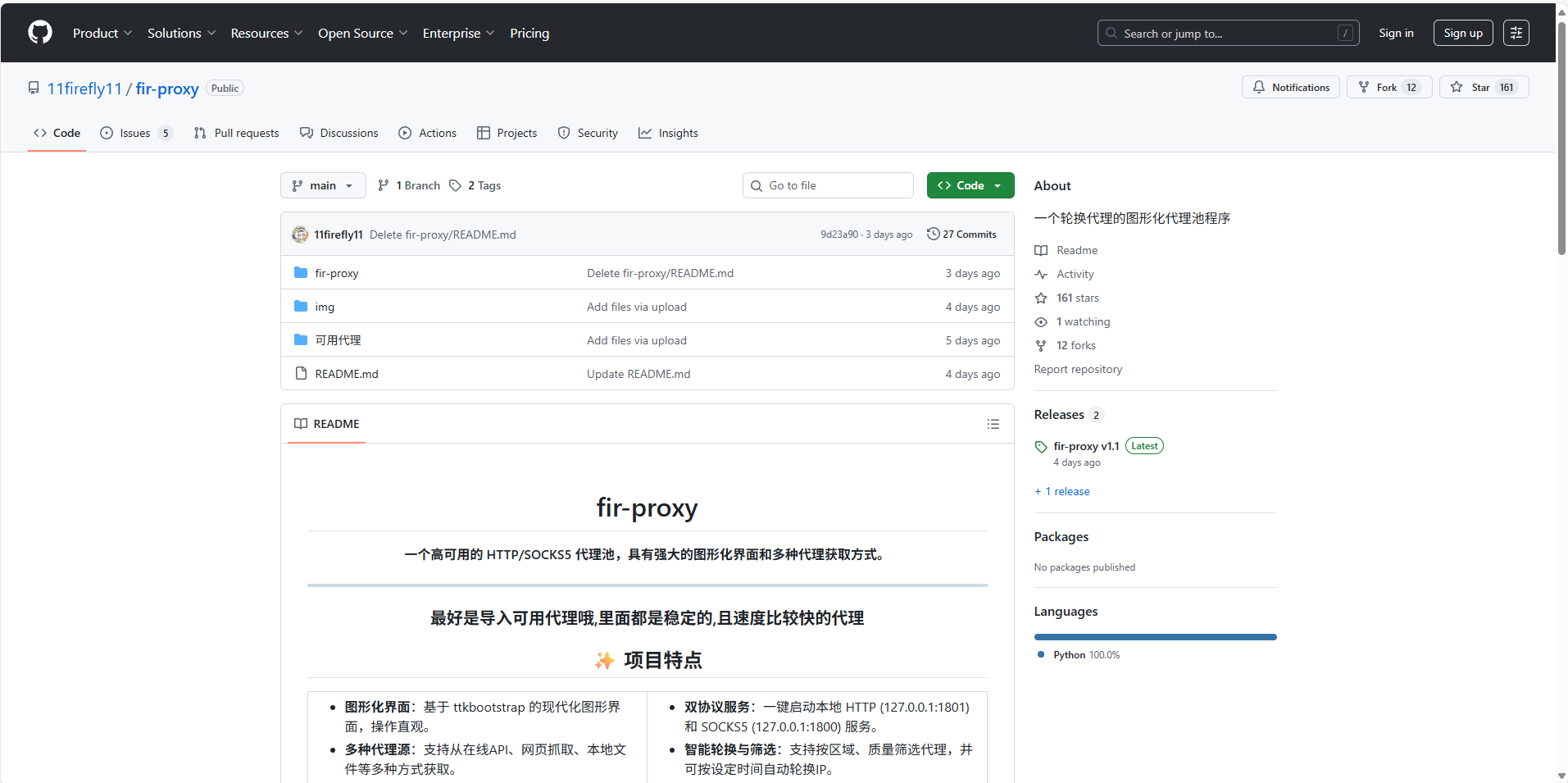

小白也能轻松上手!一招解决IP被封杀难题

—— fir-proxy 。这款开源高可用代理池能在多个IP中智能自动轮换新IP,大幅降低手动操作时间,让你专注于攻击策略,提升演练得分效率。(该项目一个星期的时间就已经有三位数的star,可见质量之高。) 文件下载后,项目需由python编写,按照requi

2025-09-02 10:38:26 475

475

475

475

创飞芯40nm HV工艺OTP IP完成上架

珠海创飞芯科技有限公司实现新突破!我司基于40HV(40nm 1.1V / 8V / 32V high voltage process)工艺制程的一次性可编程存储IP核已在国内两家头部晶圆代工厂经过

2025-08-14 17:20:53 1311

1311

1311

1311请问InConnect 是否可以用实际 IP 而不是用虚拟 IP 映射实际IP ?

但是这样子使用的话,我只能通过这个虚拟IP来连接设备,那样子我的PLC编程软件就不能连接上设备了因为IP和实际的不一样,我能通过什么办法来让映射出来的虚拟IP和我的实际设备IP一致吗?是要需用虚拟网卡还是怎么样子?

2025-08-06 07:54:23

FPGA利用DMA IP核实现ADC数据采集

DMA IP核来实现高效数据传输的步骤,包括创建项目、配置ADC接口、添加和连接DMA IP核、设计控制逻辑、生成比特流、软件开发及系统集成。文章还强调了系统实现中不可或缺的ip_repo文件的重要性和作用。

2025-07-29 14:12:22 4847

4847

4847

4847CNC的IP地址相同冲突如何解决?

在网络世界中,每个设备都需要一个独特的标识来确保信息的准确传输,这个标识就是IP地址。然而,在CNC(数控机床)生产车间中,由于存在多个品牌、不同型号的设备,且这些设备在出厂测试时往往会被配备相同

2025-07-23 14:13:12 537

537

537

537

Altera FPGA 的PIO IP当中bidir和inout选项的区别

PIO IP是FPGA 设计中比较简单常用的IP, 当设置PIO IP的Direction的时候,可以看到有如下4个选项: Input代表这组IO是输入引脚,Output代表这组IO是输出引脚

2025-07-07 11:55:06 2352

2352

2352

2352

单核CPU网关和双核CPU网关有什么区别

单核CPU网关与双核CPU网关的核心区别在于处理能力、多任务效率、性能表现及适用场景,双核CPU网关在多任务处理、复杂计算和响应速度上具有显著优势,而单核CPU网关则更适合轻量级、低负载的简单应用场景。以下是具体分析:

2025-07-05 14:37:45 828

828

828

828VIVADO自带Turbo译码器IP核怎么用?

turbo 译码器IP核没有输出,不知道哪里出了问题,有经验的小伙伴帮忙看看啊

搭建了turbo 译码器IP核测试工程,用Matlab产生的数据源,调用turbo编码器生成编码数据,将编码后的数据给

2025-06-23 17:39:24

如何使用AMD Vitis HLS创建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器。接着会在 AMD Vivado Design Suite 设计中使用此 HLS IP,并使用嵌入式 Vitis 应用控制此 HLS IP。

2025-06-13 09:50:11 1447

1447

1447

1447

稳定、高效、智能:蜂鸟IP如何为技术玩家提供可靠动态IP服务?

在当今数字化时代,网络环境的稳定性和灵活性已成为技术爱好者和专业人士关注的重点。无论是爬虫开发、网络安全测试,还是多地域网络访问需求,一个可靠的动态IP服务能显著提升工作效率,避免因IP限制或网络

2025-06-04 15:58:43 680

680

680

680创飞芯55nm BCD工艺OTP IP实现上架

近日,珠海创飞芯科技有限公司宣布,其自主研发的 55BCD ( 55nm Bipolar-CMOS-DMOS Generic Process) 工艺 OTP IP(一次性可编程存储IP核) 已在一家

2025-05-30 11:31:13 1171

1171

1171

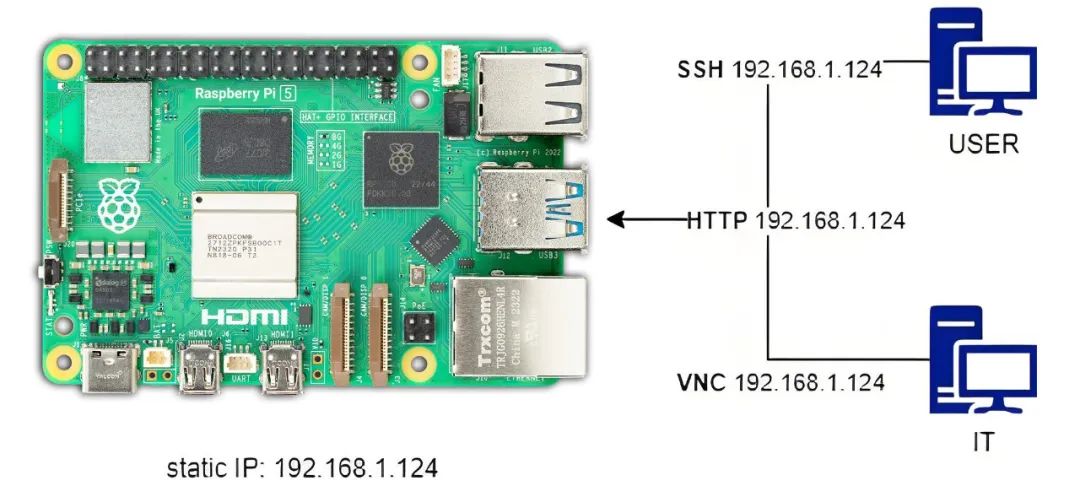

1171树莓派“定居”完全指南:一键设置静态IP,稳定又高效!

当你为树莓派设置静态IP地址时,实际上是为它分配了一个固定地址,该地址不会改变,而动态IP地址则会在设备每次连接到网络时发生变化。在树莓派上设置静态IP地址有诸多好处:稳定访问使用静态IP地址后,你

2025-05-25 08:32:07 1388

1388

1388

1388

JESD204B IP核的配置与使用

物理层的位置,一种是物理层在JESD204 IP里;另外一种是物理层在JESD204 IP外部,需要再配置JESD204 phy IP核进行使用。

2025-05-24 15:05:00 1827

1827

1827

1827

IP防护等级小知识

”。今天小编就来带大家了解一些关于IP等级的小知识。 IP等级的定义 外壳防护等级(IP代码)是针对电气设备外壳防止异物侵入、防尘、防水的特性加以分级,来源是国际电工委员会的标准IEC 60529。我国对应的国家标准为 GB/T 4208-2017。 试验项目

2025-05-23 14:14:18 2472

2472

2472

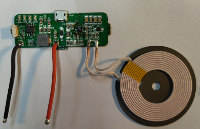

2472ip6826芯片参数:无线充电领域的高效兼容解决方案

英集芯IP6826芯片凭借其高效兼容性和安全性,是无线充电领域的佼佼者。其核心技术双核驱动+动态调压IP6826具有高集成度和灵活性,可适配多种无线充电应用场景。

2025-05-22 08:56:00 870

870

870

870

IP6825+IP5306充电宝:重新定义便携电源的无线充电体验

本文主要介绍了两种充电宝方案:IP6825和IP5306。IP6825是创新解决方案,通过高效充放电和磁吸无线充电将充电宝的便捷性和功能性提升。IP5306芯片集成了多种功能,支持2.1A充电和2.4A放电,适合多合一电源管理。

2025-05-19 08:56:00 1182

1182

1182

1182

智能无人设备从IP核到系统的全流程功能安全问题初探

功能安全是为许多智能无人设备保驾护航的重要措施,因此需要引起从IP到芯片和系统等各环节的重视,除了获得由权威机构在进行全流程审核,覆盖开发流程、测试报告及安全案例完整性之后获得ASIL等级证书之外,设计文档、测试数据、工具认证和持续合规管理都非常重要。

2025-05-15 14:52:46 435

435

435

435

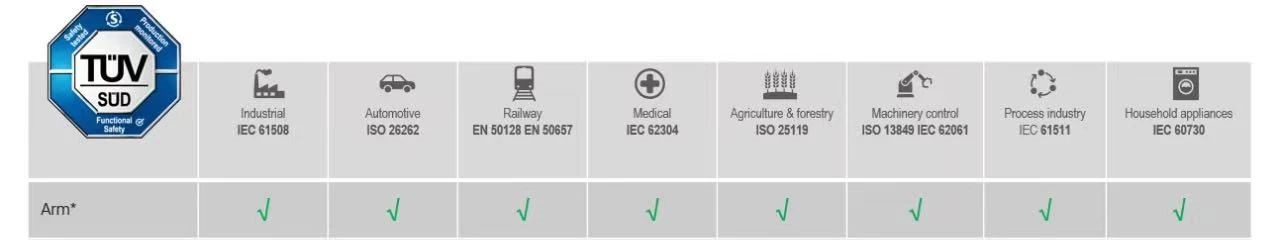

内网穿透和公网ip什么区别

在远程访问、企业组网等场景中,内网穿透和公网IP是两种常见的解决方案,但它们的原理、成本和使用方式截然不同。 以下图片是两者的关键对比: 1. 本质区别 2. 工作原理对比 (1)公网IP方案

2025-05-14 14:18:11 559

559

559

559

Xilinx Shift RAM IP概述和主要功能

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一个 LogiCORE IP 核,用于在 FPGA 中实现高效的移位寄存器(Shift Register)。该 IP 核利用

2025-05-14 09:36:22 912

912

912

912芯耀辉科技出席2025半导体IP产业研讨会

如果说芯片是现代科技的“神经中枢”,那么半导体IP(知识产权核)就是集成电路产业的“技术底座”,构成了芯片设计的重要基石。为推动我国集成电路产业关键核心技术攻关与生态体系建设,助力构建自主可控

2025-05-13 10:06:48 923

923

923

923cypress3014输出的画面在obs上会翻转,在potplayer上显示正常,这种是哪里有问题?

请问输出的画面在obs上会翻转,在potplayer上显示正常,这种是哪里有问题

2025-05-08 08:26:25

vivado IP核cordic中sin和cos的计算

Architectural Configuration选择为并行模式,具有单周期数据吞吐量和较大的硅面积。具有并行结构配置的CORDIC核使用移位相加子级数组并行实现这些移位相加操作。该并形电路的实现规模与(内部精度 * 迭代次数)成正比。

2025-05-03 18:16:00 1393

1393

1393

1393

海外住宅IP代理优势综合分析

海外住宅IP代理凭借其独特的资源特性与技术架构,在跨境电商、数据采集、广告投放等场景中展现出显著优势。以下从核心功能、技术保障、合规性及适用场景等维度进行详细分析: 一、隐匿性与安全性提升 真实IP

2025-04-25 10:28:55 486

486

486

486linux+rtos系统如何适配linux小核屏幕驱动?

我希望使用小核运行lvgl对大核程序进行控制,运行小核lvgldemo的时候发现linux下的屏幕没有做适配,查看dts发现几乎所有的dts都用的是hx8399作为dsi的显示,但是现在市面上

2025-04-25 07:16:03

住宅IP动态化技术应用解析:对比数据中心IP的三大核心优势

在网络安全、数据采集、跨境电商等数字技术领域,IP资源的选择直接影响业务运行效果。本文针对技术开发者与行业用户关注的动态住宅IP特性,对比传统数据中心IP的差异表现,解析其在真实业务场景中的技术优势与应用价值。

2025-04-24 15:34:27 517

517

517

517一文详解Video In to AXI4-Stream IP核

Video In to AXI4-Stream IP核用于将视频源(带有同步信号的时钟并行视频数据,即同步sync或消隐blank信号或者而后者皆有)转换成AXI4-Stream接口形式,实现了接口转换。该IP还可使用VTC核,VTC在视频输入和视频处理之间起桥梁作用。

2025-04-03 09:28:14 2418

2418

2418

2418

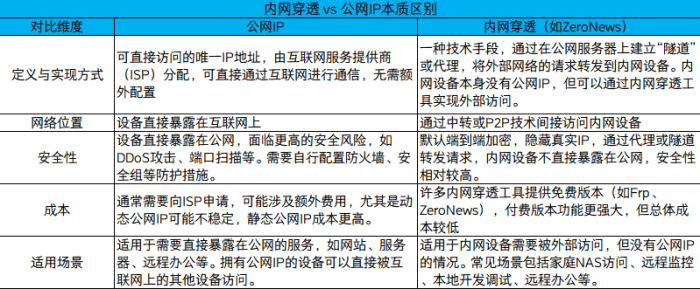

适用于单核、双核和四核应用处理器的PMIC DA9063L-A数据手册

DA9063L-A 是一款功能强大的系统电源管理集成电路(PMIC),适用于单核、双核和四核应用处理器,例如那些基于 ARM® Cortex®-A9和 Cortex-A15 架构的处理器。 *附件

2025-04-01 18:19:46 815

815

815

815

【「芯片通识课:一本书读懂芯片技术」阅读体验】芯片如何设计

SoC芯片的功能和性能模拟。这种SoC芯片的系统结构如下图所示。

从开发角度看,IP由行为级、结构级和物理级三个层次的划分,分别对应三种类型的IP:由硬件描述语言设计的IP软核、完成结构描述的IP固核

2025-03-29 20:57:53

TAG-8000无线高压核相仪操作使用

TAG-8000 无线高压核相仪(以下简称“仪器”)用于两条高压线路并网或环网核相。仪器适合0.22~220kV交流输电线路带电作业和二次侧带电作业,具有高压验电功能。仪器采用无线传输技术,操作安全可靠,使用方便,克服了有线核相仪的诸多缺点。

2025-03-28 17:33:54 0

0

0

0快问快答:防护等级IP68和IP67的有什么区别?如何有效进行防水等级测试

IP68与IP67,代表电子设备顶级防水防尘能力,是高品质的象征。IP68更强悍,可长时深潜;IP67亦卓越,能短时浸泡。精诚工科气密性检测仪,精准模拟IP等级测试环境,以压力衰减等高效方法,结合

2025-03-17 11:01:11 6635

6635

6635

6635

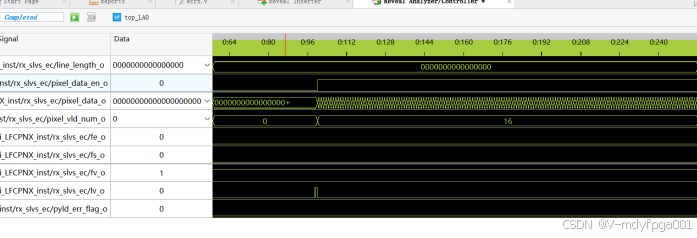

AXI 接口设计避坑指南:AXI接口笔记

AXI接口笔记 第一章 问题记录 第1节 接收数据全0或全1 1.1 问题现象 上图中,pixel_data_o是EC IP核输出的图像数据,正确的话会如上图所示,图像数据每个时钟会变化并且值

2025-03-10 17:21:56 829

829

829

829

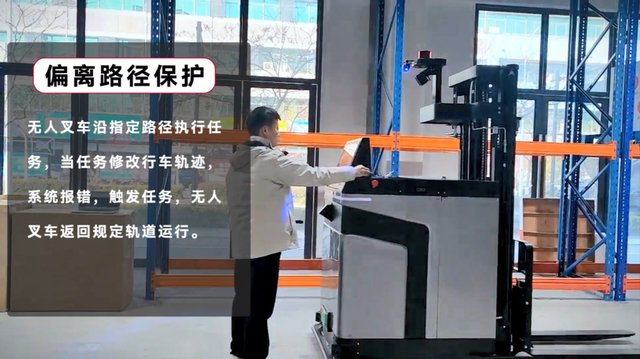

联核科技AGV无人叉车有哪些安全防护措施?

联核科技AGV无人自动叉车的安全配置非常全面,主要包括以下几个方面: 一、基础安全防护 偏离路径保护 :当联核科技AGV自动无人叉车偏离预设路径时,系统会自动触发保护机制,确保AGV无人叉车不会误入

2025-03-10 16:36:49 675

675

675

675

请问哪里有移植RFAL支持ST25DV的文档?

求助:哪里有相关文档介绍

本人想移植一下RFAL支持ST25DV64KC,用于与另外一个NFC模块进行数据通信,哪个大佬帮忙分享一下文档

2025-03-10 08:13:14

Imagination利用Cadence系统设计与验证工具开发节能半导体IP

IP 模块,旨在为客户提供优质产品。作为分块式延迟渲染技术的创造者,Imagination 有能力生产节能处理器

2025-03-07 19:11:44 1185

1185

1185

1185

联核科技AGV无人叉车的应用场景有哪些?

联核科技AGV无人自动叉车在多个应用场景中均展现出卓越的性能和广泛的应用价值。下面是针对每个应用场景的简要概括、适用车型及其功能的详细介绍联核科技官网-AGV叉车十大品牌-无人叉车厂家-自动化叉车

2025-03-07 15:33:15 677

677

677

677

防水等级大揭秘:IPX7、IPX8、IP67、IP68、IP69,到底有啥不一样

您是不是还在为各种电子产品上眼花缭乱的防水标识感到困惑?别担心!精诚工科今天就带您一次性彻底搞懂IPX7、IPX8、IP67、IP68、IP69这些常见的防水等级,让您从此选购防水产品不再懵圈!一

2025-03-03 11:19:15 26711

26711

26711

26711

Vivado FIR IP核实现

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件来破解。如果是个人学习,现在网络上流传的license破解文件在破解Vivado的同时也破解

2025-03-01 14:44:19 2709

2709

2709

2709

晶科能源与中广核新能源高层会谈

近日,晶科能源股份有限公司(简称“晶科能源”)与中国广核新能源控股有限公司(简称“中广核新能源”)高层在晶科能源总部举行了会谈,双方就深化合作、共谋绿色未来进行了深入交流。中广核新能源党委副书记、总经理李光明,晶科能源董事长李仙德等双方相关领导出席了此次会谈。

2025-02-20 18:20:07 903

903

903

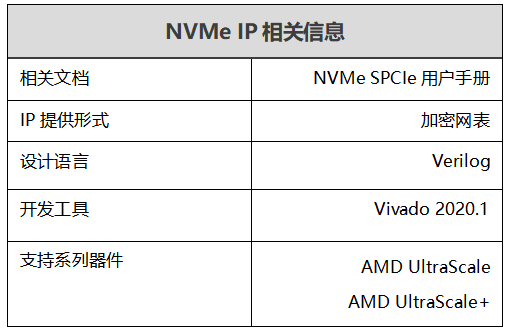

903ALINX NVME SPCle IP 特性详解

。 NVMe SPCle IP 正是为这样的场景量身定制。通过结合 PCIe 软核 IP 与 NVMe 主机控制器,让开发人员 在无硬核的情况下,也能轻松接入 NVMe SSD ,突破了传统存储方案的硬件限制。 简单来说, NVMe SPCle IP 的存在,让高性能存储不再是高成本设备的专属

2025-02-20 15:35:10 831

831

831

831

Linux ip命令常用操作

Linux ip命令常用操作 在Linux系统中,ip命令是用于管理网络接口和路由的强大工具。相比于旧的 ifconfig命令,ip命令提供了更多的功能和更细粒度的控制。本文将详细介绍 ip命令

2025-02-19 10:23:11 1192

1192

1192

1192人工智能的下一站在哪里

DeepSeek的爆发进一步推动了AI行业的发展速度,这让人们不得不想象AI的下一站在哪里?维智科技所深耕的时空大模型与AI发展的逻辑轨迹又是如何联系的?

2025-02-14 10:27:55 855

855

855

855IP地址查询技术

IP查询****的价值 根据2023年国际互联网数据中心统计,全球每天产生的IP查询请求超过50亿次,这一数字就能够清晰的看出广大群众对于IP查询技术的需求以及它的价值。 而传统IP查询技术

2025-02-12 11:13:11 805

805

805

805

DAC5682Z两通道输出有相差是怎么回事?

以上是我的应用场景:通过CDCE62005提供DAC5682Z的工作时钟和FPGA的工作时钟;CLK0和CLK1都是200MHz的时钟,在FPGA内部使用DDS IP核生成一个20MHz的正弦

2025-02-12 08:24:16

美国多ip服务器租用配置步骤

美国多IP服务器租用是一种提供多个独立IP地址的服务器租赁服务,主要用于站群建设和SEO优化。以下是关于美国多IP服务器租用的详细介绍,主机推荐小编为您整理发布美国多ip服务器租用配置步骤。

2025-02-08 17:12:17 923

923

923

923sdwan组网需要固定ip吗?

SD-WAN组网并不一定需要固定IP地址。以下是具体说明: 1、不需要固定IP的情况 动态IP可满足基本需求:SD-WAN技术本身具有灵活性,能够基于动态IP地址进行网络连接和流量管理。在许多应用场

2025-02-08 12:37:17 1014

1014

1014

1014如何理解芯片设计中的IP

本文主要介绍如何理解芯片设计中的IP 在芯片设计中,IP(知识产权核心,Intellectual Property Core)是指在芯片设计中采用的、已经开发好的功能模块、设计或技术,它可以是硬件

2025-02-08 10:43:45 2349

2349

2349

2349新加坡共享主机怎么设置ip

在新加坡设置共享主机的IP地址,通常涉及多个步骤,包括评估需求、选择服务商、配置网络等。以下是一个详细的设置指南,主机推荐小编为您整理发布新加坡共享主机怎么设置ip。

2025-01-24 11:47:08 829

829

829

829Andes晶心科技推出AndesCore AX66乱序超纯量多核处理器IP

Andes晶心科技(Andes Technology)作为高效能、低功耗、32/64位RISC-V处理器核的领先供货商及RISC-V国际组织的创始顶级会员,今日宣布推出支持RVA23规范的AndesCore AX66乱序超纯量多核处理器IP。

2025-01-23 11:05:26 1807

1807

1807

1807Profinet从站转EtherNet/IP从站网关

Profinet从站转EtherNet/IP从站网关 SG-PN-EIP(S)-220 功能概述 本产品是PN(Profinet)和EtherNet/IP网关,使用数据映射方式工作。 本产品在PN侧

2025-01-21 17:16:11 909

909

909

909

XADC IP核介绍

) ADC 和片上传感器。其中12位指的是ADC转换的精度,1MSPS说的是采样速率。如图所示,是XADC在FPGA内部电路的逻辑示意,注意区别于IP核形成的电路。 1.图中1部分是温度传感器和电压传感器,可监测如图所示的多组电压。 2.图中2部分是FPGA bank上的引脚。可以用来接模拟源,总共有

2025-01-15 16:53:59 2235

2235

2235

2235

使用IP核和开源库减少FPGA设计周期

/prologue-the-2022-wilson-research-group-functional-verification-study/),70% 的 FPGA 项目落后于计划,12% 的项目落后计划 50% 以上。 为此,很多FPGA厂商都在自己EDA工具里嵌入IP减少FPGA项目的开发周期,使用 IP 是一种有助于实现按时、高质量且经济高效的项目交付的方法。

2025-01-15 10:47:37 1245

1245

1245

1245

国外多ip服务器核心优势

国外多IP服务器是指配备有多个独立IP地址的服务器,这些服务器通常位于国外。主机推荐小编为您整理发布国外多ip服务器核心优势,以下是对国外多IP服务器的详细解析。

2025-01-08 09:55:38 745

745

745

745ALINX发布100G以太网UDP/IP协议栈IP核

ALINX近日宣布,基于AMD 100G以太网MAC IP,成功开发出全新的100G以太网UDP/IP协议栈IP核。该IP核在数据传输方面表现出色,MTU支持高达9000Bytes,采用标准

2025-01-07 11:25:25 1252

1252

1252

1252 电子发烧友App

电子发烧友App

评论