电子发烧友网报道(文/黄晶晶)在这个事事皆AI的年代,端侧AI需求变得多种多样。面向专用场景的专用处理器日益被厂商所接受。隼瞻科技创始人曾轶日前在2025湾芯展上接受媒体采访,分享了当前处理器设计的需求变化,以及隼瞻科技自研EDA、IP产品如何积极助力客户成功等话题。

端侧AI芯片设计的痛点

“隼瞻科技定位于服务半导体设计公司,提供IP核及EDA工具等解决方案,助力客户芯片构筑核心竞争力,是我们产品的核心价值所在。RISC-V作为一个通用架构,拓展到CPU\NPU\DSP等领域时,我们发现所有处理器的通用架构与客户产品有一定的Gap。在CPU上,体现为算法在CPU上运行效率不高的问题。在NPU上,则反应出大模型在NPU架构上算力展现不充分的问题。”曾轶说道。真正给客户带来价值的不是通用处理器架构,而是在此基础上根据客户特定需求进行调优,让客户的芯片产品具有竞争力。

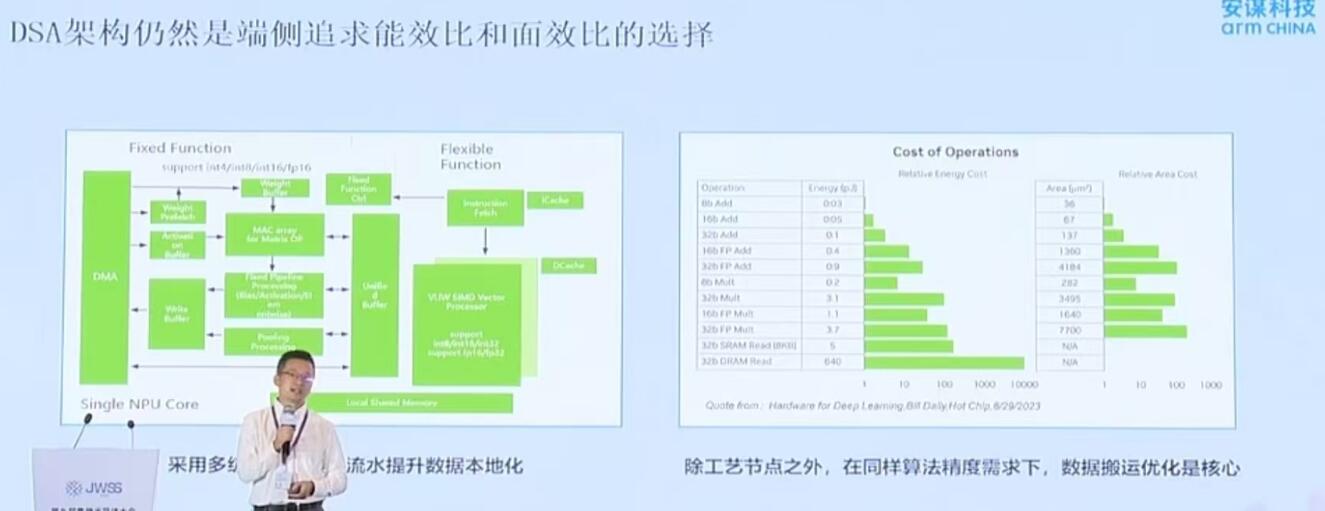

在实践中,隼瞻科技提出的 DSA方法论得到越来越多客户的认可,并将这一DSA方法论延伸到NPU领域,帮助客户优化处理器核。曾轶分析,端侧AI芯片的关键需求包括本地部署专用模型、极低的功耗和更快的响应。例如传统的音频芯片要引入AI,受限于芯片的大小,NPU算力要优化到1Tops以下,并且实时性要求高,中断响应速度要是普通CPU的三分之一,同时功耗进一步降低。

曾轶认为,端侧AI芯片本质上是对场景化的的定制,呈现需求多且硬件要求严苛的特点。其芯片设计关注的焦点不再是单纯的CPU,而是CPU、NPU、DSP的协同,更进一步则是Chiplet技术。“端侧AI芯片不仅是单核性能的提升,而且负载瓶颈、存储内存池优化等都需要研发,大公司有专门的技术专家,而大多数芯片设计公司不具备这样的人员配置。”

因此,隼瞻科技提供IP、DSA方法论以及EDA工具的整套解决方案,用EDA平台承载碎片化,从编译器到软件工具链、接口规格等实现整条链路的统一。从而帮助客户降低AI芯片开发难度,提升芯片设计效率。

以先进的RISC-V DSA架构和EDA工具协同创新

今年7月,隼瞻科技推出“智翼”系列端侧 AI 融合解决方案,以先进的RISC-V DSA (Domain Specific Architecture)架构为基础,借助 ArchitStudio处理器敏捷开发平台的强大能力,可快速高效地进行处理器定制与优化。搭配可灵活定制适配多元模型的NPU模块,能够根据不同应用场景和算法,精准匹配各类 AI 模型,实现高效的计算处理。

此外,隼瞻科技还在持续强化在定制化场景的深度布局。例如与中移芯昇达成的深度合作,聚焦 RISC-V 技术场景落地与标准适配。中移芯昇牵头制定国内 RISC-DSP 扩展指令团体标准(RISC-dsp-w),为 5G/6G 通信、空天地一体化等场景提供开源技术基座,并完成了从指令集定义、软件工具链开发、VDSP 设计到通信芯片落地的全流程闭环。隼瞻科技则以自研 DSA 处理器敏捷开发平台 ArchitStudio 为核心,适配中移芯昇的 VDSP IP 及 RISC-dsp-w 指令集,为开发者提供 “指令集 + IP + 开发工具” 的全栈支持,降低技术应用门槛;未来,双方联合探索 RISC-V 在 AI、车规等新兴领域的应用落地,助力指令集标准进一步完善。

针对当前很多模型适配NPU存在数据稀疏等问题,隼瞻科技基于模型和NPU架构的DSA,推出NPU工具,帮助客户针对NPU进行调优。此外,今年隼瞻科技还将推出针对大核CPU加大算力NPU的EDA工具和解决方案,助力客户在具身智能、端侧一体机等新兴领域的AI需求。

曾轶表示,自今年初DeepSeek掀起端侧AI热潮之后,整个芯片设计行业正在从一个传统的SoC平台向更新的面向算力的芯片研发平台演进。而这为EDA、IC设计企业都创造了更多的创新机会。

发布评论请先 登录

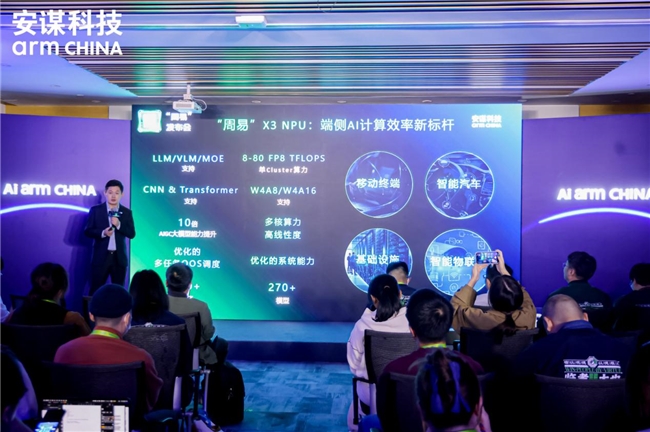

安谋发布“周易”X3 NPU,破局AI算力,智绘未来蓝图

AI体验跃迁,天玑9500用双NPU开创端侧AI新时代

天玑9500 性能大爆发!NPU AI算力或达100TOPS

隼瞻科技:以DSA技术为核,IP+EDA工具双驱,赋能端侧AI NPU算力效率跃升

隼瞻科技:以DSA技术为核,IP+EDA工具双驱,赋能端侧AI NPU算力效率跃升

评论