AXI接口笔记

第一章问题记录

第1节接收数据全0或全1

1.1问题现象

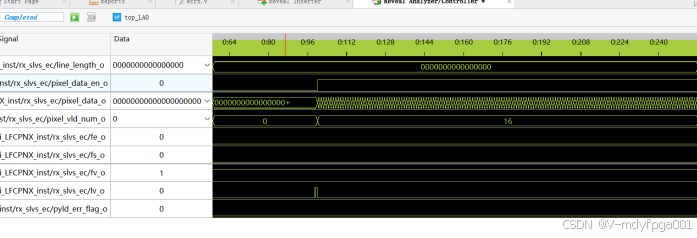

上图中,pixel_data_o是EC IP核输出的图像数据,正确的话会如上图所示,图像数据每个时钟会变化并且值是不固定的。

本次出现的错误现象是:pixed_data_o是有输出的,但输出全是0或者是全是1,并且在最后一个像素出现pyld_err_flag_o的错误指示。

1.2问题原因

经过LATTICE的原厂工程师定位,确定是IP核导致的reveal显示问题,需要重新安装EC的IP核。

1.3解决方法

安装EC的IP核,安装文件:F:svnmdy_flow_common2_design8_LVDS4_mdySlvdsEclatticesemi.com_slvsec_rx_1.2.0.ipk

安装过程:

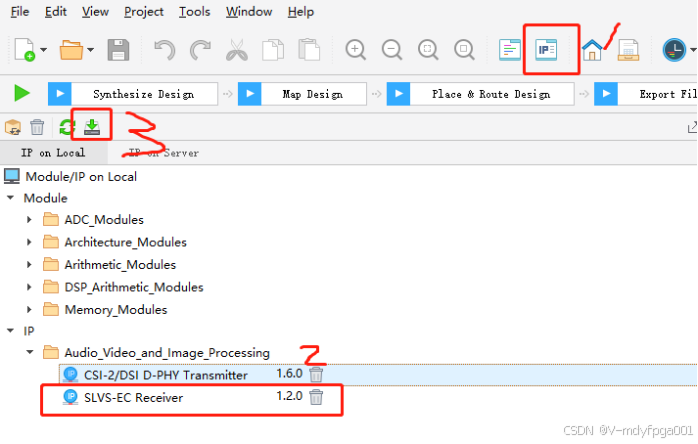

1.3.1.打开LATTICE的软件radiant

1.3.2.打开图中1所示的IP Catalog,显示2是否存在,如果存在就删除;然后点击上图3所示的安装位置。

1.3.3.选择安装文件,接提示要求安装即可。安装完成后,在上图中2的位置将又再出现。

1.3.4.重装生成IP核。

第2节接收不到任何东西

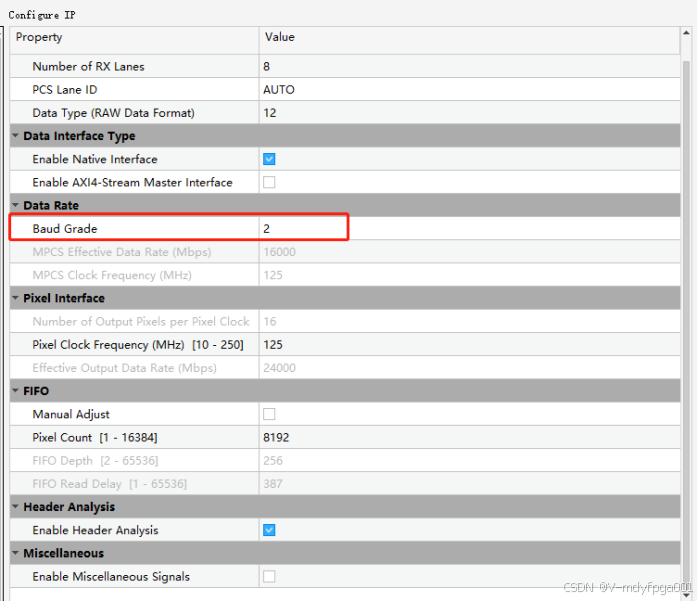

2.1.如果SERDES速率是5G,则BAUD GRADE选用3;如果是2.5G,则选用2;千万不要搞错。

2.2.综合工具要改为:synplify pro。使用LSE将出现不稳定情况,综合后将出现全部接收不到的情况,不稳定。

2.3.使用serdes IP核,去接收数据,看是否有错误提示。注意,本次定位,可以看到信号质量挺好,眼图也是很好的,但从SERDES上看就是有误码。怀疑是频偏问题导致的,在摄像头一侧,修改了时钟线,问题解决。

审核编辑 黄宇

-

接口

+关注

关注

33文章

9600浏览量

157622 -

AXI

+关注

关注

1文章

145浏览量

18014

发布评论请先 登录

利用开源uart2axi4实现串口访问axi总线

使用AXI4接口IP核进行DDR读写测试

如果想运用蜂鸟E203给的一个AXI接口,只需要自己写一个AXI协议的从机就行吗,蜂鸟的cpu核需要改动什么吗?

将e203 例化AXI总线接口

AXI GPIO扩展e203 IO口简介

京东商品详情接口实战解析:从调用优化到商业价值挖掘(附避坑代码)

关于AXI Lite无法正常握手的问题

RDMA简介9之AXI 总线协议分析2

RDMA简介8之AXI 总线协议分析1

NVMe IP之AXI4总线分析

NVMe简介之AXI总线

AXI 接口设计避坑指南:AXI接口笔记

AXI 接口设计避坑指南:AXI接口笔记

评论