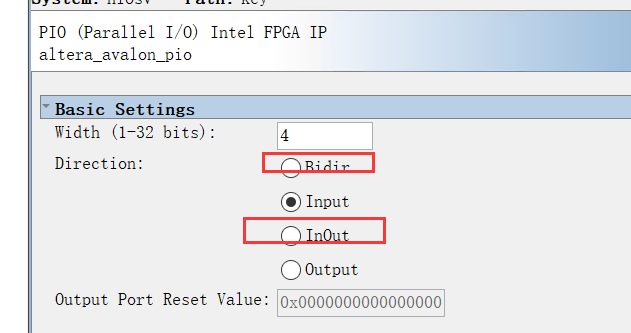

PIO IP是FPGA 设计中比较简单常用的IP, 当设置PIO IP的Direction的时候,可以看到有如下4个选项:

Input代表这组IO是输入引脚,Output代表这组IO是输出引脚,这些很好理解,但Bidir和InOut都表示双向的意思,它们有什么区别吗?

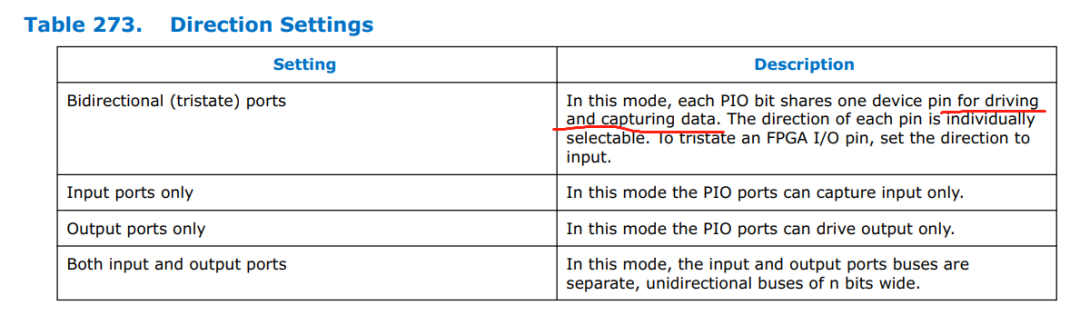

参考28.4.1.2. Direction (intel.com)可知:

bidir,指n位宽的信号中的每一位都可以单独/分别设置为读或是写。

inout,指将n位宽的信号,全设置为读或全部设置为写,但是不能要求其中某些位读而某些位为写。

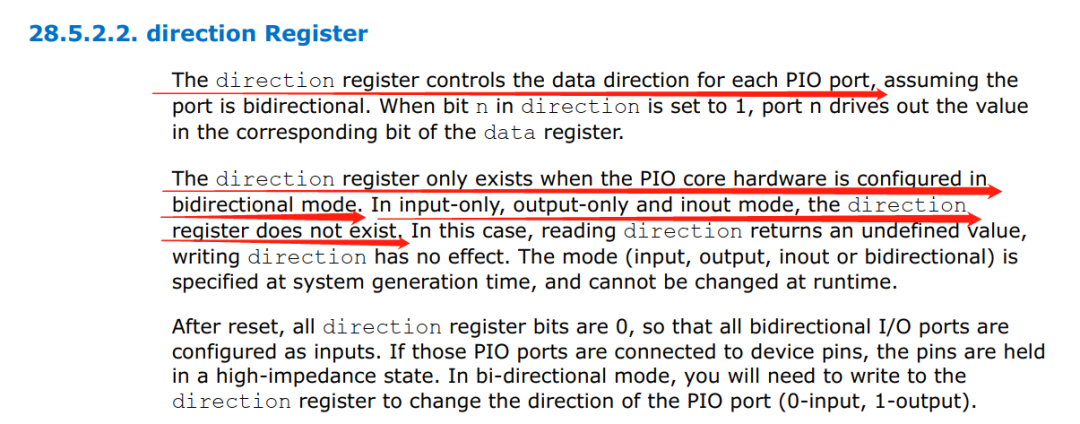

只有设置为bidir模式的时候,才存在direction寄存器,用于控制某个I/O端口用于读(input),还是用于写(output):

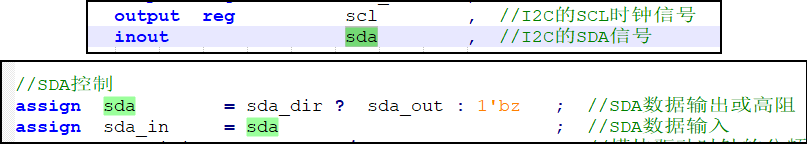

不过在Altera PIO IP之外,其他地方在用bidir和inout表达的时候,bidir(bidir是“bidirectional”的缩写)更侧重于表示双向的特性,是一个概念性的描述;而inout是硬件描述语言中用于声明双向信号或端口的关键字,是一种具体的语法形式。例如在VHDL和Verilog中,都使用inout关键字来实现bidir功能,用于实现双向的接口或总线,如I2C等总线。

I2C的信号线电路设计参考如下:

-

FPGA

+关注

关注

1663文章

22493浏览量

638947 -

Altera

+关注

关注

37文章

828浏览量

159097 -

友晶科技

+关注

关注

0文章

8浏览量

7162 -

PIO

+关注

关注

0文章

20浏览量

6628

原文标题:【答疑解惑】Altera FPGA 的PIO IP当中bidir和inout选项的区别

文章出处:【微信号:友晶FPGA,微信公众号:友晶FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

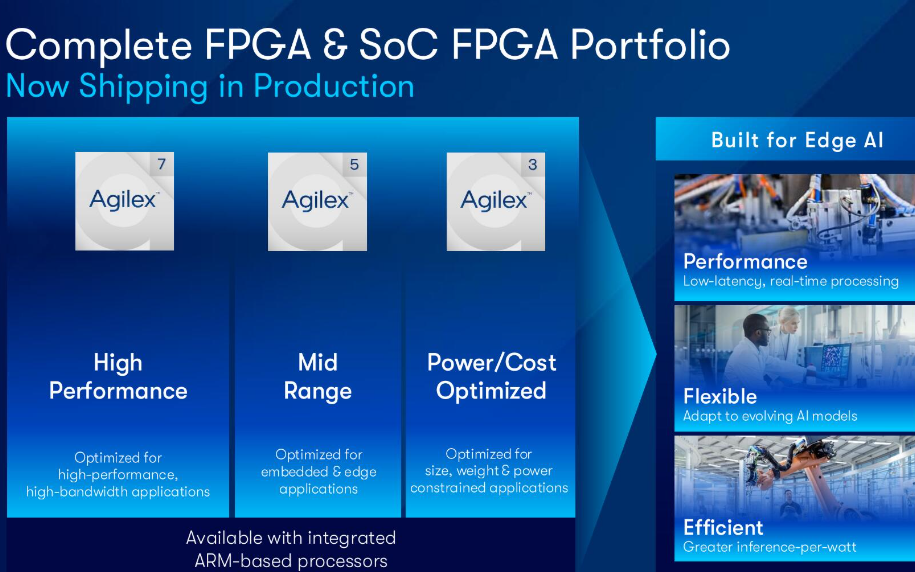

Altera三大FPGA系列产品生命周期支持延至2045年

Altera Agilex FPGA与SoC实现更智能的AI

Altera即将亮相Embedded World 2026

Altera携手合作伙伴共建FPGA创新未来

Altera Agilex 5系列FPGA与SoC产品荣膺2025全球电子成就奖

Altera全新推出MAX 10 FPGA封装新选择

Altera任命Sandeep Nayyar为首席财务官

Altera进一步扩展 Agilex™ FPGA 产品组合,全面提升开发体验

银湖资本完成对Altera 51%股权的收购

使用Altera SoC FPGA提升AI信道估计效率

Altera Agilex 3 FPGA和SoC产品介绍

Altera FPGA 的PIO IP当中bidir和inout选项的区别

Altera FPGA 的PIO IP当中bidir和inout选项的区别

评论