电子发烧友网报道(文/黄晶晶)前段时间,三星、SK海力士、美光等DRAM大厂已计划陆续退出部分DDR4市场,将产能转向DDR5、LPDDR5和HBM。由此引发DDR4供应链波动,同时在供给不足的担忧

2025-06-19 00:54:00 10158

10158

RK3576与RK3588系列核心板全新升级全面搭载高带宽LPDDR5内存LPDDR5加持,核心性能迎来质的飞跃作为新一代低功耗内存技术,LPDDR5相较于LPDDR4/4X,堪称“性能与能效的双重

2025-12-29 16:38:27 5677

5677

ICU-X0201 Hello Chirp示例应用用户指南 在嵌入式产品中集成超声传感器时,开发合适的应用程序是关键的一环。InvenSense的ICU-X0201 Hello Chirp示例应用为

2025-12-26 10:25:09 204

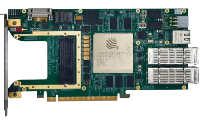

204 PCIE736是一款基于PCIE总线架构的4路QSFP28100G光纤通道适配器,该板卡具有1个PCIeGen3x16主机接口、一共4个QSFP28100G光纤接口,可以实现4路

2025-12-23 15:54:35 509

509

TPD3S0x4:USB接口的高效保护解决方案 在电子设备的设计中,USB接口的稳定性和安全性至关重要。今天,我们就来深入了解一下德州仪器(TI)的TPD3S0x4系列产品,它为USB主机端口提供了

2025-12-22 15:15:23 281

281 Ø支持PCIe 2.0,3.0,4.0速度;PCIe x4,x8,x16链路宽度Ø支持64,128,256,512-bit数据路径Ø64-bit源地址,目的地址,和描述符地址Ø多达8个独立

2025-12-11 11:07:02

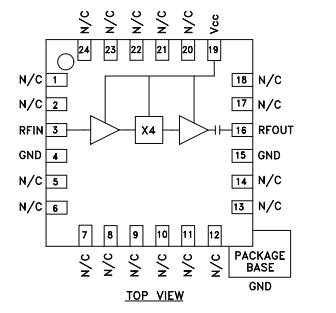

。X4DS35Z1-100G采用用户友好的 Xinger风格表面贴装封装,高度仅 0.73mm,便于集成至紧凑型系统。核心参数频段范围:3300-4200 MHz(覆盖5G中高频段及部分卫星通信频段)功率容量:平均功率 1瓦

2025-12-05 09:19:54

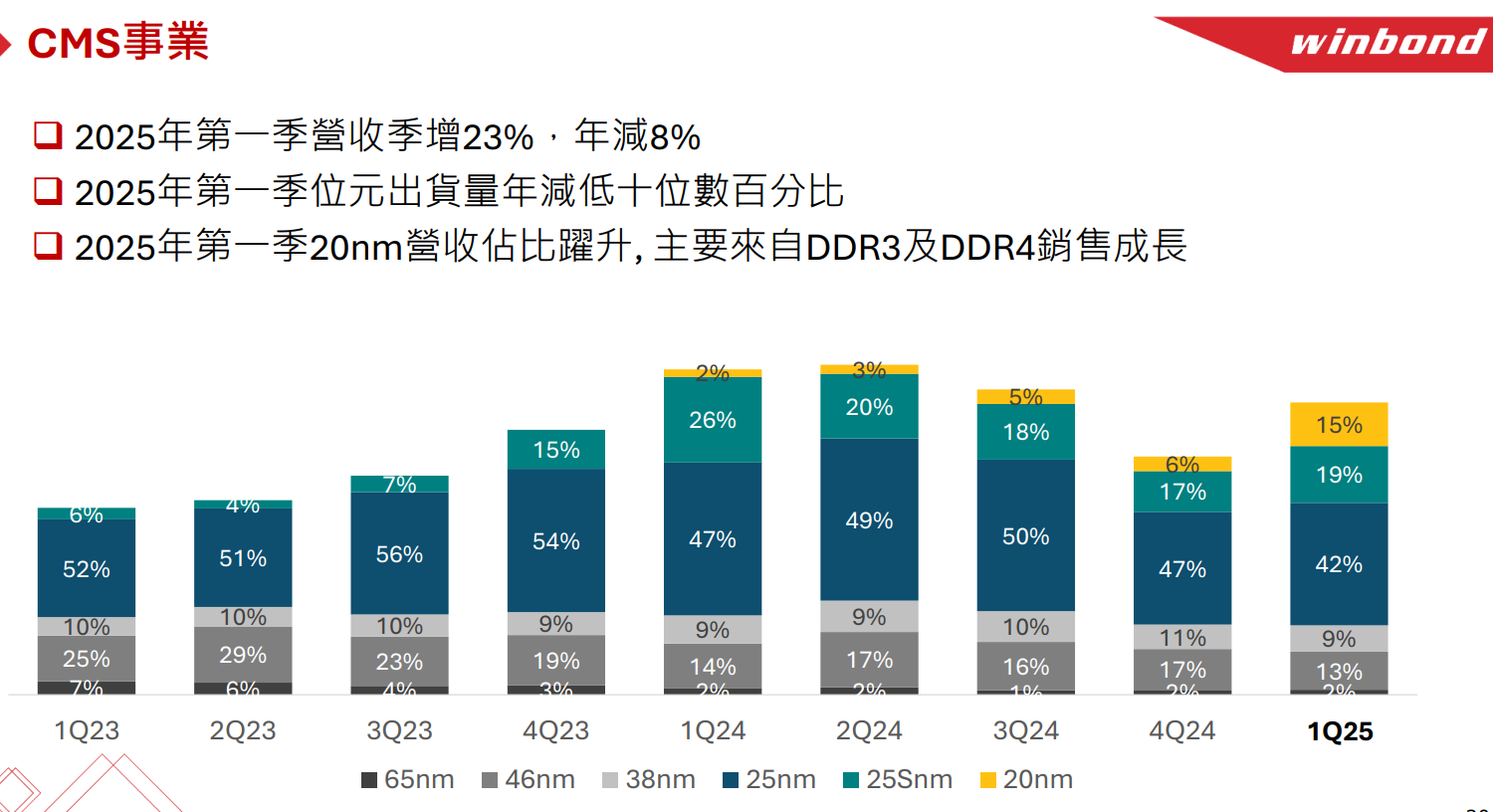

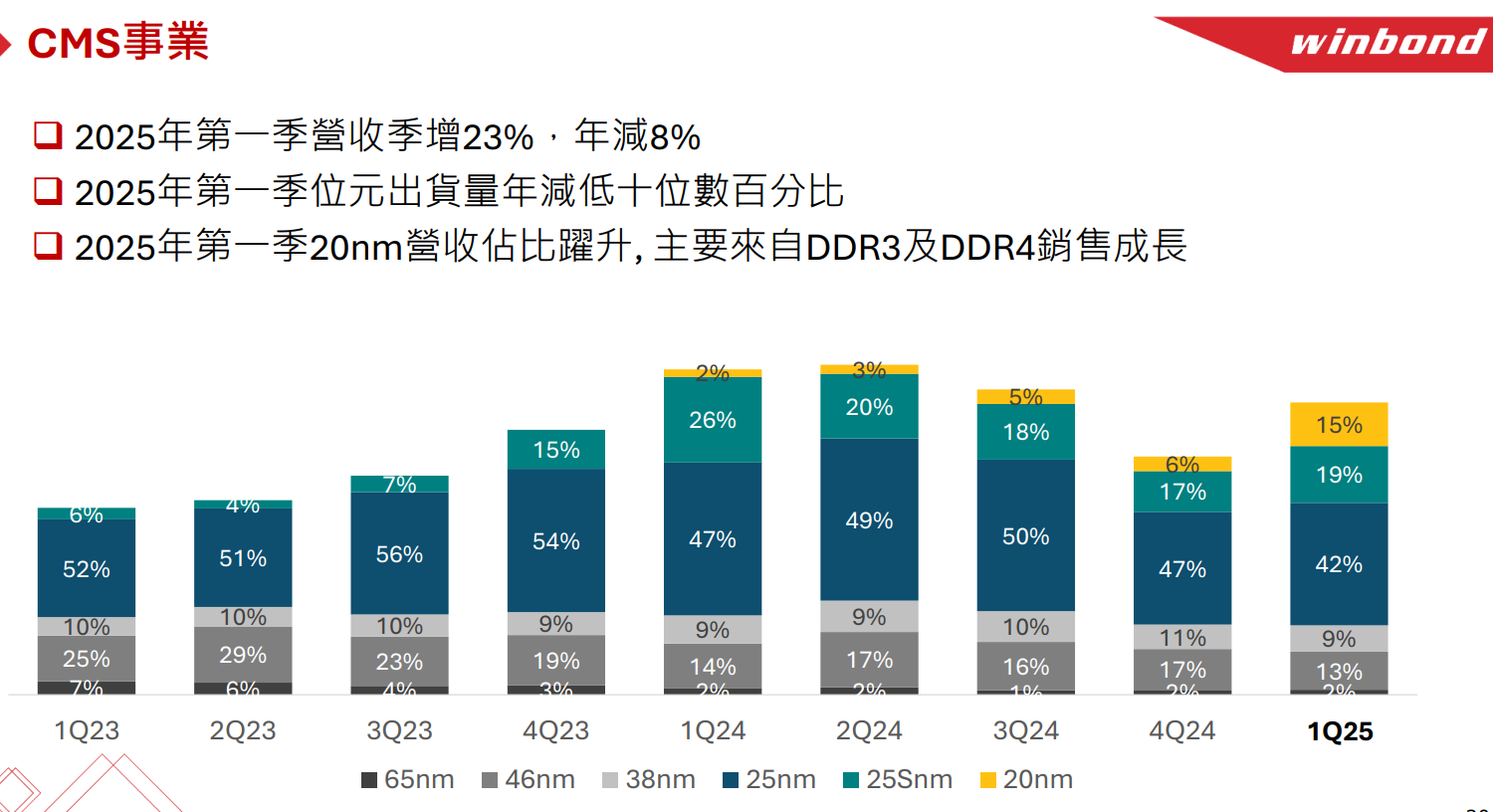

2025 年 12 月 3日,中国苏州 — 全球半导体存储解决方案领导厂商华邦电子今日宣布推出全新 8Gb DDR4 DRAM,该产品采用华邦自有先进 16nm 制程技术,提供更高速度、更低

2025-12-03 16:44:28 712

712

。

该模块默认配备 8GB LPDDR4 内存和 16GB eMMC 闪存,内置千兆以太网 PHY 芯片,以及 WiFi 5 + 蓝牙 4.1 无线模块。

2025-11-28 16:57:59 2056

2056

;

MT41K512M16VRP-107 AAT:P22000;

MT40A1G8SA-062E:E 22000

MY40A256M16LY-062E:F 68000

NT5AD512M8E3-JRI DDR4 512×8 98K

2025-11-27 15:58:19

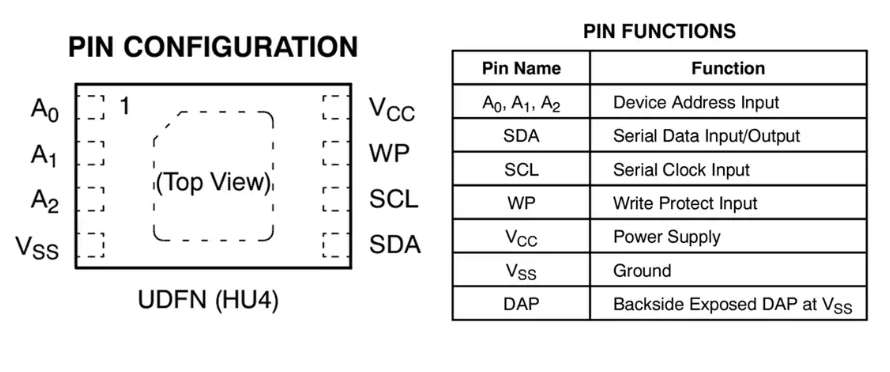

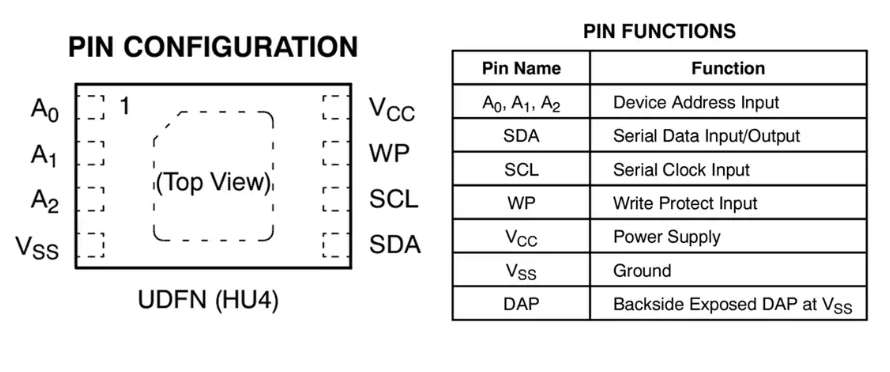

在电子设计领域,对于DDR4 DIMM的设计,EEPROM的选择至关重要。N34C04作为一款专门为DDR4 DIMM设计的EEPROM Serial 4 - Kb器件,实现了JEDEC

2025-11-27 14:42:12 306

306

电子发烧友网综合报道,11月24日,兆易创新高管在2025年第三季度业绩说明会上表示,公司利基型DRAM产品量价齐升,公司今年新量产的DDR4 8Gb较快抢占份额,进入第三季度销量已经与DDR4

2025-11-26 11:58:36 5359

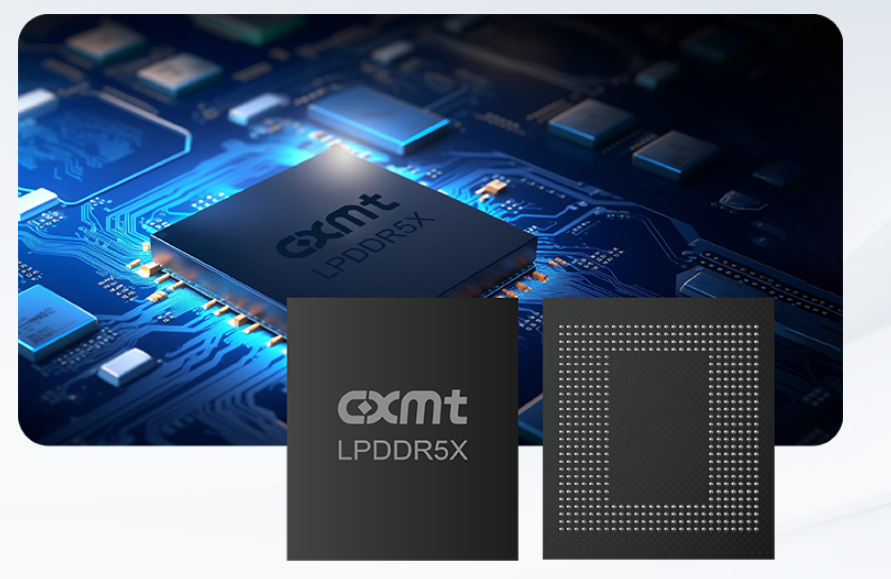

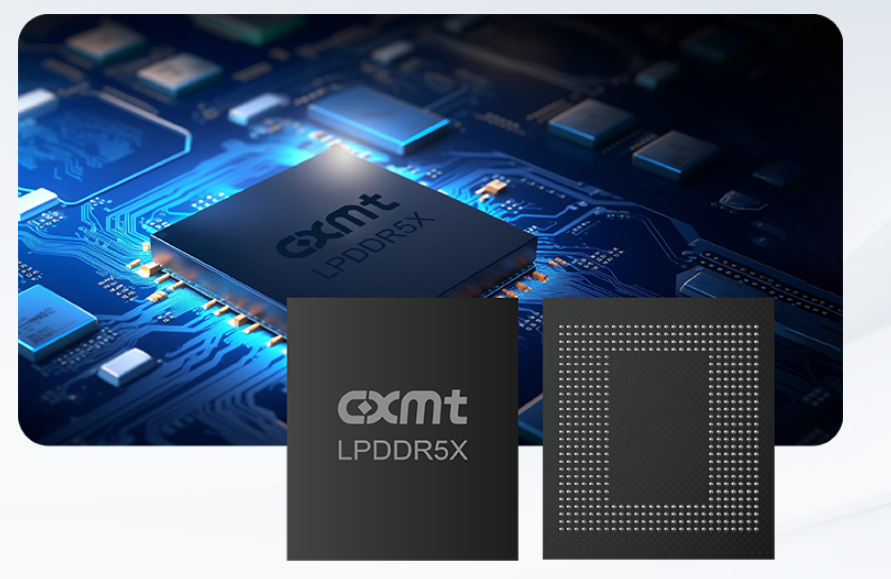

5359 电子发烧友网综合报道,近日,长鑫存储首次全面展示DDR5和LPDDR5X两大产品线最新产品。 长鑫存储最新的DDR5产品是中国首个自主研发的DDR5。该产品系列最高速率达8000Mbps,最高

2025-11-25 08:27:00 8132

8132

本章的实验任务是在 PL 端自定义一个 AXI4 接口的 IP 核,通过 AXI_HP 接口对 PS 端 DDR3 进行读写测试,读写的内存大小是 4K 字节。

2025-11-24 09:19:42 3467

3467

都发布了相关切换举措。 瑞芯微 RK3588 适配长鑫存储 LPDDR5 系列芯片 由于DDR4、LPDDR4 等前代产品的供应链紧张态势难以缓解,瑞芯微自 2021 年起便启动 LPDDR5/5X 颗粒适配工作,历经近五年技术沉淀与实践验证,已积累丰富的产品化经验。瑞芯微表

2025-11-23 07:44:00 9240

9240

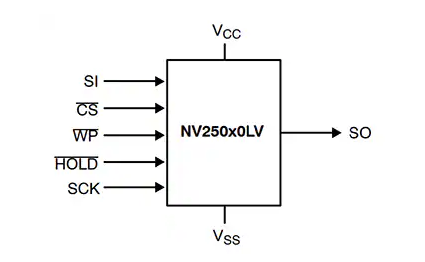

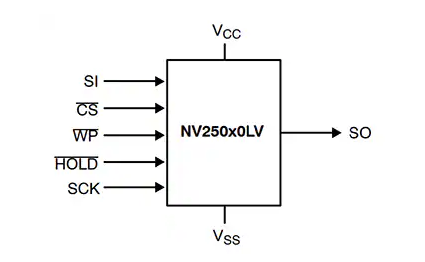

安森美 (onsemi) NV250x0LV低电压车规级一级串行EEPROM是1Kb、2Kb和4Kb SPI串行EEPROM器件,内部分别组织为128×8、256×8和512×8位。安森美

2025-11-22 10:53:07 917

917

应用。

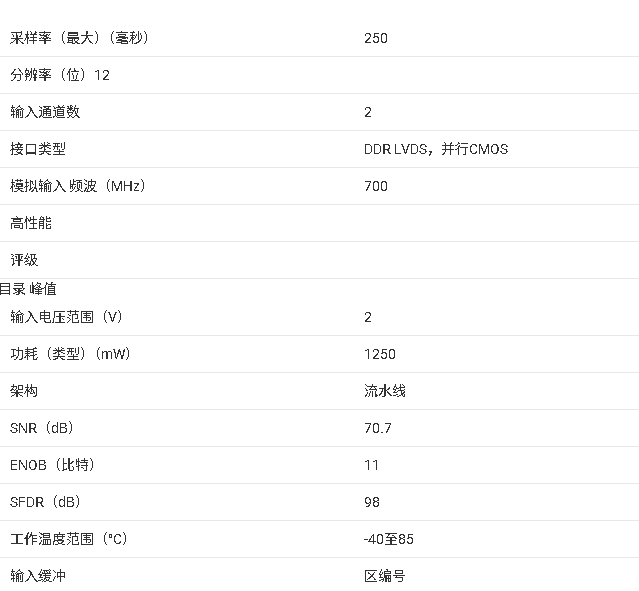

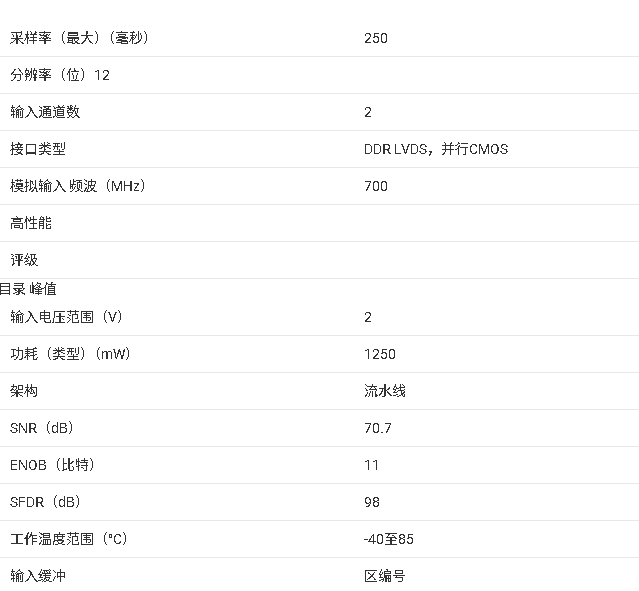

ADS62Px9/x8 具有增益选项,可用于在较低全尺度输入范围内提升 SFDR 性能。它包含一个直流偏移校正环路,可用于取消ADC偏移。同时提供DDR LVDS(双倍数据速率)和并行CMOS数字输出接口。

2025-11-21 15:57:13 636

636

的唯一身份标识符,其地址为 0x0001 2660 - 0x0001 2669,共 80bit。UID在芯片生产时写入, 用户无法修改。UID 寄存器支持以单字节 / 半字 / 全字等方式读取,然后

2025-11-19 08:03:41

的唯一身份标识符,其地址为 0x0001 2660 - 0x0001 2669,共 80bit。UID在芯片生产时写入, 用户无法修改。UID 寄存器支持以单字节 / 半字 / 全字等方式读取,然后

2025-11-18 06:35:51

。这些MCIO插座支持PCIe5(32Gbps)和SAS4(24Gbps)。MCIO 85Ω X8 X16直式插座提供用于定制布线的直式、直角和侧向出口电缆选项,完整的产品组合支持混合型电缆组件。

2025-11-06 16:06:41 526

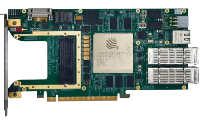

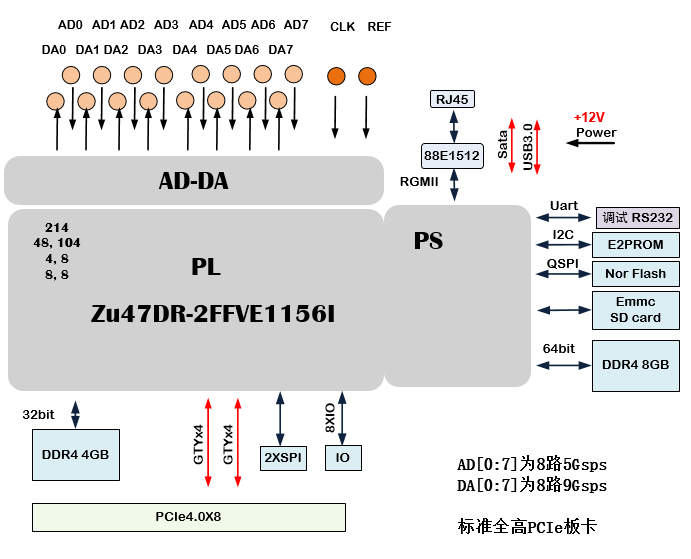

526 产品概述PCIE725G 是一款基于 PCIe x16 总线架构的高性能 FMC 接口信号处理平台,该平台支持采用 16nm 工艺 JFM9VU9P FPGA作为主处理器。该

2025-11-05 17:35:46

PCIE725G 是一款基于 PCIe x16 总线架构的高性能 FMC 接口信号处理平台,该平台支持采用 16nm 工艺 JFM9VU9P FPGA作为主处理器。该板卡支持 1 个 FMC+

2025-11-05 17:30:15 685

685

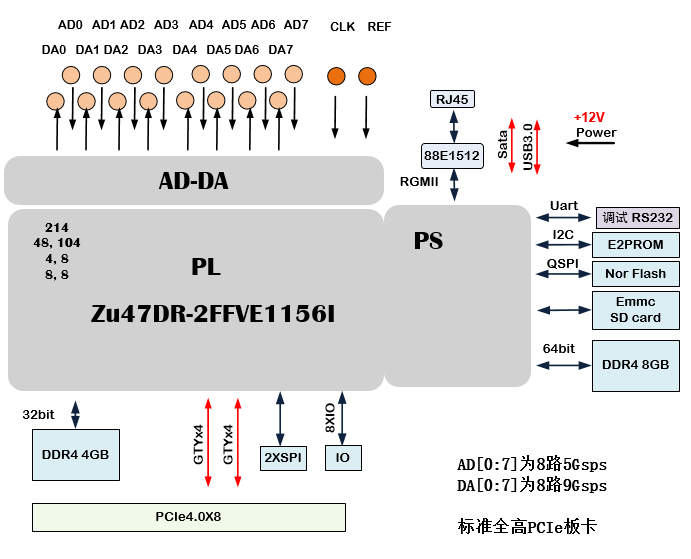

识别。该板卡的PS端支持1组72位DDR4 SDRAM,PL端支持1组32位DDR4 SDRAM,支持1片32GB EMMC存储单元,支持2片QSPI FLASH

2025-11-03 16:35:26

和优化的内存设计,长鑫存储 LPDDR5X在容量、速率、功耗上都有显著提升,目前提供12Gb和16Gb两种单颗粒容量,最高速率达到10667Mbps,达到国际主流水平,较上一代LPDDR5提升了66

2025-10-30 09:12:55 5297

5297

设计。

寄存器的读操作:

寄存器的写操作:

值得注意的是,相邻寄存器的地址这里分配的间隔为4,因为寄存器中数据的存取是以字节(Byte)为单位,1Byte = 8bit; 而这里因为采用32bit

2025-10-29 07:49:06

功耗PSRAM KGD、LPDDR4(x)颗粒及面向PC/Server领域的DDR5/DDR4模组产品等多款前沿存储产品与创新方案亮相,全面展示公司在IoT、网络通信、消费电子、汽车电子及工业控制等关键领域的创新技术和市场竞争力。

2025-10-27 17:47:31 1433

1433 前言:2025年,存储市场持续“高烧”——-国际大厂停产DDR3/4,减产LPDDR4/4X,涨价50%只是起步-国产料号月更、周更,同一料号不同Die,颗粒参数“开盲盒”-更大的坑是:对于嵌入式

2025-10-24 11:59:51 919

919

电子发烧友网综合报道,深科技主要从事高端存储芯片的封装与测试,产品包括 DRAM 运存(DDR4/DDR5)、LPDDR 低功耗运存(LPDDR4/LPDDR5)、NAND FLASH 闪存(SSD

2025-10-24 09:13:35 6360

6360 蜂鸟DDR200T中DDR3的ip配置案列,提供DDR3引脚配置。具体参数可更具项目实际更改。

这里选用的axi接口

在赛灵思的IP配置中没有MT41K28M6JT-125K内存的信息,因此选用

2025-10-21 11:19:08

2025年10月10日至12日,以“碳硅共生 合创AI+时代”为主题的第13届中国移动全球合作伙伴大会在广州保利世贸博览馆盛大举办。紫光国芯携DDR5 RDIMM模组、LPDDR4(x)/DDR4

2025-10-14 17:39:52 986

986 涉及多款 8GB、16GB DDR4 SODIMM 及 UDIMM 模组,标志着 DDR4 内存时代进入收尾阶段。

2025-10-14 17:11:37 1035

1035 NT5CB256M8GN-cg,回收H5TQ4G83AFRPBC,回收NT5CB256M16BP-di,回收K4B2G1646E-BCH9,

回收MT48LC16M16A2P75D,回收HY5PS1G831C。电子回收,回收电子元件。回收DDR,回收DDR2,回收DDR3(新旧/拆机/带板均可)

2025-10-09 14:15:34

硬件功能

USB-FS Type-C 接口,通过2.0mm跳线组合选择Host或Device功能,支持RA8x1 MCU的USB-Boot功能。

2路CAN-FD 收发器,通过2.54mm跳线座连接

2025-10-02 17:25:10

DDR4 内存,涵盖 x4、x8、x16 三种通道规格,且在 DIMM 内存类型上兼容 UDIMM(无缓冲双列直插内存模块)、RDIMM(带寄存器双列直插内存模块)与 LRDIMM(低负载双列直插内存

2025-09-22 02:36:00 2271

2271 贞光科技作为紫光国芯的重要合作伙伴,正在将国产首款通过AEC-Q100认证的车规级LPDDR4x存储芯片推向市场,为智能网联新能源汽车提供核心存储解决方案。在2025年9月5日至8日举办的重庆世界

2025-09-12 16:32:36 2639

2639

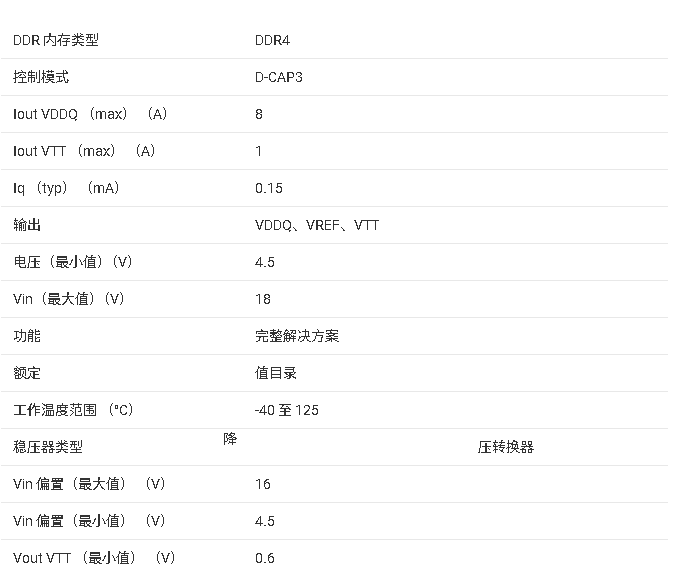

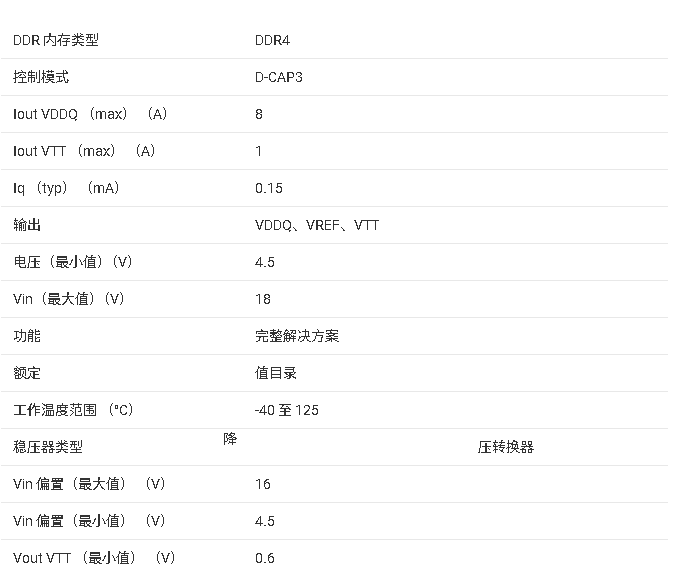

TPS65295器件以最低的总成本和最小的空间为 DDR4 内存系统提供完整的电源解决方案。它符合 DDR4 上电和断电序列要求的 JEDEC 标准。该TPS65295集成了两个同步降压转换器

2025-09-09 14:16:04 1732

1732

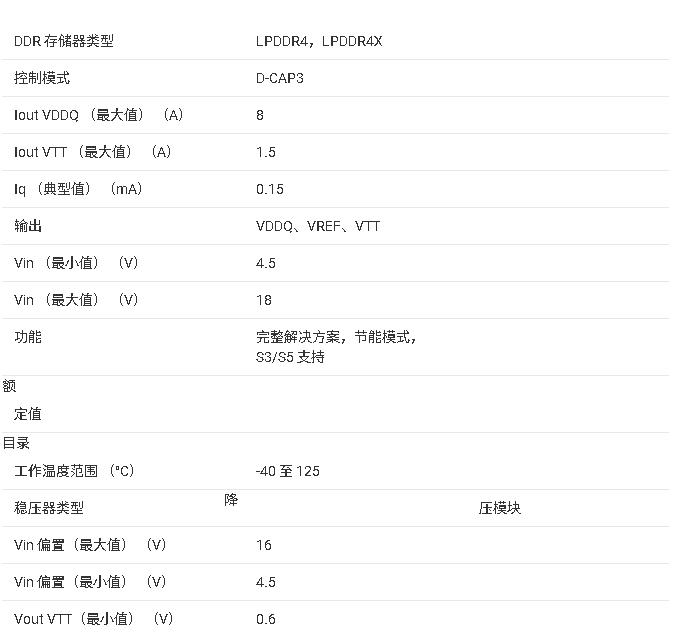

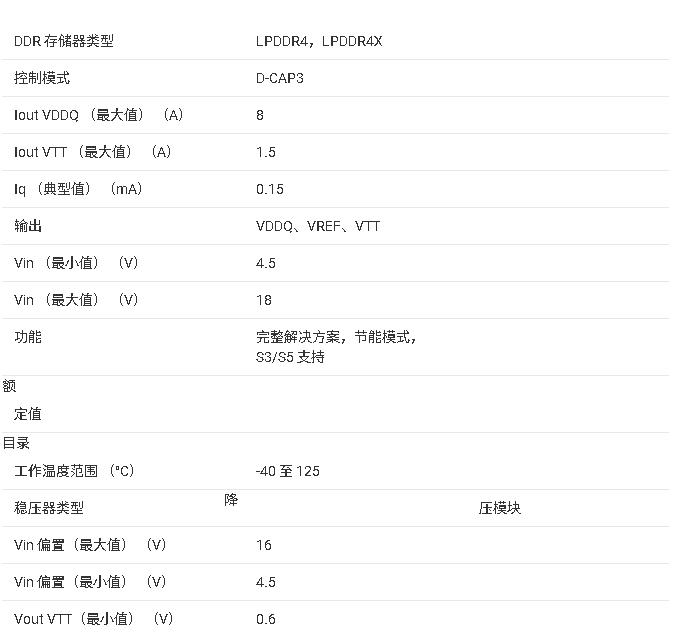

TPS65296器件以最低的总成本和最小的空间为 LPDDR4/LPDDR4X 存储器系统提供完整的电源解决方案。它符合 LPDDR4/LPDDR4X 上电和断电序列要求的 JEDEC 标准。该TPS65296集成了两个同步降压转换器(VDD1和VDD2)和一个1.5A LDO(VDDQ)。

2025-09-09 14:11:06 1155

1155

在国产存储芯片加速替代的关键阶段,北京贞光科技有限公司,作为紫光国芯的专业授权代理商,正将SDR到DDR4的全系列产品推向工业控制、电力系统和安防监控等高可靠性市场。凭借稳定的供货能力、深入

2025-09-03 16:22:46 1511

1511

Cortex-A53

2GB DDR4(SOC支持最高可达4GB)

8GB eMMC flash

256MB的SPI-NAND Flash

32MB的SPI-NOR Flash

Micro SD卡插槽

1x

2025-08-26 17:26:08

凭借与紫光国芯的紧密合作,贞光科技能够为客户提供DDR3、LPDDR4及LPDDR4X全系列车规级存储产品。在产品覆盖、技术支持和供应保障等方面的综合优势,使贞光科技成为车载电子领域可靠且高效

2025-08-26 16:12:15 1430

1430

根用于接收数据。常见的通道配置有:x1、x4、x8和x16,数字表示并行通道的数量,以此来描述接口的物理大小和数据传输带宽。例如,x16代表有16条通道,可提供比x4更高的带宽。PCIe设备通过专用

2025-08-21 16:51:24

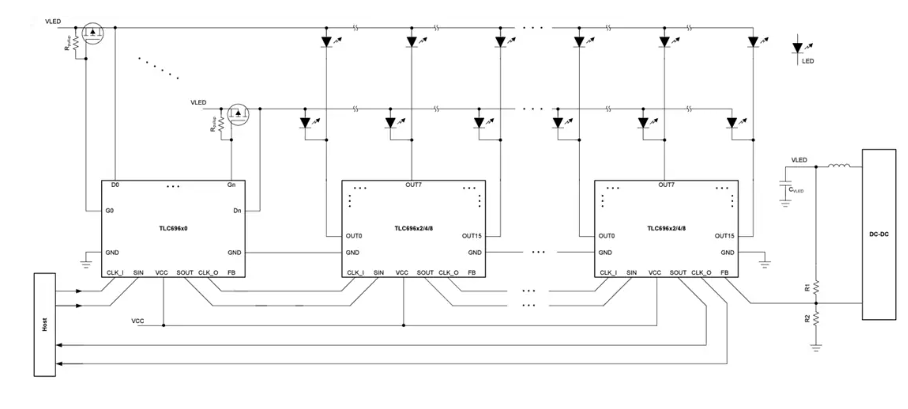

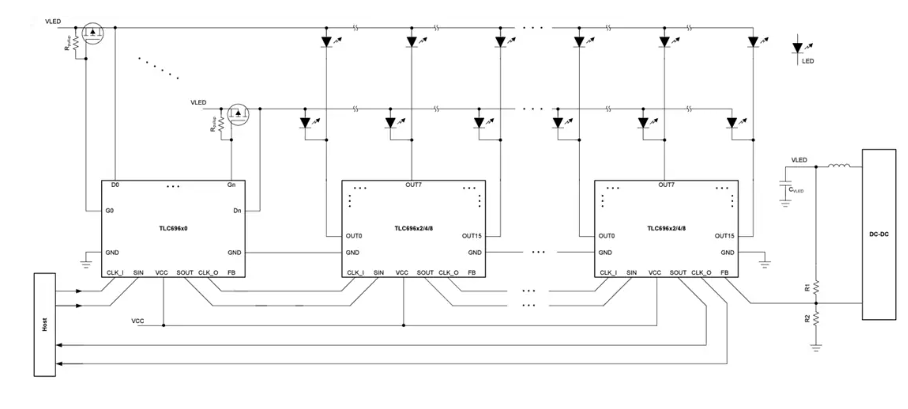

Texas Instruments TLC696x2/4/8TLC696x2/4/8-Q1背光驱动器是与TLC696x0/TLC696x0-Q1(扫描MOSFET控制器,可实现2/4/8时分多路复用

2025-08-21 14:54:59 878

878

电子发烧友网为你提供()0.25 - 2.15 GHz 4x2 开关矩阵,带音调/电压解码器相关产品参数、数据手册,更有0.25 - 2.15 GHz 4x2 开关矩阵,带音调/电压解码器的引脚图

2025-08-07 18:35:49

显示设备。特点:#CMOS工艺#低功耗#显示模式:16 段 x8 位#键扫描矩阵:8x4 按键矩阵#8个层次显示亮度调节#4线串行接口#内置 RC 振荡#内置上电复位应用领域:#LED显示面板#电动自行车显示面板#智能电表等数码管#家电设备

2025-08-06 16:30:50

8GB LPDDR4 RAM l 16 GB,默认 eMC 启动 ROM l I2S/PCM Ports x3 l HDMI Audio0ut x2 l 千兆以太网GMAC x2 l USB 3.0x

2025-07-29 09:40:19 274

274

三星 K4F6E3S4HM-MGCJ LPDDR4

2025-07-21 14:47:09 0

0 对于嵌入式系统工程师而言,选择合适的 DRAM 至关重要,需综合考虑带宽、时延与功耗限制。在近期发布的白皮书中,我们详细比较了主要的内存类型(包括 DDR4、DDR5、LPDDR4 和 LPDDR5),并针对视频处理和 AI 推理等高吞吐量应用提供了实用的选择建议。

2025-07-10 11:33:04 2158

2158 方式比较灵活,采用软核实现 DDR memory 的控制,有如下特点:

支持 DDR3

支持 x8、x16 Memory Device

最大位宽支持 32 bit

支持精简的 AXI4 总线协议

一个

2025-07-10 10:46:48

面对近来全球大厂陆续停产LPDDR4/4X以及DDR4内存颗粒所带来的巨大供应短缺,芯动科技凭借行业首屈一指的内存接口开发能力,服务客户痛点,率先在全球多个主流28nm和22nm工艺节点上,系统布局

2025-07-08 14:41:10 1160

1160 数据。

时钟关系 :

pclk为并行数据的同步时钟,fclk为高频串行时钟(通常为pclk的倍数,如 2x、4x 等,用于实现高速串行输出)。

若fclk是pclk的 8 倍,则可能实现 8b/10b 编码

2025-07-02 10:26:48

Gb(2GX8)内存在6月2日的报价为5.171美元,当时比DDR5低约8%。然而,最新报价显示DDR4已上涨至8.633美元,不到一个月时间内涨幅高达67%,且已经超过DDR5的价格的44%。最新市场数据

2025-06-27 00:27:00 4540

4540 ,其值为1、4、8、16、24、或32

u32 biCompression; // 说明图象数据压缩的类型。其值可以是下述值之一:

// BI_RGB:没有压缩;

// BI_RLE8:每个象素8比特

2025-06-14 01:51:38

LPDD3 或 LPDDR4,最大支持容量为 2GB。

K230D 有 1 路 USB 2.0 OTG,K230 有两路 USB 2.0 OTG

K230D 最多 3 路 ADC, K230 最多有 6

2025-06-11 06:46:07

基于XCVU9P的4路QSFP28光纤PCIeX16收发卡。该板卡要求符合PCIe 3.0标准,包含一片XCVU9P-2FLGA2014I、4组64-bit/8GB DDR4;4路QSFP28 4X

2025-05-29 11:02:32 648

648

初三星公司已经与主要客户协商新定价,DDR4的价格提高约20%,DDR5的价格上涨5%。 此外,SK海力士、美光此前也传出涨价的消息。据供应链人士透露,海力士DRAM(消费级)颗粒(Memory Chip/Die)价格已上涨约12%。 长江存储旗下零售品牌致态此前也透露,或从2025年4月起上调渠道提货价

2025-05-13 15:20:11 1205

1205 最新消息,三星电子本月初与主要客户就提高DRAM芯片售价达成一致。DDR4 DRAM价格平均上涨两位数百分比;DDR5价格上涨个位数百分比。据称 DDR4 上调 20%,DDR5 上调约 5

2025-05-13 01:09:00 6843

6843 最近需要找个国产LPDDR4的停产替换,希望有了解的朋友可以分享一下!感激不尽

2025-05-12 12:47:34

TPS51116为 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、DDR3L、LPDDR3 和 DDR4 内存系统提供完整的电源。它将同步降压控制器与 3A 灌电流/拉

2025-04-29 16:38:02 1031

1031

xGateway-16X 为高性能网关产品,可以扫描周围的蓝牙信号,通过网络上传 服务器。网络传输方式可以选择网口/wifi/4G中的一种或多种,可根据用户需求 定制,适合室内或室外使用。应用于需要将信标/传感器/标签快速接入IOT云端 的场景。

2025-04-27 17:57:33 0

0 Sensirion再次成为环境传感器解决方案创新先锋,推出占地仅需1平方厘米的SCD4x创新微型CO₂传感器。此次颠覆性创新以光声传感器技术为原理,尺寸降至最小的同时保证性能最优化,为更多集成和应用开辟新的空间。SCD4x具有无与伦比的高性价比,尤其适合批量生产和成本敏感应用。

2025-04-25 15:09:09 1024

1024

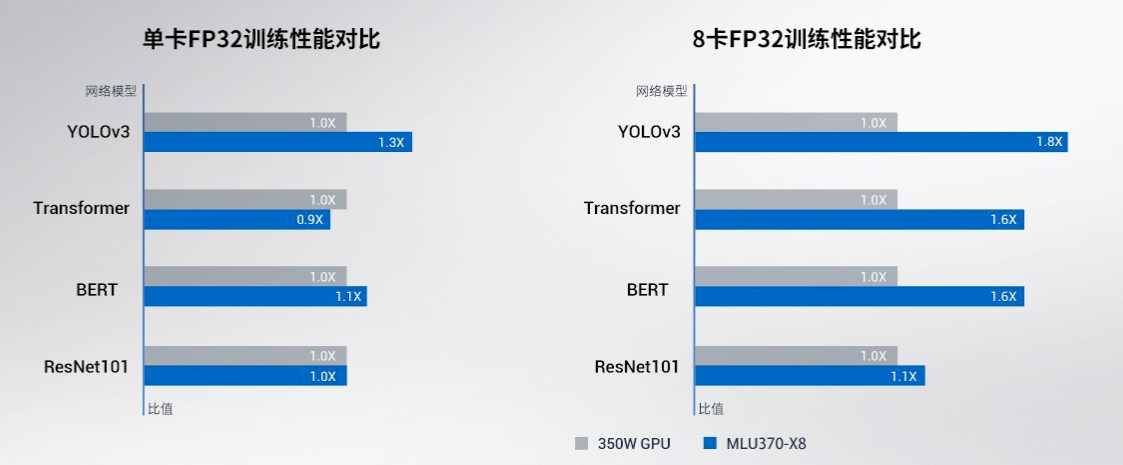

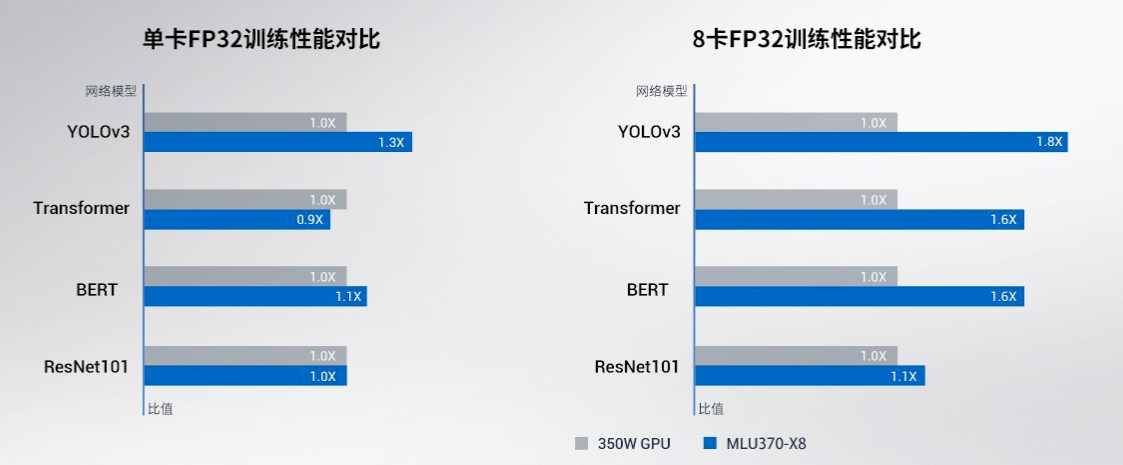

MLU370-X8智能加速卡是全面升级的数据中心训推一体AI加速卡,基于寒武纪全新一代思元370芯片,接口为PCIe 4.0 X16,是全高全长双宽(FHFL-Dual-Slot)的标准PCIe加速卡,适用于业内最新的CPU平台,可轻松搭载于最先进的人工智能服务器,快速实现 AI算力的部署。

2025-04-24 17:57:54 4517

4517

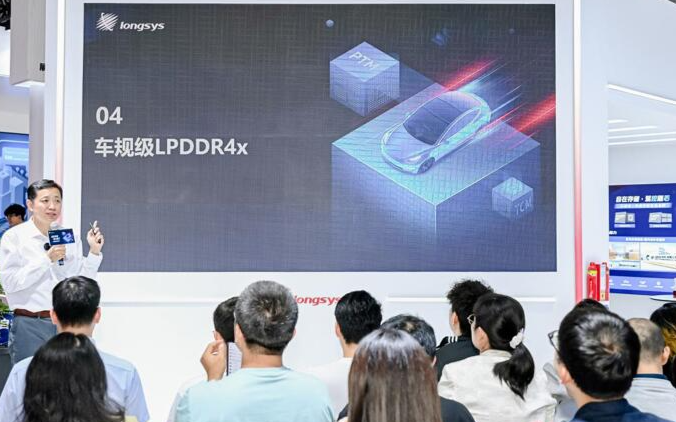

4月23日,在上海车展上,江波龙召开了新品发布会,亮相了多款创新的车规存储产品,包括车规级eMMC全芯定制版和车规级UFS,以及车规级LPDDR4x和车规级SPI NAND Flash。这些产品均符合AEC-Q100可靠性标准,能够满足智能辅助驾驶、汽车AI+等对存储性能的严苛要求。

2025-04-24 07:06:05 2631

2631

/4GB

LPDDR4

存储器

8GB eMMC/16GB eMMC/32GB eMMC

其他存储

E2PROM 32KBit

接口类型

LGA 381PIN

工作温度

工业级:-40℃ ~ +85

2025-04-23 11:35:35

电子发烧友网站提供《COMSOL Multiphysics V4.x操作手册丛书后处理用户指南.pdf》资料免费下载

2025-04-22 15:36:55 1

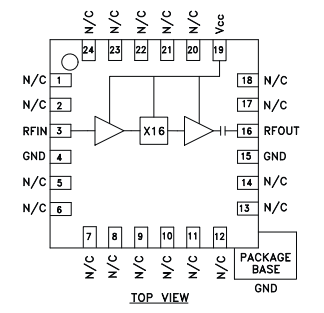

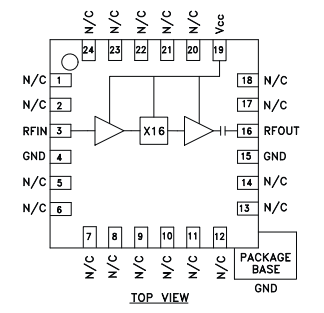

1 HMC445LP4(E)是一款有源微型x16倍频器,使用InGaP GaAs HBT技术,采用4x4 mm无引脚表面贴装封装。 功率输出为+7 dBm(典型值),电源电压为5V,在不同的输入功率

2025-04-18 09:22:16 722

722

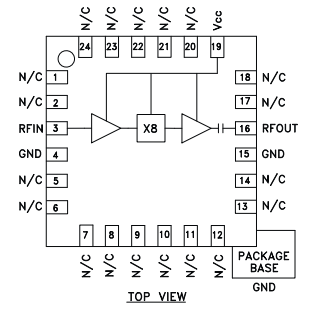

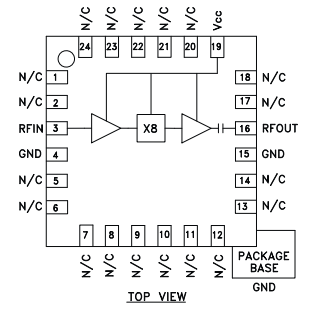

HMC444LP4(E)是一款有源微型x8倍频器,使用InGaP GaAs HBT技术,采用4x4 mm无引脚表面贴装封装。 功率输出为+6 dBm(典型值),电源电压为5V,在不同的输入功率、温度和电源电压下变化很小。

2025-04-17 17:03:10 999

999

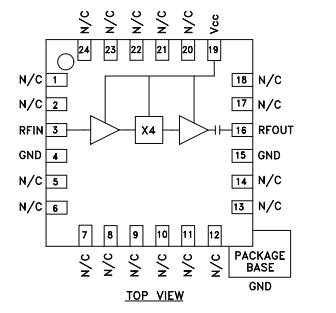

HMC370LP4(E)是一款利用InGaP GaAs HBT技术制造而成的有源微型x4倍频器,采用4x4 mm无铅表面贴装封装。 在5V电源电压下,功率输出为0 dBm(典型值)且相对输入功率

2025-04-17 11:30:11 775

775

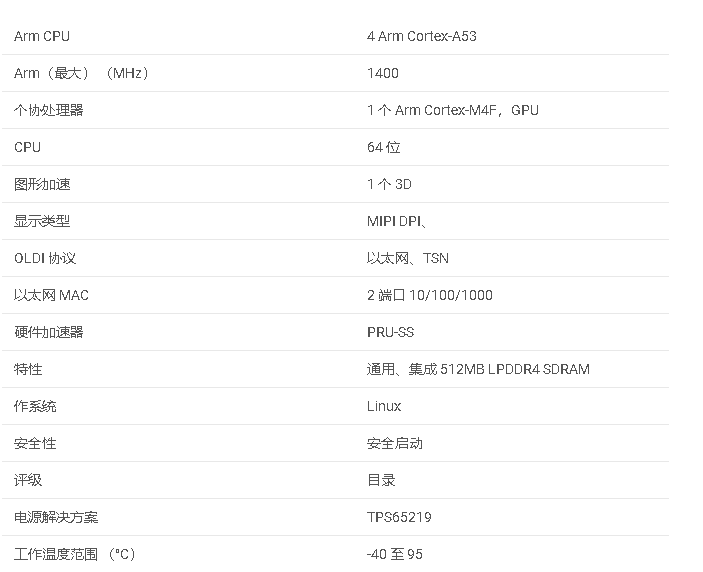

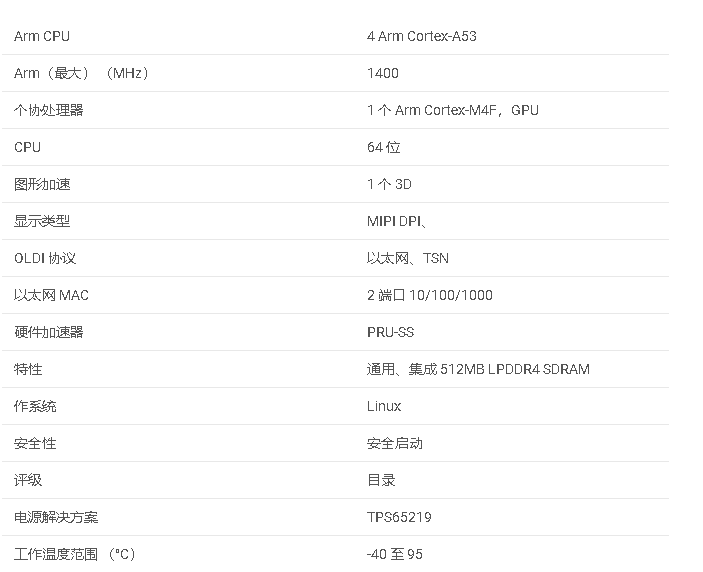

AM625SIP 是 ALW 封装的 AM6254 器件的系统级封装 (SIP) 衍生产品,增加了集成的 LPDDR4 SDRAM。本文档仅定义了 AM62x Sitara 处理器数据表 (修订版

2025-04-15 09:22:07 1300

1300

.PCIe 2.0 x8配置下,支持8路FHD(1920x1080p)@60Hz的采集与显示5.PCIe 2.0 x4配置下,支持8路FHD(1920x1080p)@30Hz的采集与显示5 用户接口1.8路

2025-04-14 15:17:46

4月10日晚间,中国手机大厂OPPO发布了Find X8系列,包括Find X8s、FindX8s+和 Find X8 Ultra。其中Find X8 Ultra最为引人注目。

2025-04-11 18:02:15 3395

3395

电子发烧友网为你提供()Sky5® LB/LMB/MB/HB 和 4x4 MIMO 分集接收模块相关产品参数、数据手册,更有Sky5® LB/LMB/MB/HB 和 4x4 MIMO 分集接收模块

2025-04-11 15:21:46

近日,全新OPPO Find X8系列发布,带来三款新机:夜景人像神器Find X8 Ultra,小得极致强得离谱的Find X8s,全民爆款全面焕新的Find X8s+。

2025-04-11 14:42:19 2034

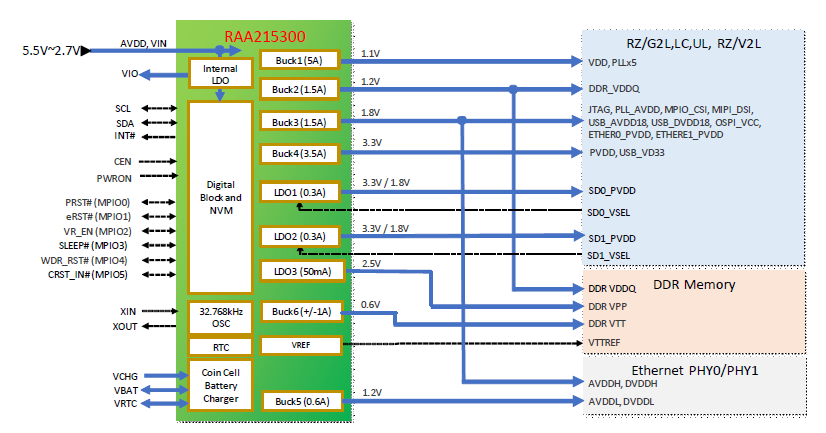

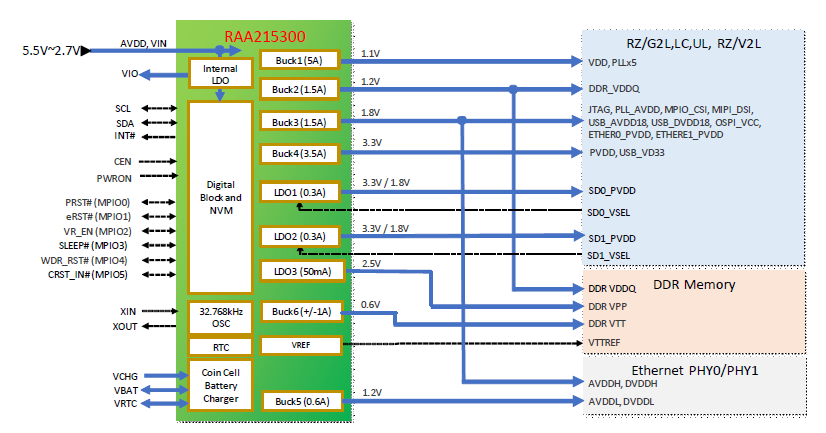

2034 RAA215300 是一款高性能、低成本的 9 通道 PMIC,专为 32 位和 64 位 MCU 和 MPU 应用而设计。 该 PMIC 支持DDR3、DDR3L、DDR4 和 LPDDR4 内存

2025-04-09 15:31:25 657

657

的DAC; ● 支持外部时钟输入1路, 外触发,外同步各1路; ● PL 1组64 bit 2400M DDR4,支持PL部分高速存储和处理。 单组4GB字节容量,PL部分8GB字节容量。 ● 支

2025-04-08 10:34:02 1024

1024

1210

注意:DDR PMU 固件 vision-0x1001 (vA-2019.04)

注意:DDR4 UDIMM,带 2 位 64 位总线 (x8)

注意:32 GB DDR4,64 位,CL=22,ECC

2025-04-04 08:17:54

产品介绍ExpressSlotEliteMB842M5P-B将PCIex8/x16扩展插槽转换为无螺丝安装M.2NVMe硬盘托架,让您无需打开机箱即可更换M.2NVMeSSD。注意:您的主板或转接卡

2025-03-27 18:02:26 1383

1383

。

SpacemiT K1主要用于单板计算机、网络存储、云计算机、智能机器人、工业控制、边缘计算机等。

主要特点

进迭时空8核RISC-V芯片,CPU集成2.0 TOPs AI算力

8GB LPDDR4内存

2025-03-25 14:40:26

近日,2025中国集成电路创新联盟大会暨协同创新交流会在北京举办。会议同期揭晓了第八届“IC创新奖”评选结果并举行颁奖仪式,紫光国芯自主研发的车规级LPDDR4(x)产品,凭借其在核心技术创新及关键场景领域应用等显著成果,荣获第八届“IC创新奖-成果产业化奖”。

2025-03-25 09:58:55 1422

1422 3, DDR3L, DDR4和LPDDR3, LPDDR4协议,数据传输速率最高可达2667Mbps,并支持X16/X32/X64等多种数据位宽应用。

2025-03-21 16:20:03 984

984 产品介绍ICYDOCKCP149是一款可拆卸的2盘位M.2NVMe硬盘转PCIe5.0x16插槽全金属硬盘抽取盒,专为使用x8/x8或x8/x4/x4PCIe拆分设置的英特尔主板而设计。与需要x4

2025-03-20 17:24:00 968

968

5的6400 Mbps提升约33%,可处理8K视频流、实时AI计算等密集型任务。三星近期推出的LPDDR5X-Ultra-Pro甚至将速率提升至12700 MT/s(

2025-03-17 10:16:08 8919

8919 我正在使用 i.MX 8M Plus 评估套件。测试 2 通道 LPDDR4 设备很好。但是,配置 1 个通道 LPDDR4 很困难,因为根据原理图,i.MX8MP 侧的通道 A 连接到 LPDDR4 侧的通道 B。如何在此交换通道分配中配置一个通道 LPDDR4?

2025-03-17 07:00:59

)或直接指定端口号5901:root@myd-ld25x:~# cat .vnc/myd-ld25x:1.log

Xvnc TigerVNC 1.12.0 - built 2023-01-06 16

2025-03-07 15:25:53

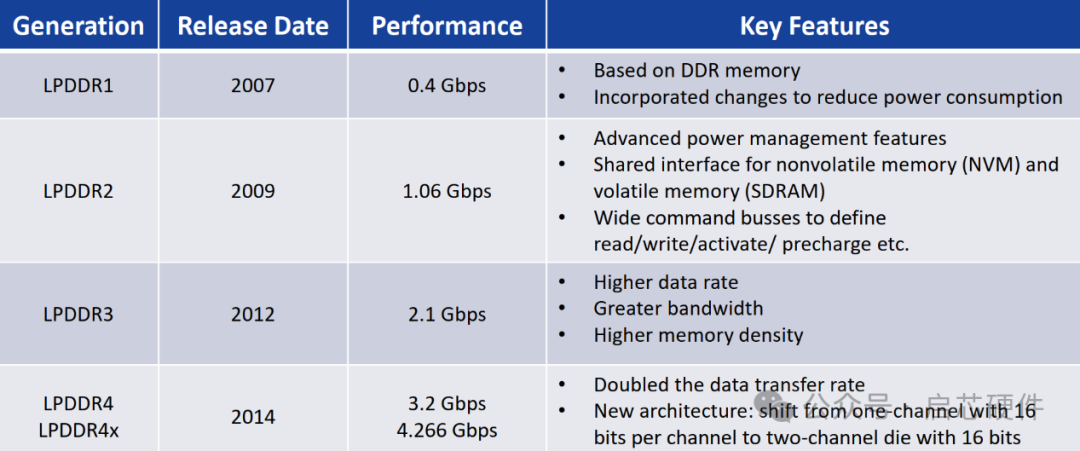

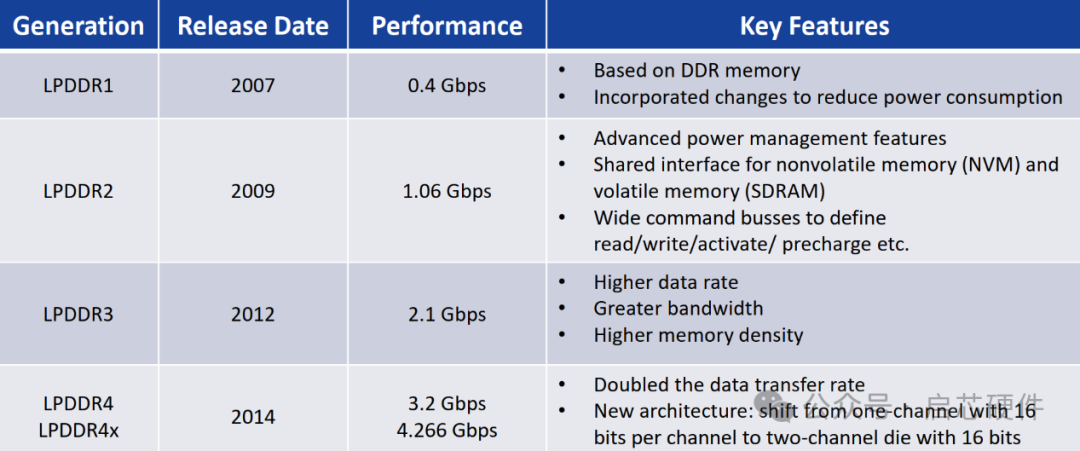

/ 机器学习应用的 HBM。 ・低功耗双倍数据速率(LPDDR)作为一种专门为移动设备(如智能手机和平板电脑)设计的内存出现。 ・LPDDR 的发展主要是由移动设备对更高性能和更低功耗的需求所驱动。 ・每一代新的 LPDDR 都提供了移动用户体验从社交媒体和游戏到 4K 乃至现在的

2025-03-04 14:44:51 2285

2285

本文详细介绍了 SK hynix 公司生产的 LPDDR4 16Gb(x16,2 Channel,1 CS)内存芯片 H9HCNNNBKUMLXR 的技术规格书。该文档提供了芯片的详细参数、功能描述

2025-03-03 14:07:05

DDR3、DDR3L、

LPDDR3、DDR4、LPDDR4、LPDDR4X 等多种内存型号。

系统框图

RK3566 EVB2 系统采用 RK3566 为系统核心芯片,采用 PMIC

2025-02-26 12:17:22

电子发烧友网综合报道,日前,日媒报道由于DRAM内存芯片价格持续下滑,全球三大原厂三星、SK海力士和美光计划在2025年停产DDR4内存芯片。 数据显示,2025年1月,DDR4 8Gb颗粒

2025-02-21 00:10:00 2807

2807

CPU RAMfour channels, each channel 16bits data widths ;

up to 32G Byte,

LPDDR4/4X

2025-02-20 21:56:40

特点4Gb双数据速率3(DDR3(L))DRAM是一种高速CMOS SDRAM,包含4294967296位。它内部配置为八进制存储体DRAM。4Gb芯片由64Mbit x 8 I/O x 8存储体

2025-02-20 11:44:07

据报道,业内人士透露,全球三大DRAM内存制造商——三星电子、SK海力士和美光,有望在2025年内正式停产已有多年历史的DDR3和DDR4两代内存。 随着技术的不断进步和消费级平台的更新换代

2025-02-19 11:11:51 3465

3465 DDR3/DDR3L/LPDDR3/DDR4/LPDDR4/LPDDR4X,最大支持 4GB (32Gb)内存

支持 SD3.0/eMMC5.1 接口

视频引擎(Video Engine):

H.265

2025-02-13 10:20:55

LPDDR4/4X&LPDDR5 2x32Bit支持 LPDDR4/4X&LPDDR5 2x32BitRK3588S和RK3588对比,主要减少的功能

2025-02-11 11:53:28

如需了解价格货期等具体信息,欢迎在首页找到联系方式链接我。不要留言,留言会被吞,收不到留言。 8GB DDR4 ECC UDIMM 产品概述 8GB DDR4 ECC UDIMM

2025-02-10 20:07:47

如需了解价格货期等具体信息,欢迎在首页找到联系方式链接我。不要留言,留言会被吞,收不到留言。 16GB DDR4 ECC UDIMM 产品概述 16GB DDR4 ECC

2025-02-10 20:05:15

M471A2G43AB2-CWE 是一款高性能的 DDR4 SO-DIMM 内存模块,具有 16GB 的容量,专为满足现代移动计算需求而设计。这款内存条采用了 Samsung 的先进技术,适用于各种

2025-02-10 07:49:49

M471A1G44CB0-CWE 是一款高性能的 DDR4 SO-DIMM 内存模块,具有 8GB 的容量,专为满足现代移动计算需求而设计。这款内存条采用了 Samsung 的先进技术,适用于各类

2025-02-10 07:48:41

NN 等深度学习框架。

存储能力

内存

支持 32 - bit LPDDR4/LPDDR4x/LPDDR5。

支持 eMMC 5.1,SDIO 3.0 和 SFC。

支持 UFS v2.0

2025-02-05 11:39:03

147.7x71.5x7.7毫米,接近现有iPhone 15和iPhone 16的尺寸。 除了尺寸,iPhone SE 4的其他配置也备受期待。预计它将于2025年3月或4月发布,可能采用6.1英寸OLED显示屏、Face ID、USB - C接口、单颗48

2025-01-24 14:48:33 1634

1634 电子发烧友网站提供《EE-39:将5V闪存与ADSP-218x接口(字节编程算法).pdf》资料免费下载

2025-01-15 16:11:51 0

0 直接进行仿真了。这种方法非常的简单,但是,DDR4 这一侧的模型包含在内部,接口信号隐藏了,所以用户无法直接观察到 DDR4 管脚上的波形。

2025-01-10 13:33:34 1481

1481

电子发烧友App

电子发烧友App

评论