2022-6-1 中国,上海 上海合见工业软件集团有限公司(简称“合见工软”)近日推出多款EDA产品和解决方案,以更好地解决芯片开发中的功能验证、调试和大规模测试管理,以及先进封装系统级设计协同

2022-06-01 17:38:47 3621

3621

Cadence宣布业内首个DDR4 Design IP解决方案在28纳米级芯片上得到验证

2012-09-10 09:53:24 1949

1949 楷登电子(NASDAQ:CDNS)今日宣布,发布增强型 Cadence® Voltus™IC 电源完整性解决方案,其面向先进工艺节点的电网签核,其大规模并行(XP)算法选项采用了分布式处理技术。

2018-07-26 15:59:22 7890

7890 2022年6月28日,国微思尔芯面向全球客户正式发布芯神瞳自动原型编译软件Player Pro-7(PPro-7)。新版本针对大规模芯片设计提供了有效的解决方案,拥有更高的编译效率和更好的分割性能

2022-06-28 10:21:59 1269

1269

限制,以及一些现有通信系统中存在的挑战,诸如网络的可靠性、覆盖率、能效性、和延迟性等。大规模MIMO作为5G技术的一种实现方案,通过在基站收发信机(BTS)上使用大量的天线(超过64根)实现了更大的无线

2014-12-24 14:13:12

其测试方案。最后分析了国内毫米波终端可能的商用计划。【关键词】毫米波终端,大规模天线技术,空中下载技术

2019-07-18 08:04:55

的数据库架构,使用模型和库为Cadence OrCAD和Allegro产品线提供完全可升级的PCB解决方案,加速你的设计速度并扩大设计规模,从而提高了设计效率,缩短了设计周期,以及更快地实现

2018-08-30 10:49:16

平台是更广泛的 Cadence 3D-IC 解决方案组合的一部分,该组合超越了数字,包括系统和验证以及IP 功能。更广泛的解决方案通过由 Palladium® Z2 和 Protium™ X2

2021-10-14 11:19:57

Cadence设计系统有限公司宣布推出业界第一套完整的能够推动SiPIC设计主流化的EDA产品。Cadence解决方案针对目前SiP设计中依赖‘专家工程’的方式存在的固有局限性,提供了一套自动化

2008-06-27 10:24:12

IEEE Transactions on Information Forensics and Security上的一篇论文探讨了这种类型的攻击。他们发现,在某些情况下,当使用大规模多入多出技术

2019-06-18 07:54:32

轨迹产生的容量斜坡仍然比需求线平坦。面对此挑战,3GPP 标准实体近来提出了数据容量“到2020 年增长1000 倍”的目标,以满足演进性或革命性创意的需要。这种概念要求基站部署极大规模的天线阵

2019-07-17 07:54:10

大规模区域监控与通信系统的SOPC芯片组,看完你就懂了

2021-05-26 06:46:11

作为提升5G系统频谱效率最直观的物理层技术之一,大规模天线技术自问世以来,受到了来自学术界、工业界的广泛关注。样机测试为了克服信道信息获取困难、解决导频污染、以及计算复杂度大幅提升等问题,测试验证

2019-06-13 07:49:29

解读5G通信的杀手锏大规模天线阵列

2021-01-06 07:11:35

是Mailbox的工作方式。 TDA4VM的IPC方案,基于Mailbox的实现的方式的不同,常用的核间通信方式有两种。 基于RPMSG的核间通信解决方案,适合小块数据消息传递。基于Share Memory

2022-11-03 07:26:19

随着现代集成电路技术的发展,尤其是IP的大量使用,芯片的规模越来越大,系统功能越来越复杂,普通的EDA和FPGA仿真在速度和性能上已经无法胜任芯片仿真验证的要求,功能验证已经成为大规模芯片设计的一个

2010-05-28 13:41:35

挑战海啸模拟将物理过程模拟与大量深海数据相结合。这些计算通常在大规模并行超级计算机上完成,但具有硬件利用率低和性能差的缺陷。解决方案通过硬件浮点 FPGA 加速模拟内循环可实现高达 383

2018-07-27 15:04:13

些功能原本是用简单C语言在处理器或DSP中实现的。人们希望能够找到一种方法,在更高的层次下设计更复杂,更高速的系统,并希望将软件设计和硬件设计统一到一个平台下。解决方案C/C++语言是软件工程师在开发商

2015-01-13 16:34:40

期,产品形态和方案等各有不同。本文作者根据多年的研究成果,提出一种工作于Sub-6G的5G大规模天线的系统架构,并对其各系统组成部分进行介绍。

2019-07-16 08:12:54

什么是WiMAX物理层信号测试解决方案?有什么作用?

2019-08-08 08:04:19

本文提出了一种基于FPGA的适合大规模数字信号处理的并行处理结构。

2021-04-30 07:16:52

回收Agilent/Keysight86115D大规模/并行光收发信机测试模块全国长期回收Agilent/Keysight86115D收购大规模/并行光收发信机测试模块联系人:陈先生:***《微信

2020-08-21 11:06:14

ADI公司提供基于单硅芯片的电池化成控制系统综合解决方案 AD8452。凭借准确的化成工艺性能,可优化每个电池的化成时间。高效的能量回收特性能够明显节省大规模电池制造的能耗。

2021-01-21 06:27:38

如何去推进FTTH大规模建设?影响FTTH大规模建设的原因有哪些?

2021-05-27 06:58:13

描述此 TI 验证设计采用各种运算放大器,以绝缘电阻驱动 100pF 至 1uF 的电容负载。OPA192 的亮点在于其能够以小型绝缘电阻驱动大规模电容负载。主要特色电源电压:30 V (+/-15

2018-11-15 11:40:22

大规模电动汽车生产需要先进的电池化成和测试系统

2021-01-27 06:59:50

如何去设计一款合理的电子硬件解决方案,从而实现经济有效的大规模生产与部署?怎样去验证可部署目标硬件与软件算法模型之间的算法性能一致性?System Generator是什么?有什么功能?

2021-04-08 06:25:48

的运算,实现物理时间和仿真时间的同步更新。第二是大规模,即整个系统在各部分各个时间尺度上都能覆盖,而不是被简化。在此要求下,必须对系统进行划分,对每一个划分出来的小型子系统采用多核处理器进行并行计算仿真

2016-12-03 20:42:42

构建大规模MIMO的难点在哪?高功率硅开关的应用案列分析

2021-03-11 07:05:03

我要如何发布我的HarmonyOS组件或解决方案?

2022-06-02 15:55:36

请教大神如何去管理大规模数据?

2021-05-11 06:56:54

大规模MIMO的原型怎么制作?

2021-05-24 06:25:09

轮胎压力监测(TPM)系统有望获得大规模应用。

2021-05-12 06:02:56

基于基因电脑克隆软件SiClone 和可变剪接分析软件AltSplice 的并行优化工作,提出一种基于大规模序列比对软件的并行优化方案。该方案对所要进行比对分析的大规模序列库按某种策

2009-03-29 09:43:40 17

17 摘要:在使用传统的动态仿真方法对通用微处理器这样大规模的设计进行功能验证时仿真速度成为了瓶颈,而使用FPGA物理原型验证又不能提供很好的可调试性。本文主要介绍了基于

2010-06-07 11:20:54 0

0 服务范围大规模集成电路芯片检测标准●JESD22-A103/ A104/ A105/ A108/ A110●J-STD-020●JS-001/002●JESD78检测项目(1)芯片级可靠性验证试验

2024-03-14 16:28:30

能源公司采用McDATA大规模IT整合解决方案

权威的多功能存储网络解决方案供应商McDATA公司宣布,在PPL公司实施了一套基于McDATA的IT整合和数据保护解决

2009-07-06 08:51:30 674

674 Cadence推出首个TLM驱动式设计与验证解决方案

Cadence设计系统公司今天推出首个TLM驱动式协同设计与验证解决方案和方法学,使SoC设计师们可以尽享事务级建模(TLM)的好处。

2009-08-07 07:32:00 931

931 Cadence推出首个TLM驱动式设计与验证解决方案提升基于RTL流程的开发效率

Cadence设计系统公司推出首个TLM驱动式协同设计与验证解决方案和方法学,使SoC设计师们可以尽

2009-08-11 09:12:18 756

756 Cadence为PCI Express 3.0推出首款验证解决方案

Cadence设计系统公司宣布其已经开发了基于开放验证方法学(OVM)的验证IP(VIP)帮助开发者应用最新的PCI Express Base Specification

2009-11-04 16:59:59 1531

1531 海思半导体大规模采用SpringSoft的验证与定制设计解决方案

在高效能ASIC设计流程中部署Verdi自动侦错、Siloti能见度自动增强科技以及Lak

2010-03-17 16:45:20 1242

1242 全球电子设计创新领先企业Cadence设计系统公司日前宣布TSMC已选择Cadence解决方案作为其20纳米的设计架构。Cadence解决方案包括Virtuoso定制/模拟以及Encounter RTL-to-Signoff平台。

2012-10-22 16:48:03 1286

1286 电子设计创新企业Cadence设计系统公司,今天宣布使用ARM AMBA协议类型的Cadence验证IP(VIP)实现多个成功验证项目,这是业界最广泛使用的AMBA协议系列验证解决方案之一。顶尖客户,包括

2012-11-07 08:21:52 1357

1357 光刻物理分析器成功完成20纳米系统级芯片(SoC)测试芯片流片。双方工程师通过紧密合作,运用Cadence解决方案克服实施和可制造性设计(DFM)验证挑战,并最终完成设计。

2013-07-09 15:53:24 1053

1053 Workbench搭配Cadence Interconnect Validator,组成了一套完整的功能验证与性能检验解决方案。

2013-11-07 09:34:14 1477

1477 日益增长的验证复杂性正推动着包括形式分析的多种互补验证方法的需求,而 Jasper是快速增长形式分析行业的领导者,目标针对各种复杂验证的挑战,Cadence与Jasper的结合将扩大产业最强与最广泛的系统验证产品的差异性优势。

2014-04-25 18:32:48 2930

2930 完整性签核量身打造。Cadence® Sigrity 产品组合的全新功能中,Allegro® PowerTree™ 拓扑检视器及编辑器脱颖而出,助客户快速评估设计流程初期的功率输出方案。全新发布

2017-02-07 15:39:26 1614

1614 2017年3月1日,上海——楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日发布业界首款已通过产品流片的第三代并行仿真平台Xcelium™ 。基于多核并行运算技术,Xcelium

2017-03-01 15:57:05 5718

5718 此方案可简化,无电缆的设计分割,最多允许四个用户同时使用。S2C公司,业内领先的 FPGA 快速原型验证系统供应商,发布了适用于超大规模设计的基于赛灵思Virtex UltraScale(VU

2018-06-29 08:09:00 6021

6021 签密思想是将签名和加密融为一体的构想,相比传统的先签名后加密的体制,它的计算量小和运算速度快。自认证免去了公钥证书的管理,能为系统节约成本。鉴于两者的优点,提出了一个基于自认证的并行多重签密方案

2017-11-21 09:31:23 1

1 大规模问题,HOBBIES软件的千核规模电磁并行计算效率达到90%。 2)高效的核外求解技术:对于舰船、飞机编队等大型电磁目标,其电磁特性计算量很大,任务不可能在内存完成,HOBBIES核外求解技术的效率可以达到物理内存的90%以上,而其它软件的虚拟内存效率

2017-11-23 16:58:54 808

808 为解决已有基于身份的签密算法效率不高的问题,考虑低端设备计算能力弱的特点,引入服务器辅助验证思想,提出一种服务器辅助验证签密方案,通过服务器完成验证过程中的一些复杂运算,减少算法验证阶段的计算量

2018-03-20 14:25:22 0

0 Cadence Palladium Verification Computing Platform是全集成、高性能的超大规模集成电路功能仿真验证系统平台。这种高度可扩展的集成电路功能仿真验证硬件平台

2018-11-06 11:37:36 4765

4765 RS CMW100 通信制造测试装置 针对大规模生产、无线测试、5G NR的全新解决方案,是通用非信令测试套件,可用于6 GHz以下的5G NR测试。 主要特点:- 连续频率范围(最高达 6 GHz) - 多技术解决方案 - 可在最多八个射频端口上并行测试 - 高测量性能

2020-04-13 11:47:00 3041

3041 FACE-VUP:大规模FPGA原型验证平台 FACE-VUP大规模FPGA原型验证平台是FACE系列的最新产品。FACE-VUP同时搭载16nm工艺的Virtex UltraScale+系列主器件

2020-05-19 10:50:05 3371

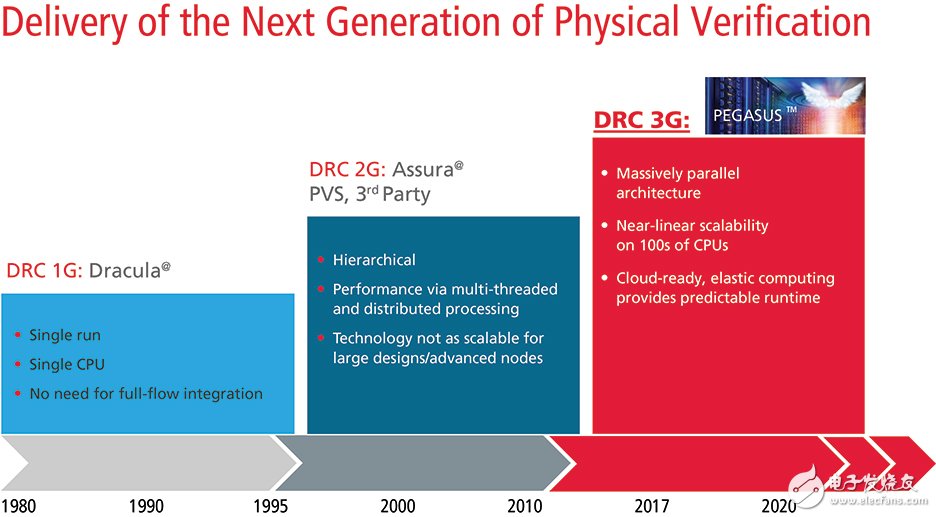

3371 新思科技(Synopsys)近日宣布推出最新版本IC Validator物理验证解决方案,该解决方案包含多项创新技术,可加快前沿应用推向市场的时间。IC Validator独特的弹性CPU调配技术

2020-11-24 14:42:52 3103

3103 双方合作包括多个签核域和跨库特征提取,以加速设计收敛 签核解决方案的创新能够解决从5纳米到3纳米的独特挑战,以确保签核准确性,并将运行速度提高20倍、内存消耗减少50% ECO迭代减少5倍、提高硬件

2021-01-11 18:21:15 2065

2065 超过 10%。 Cadence 与 GF 的合作让采用 GF 12LP 和 12LP+ 解决方案的签核工程师可以加速芯片设计和生产,为 AI、数据中心、超大规模、航空航天和工业市场开发产品。 中国上海

2021-03-30 15:42:47 2209

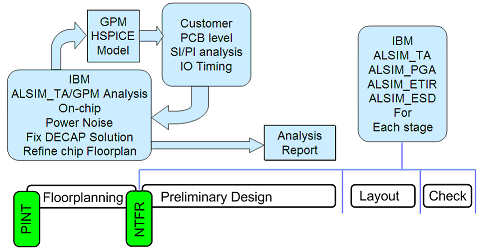

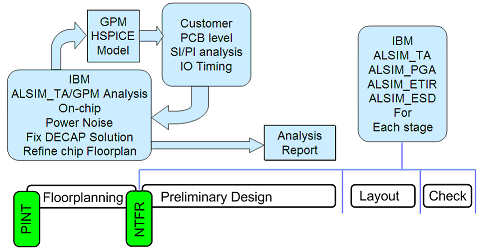

2209 针对超深亚微米工艺下超大规模通信集成电路所面临的物理设计难点,IBM提出了相应的解决方案,具体介绍如下。

2021-06-21 11:01:46 4605

4605

的演示。是德科技提供先进的设计和验证解决方案,旨在加速创新,创造一个安全互联的世界。 高速以太网生态系统中的网络设备制造商(NEM)正在努力满足超大规模数据中心对更快速度、更高流量密度的要求。为应对高速网络解决方案的功耗和性能需求,QSFP-DD 多源协议

2021-06-23 14:40:38 1916

1916 Cadence Safety Solution 包括新的 Midas Safety Platform,为模拟和数字流程提供基于 FMEDA 功能安全设计和验证的统一方案 该安全流程方案为汽车、工业

2021-10-26 14:24:34 5615

5615 Liberate Characterization 和 Tempus 解决方案已经通过 Samsung Foundry 老化模型验证,使客户能够快速、安心地完成高可靠性的设计签核 Tempus 解决方案的全新

2021-11-19 11:00:13 3839

3839 Integrity 3D-IC 是 Cadence 新一代多芯片设计解决方案,它将硅和封装的规划和实现,与系统分析和签核结合起来,以实现系统级驱动的 PPA 优化。 原生 3D 分区流程可自动智能

2021-11-19 11:02:24 4231

4231 随着SoC设计规模呈指数级增长,芯片设计团队原型验证需求也变的越来越复杂。单通过增加系统容量的方式,还是会遇到诸多困难和挑战。设计团队需要有一个成熟的面向大规模SoC设计的高密原型验证系统的软硬件通用解决方案,来解决关键困难点的突破,降低项目风险。

2021-12-08 10:54:32 2433

2433 作为新思科技光电子统一设计平台的基础,OptoCompiler可为光子芯片提供完整的端到端设计、验证和签核解决方案。OptoCompiler将成熟的专用光子技术与业界领先的仿真和物理验证工具相结合,开发者能够对复杂的光子芯片进行快速、准确的设计和验证。

2022-03-11 14:04:15 1768

1768 新思科技近日宣布与Ansys联合开发的电压时序签核解决方案已获三星采用,用以加速开发其具有理想功耗、性能和面积(PPA)的高能效比设计。

2022-04-24 15:27:02 1958

1958 该联合解决方案基于新思科技的行业金牌PrimeTime签核技术和Ansys 的RedHawk-SC电源完整性签核技术,能够防止动态电压降引起的时序失效并尽可能减小时序悲观性。

2022-04-27 14:29:22 1502

1502 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布推出 15 种新的验证 IP(VIP)解决方案,助力工程师迅速有效地验证设计,以满足最新标准协议的要求。

2022-06-06 11:18:21 4798

4798 阶段即能识别、分析并解决复杂的 IC 和芯片级系统 (SoC) 物理验证问题,进而帮助 IC 设计团队和公司加快流片速度。 在设计周期内更早地识别和解决问题,不仅有助于压缩整个验证周期,而且还能创造更多的时间和机会来提高最终的设计质量。西门子使用认证的签核

2022-08-01 18:14:57 3052

3052 近日,芯华章科技宣布对高性能仿真软件领先企业瞬曜电子进行核心技术整合,将超大规模软件仿真技术融入芯华章智V验证平台,以增强其丰富的系统级验证产品组合,巩固芯华章敏捷验证方案。同时,傅勇正式加盟芯华章

2022-09-26 10:03:15 503

503 因此,通过与 Cadence Innovus Implementation System 和 Tempus Timing Signoff Solution 共享同一个引擎,并行全芯片优化得以实现,模块所有者无需进行反复迭代,设计师也可以快速做出优化和签核决定。

2022-10-12 15:59:04 1301

1301 Wi-SUN协议在远程sub-GHz频段提供基于标准的大规模网状网络解决方案,这是现有网状网络物联网标准无法实现的。

2022-11-01 11:30:04 1509

1509 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布扩大与台积电和微软的合作,致力于加快千兆级规模数字设计的物理验证。通过此次最新合作,客户可以在带有 Cadence

2023-04-26 18:05:45 1484

1484 日前,芯华章应邀参与国际电子媒体ASPENCORE举办的《高性能计算的AI设计挑战及解决方案》线上直播论坛,与车载智能芯片平台供应商芯砺智能一道,以汽车电子为例,围绕系统级大规模芯片设计面临的挑战及验证难题,进行深入交流和讨论,吸引近500名集成电路相关从业者线上观看。

2023-05-25 15:05:52 1413

1413 NEWS2022/6/282022年6月28日,国微思尔芯面向全球客户正式发布芯神瞳自动原型编译软件PlayerPro-7(PPro-7)。新版本针对大规模芯片设计提供了有效的解决方案,拥有更高

2022-07-02 10:58:24 967

967

在 GPU 上使用大规模并行哈希图实现性能最大化

2023-07-05 16:30:35 1662

1662

平台以独特的方式将系统规划、实现和系统层级分析整合成为一个解决方案,实现无缝的原型验证 ● 共同客户可为其 AI、移动、5G、超大规模计算和物联网 3D-IC 设计进行系统原型建模,加快多芯粒

2023-10-08 15:55:01 979

979 电子设计自动化领域领先的供应商 Cadence,诚邀您参加“2023 Cadence 中国技术巡回研讨会”。会议将集聚 Cadence 的开发者与资深技术专家,与您分享数字设计与签核解决方案,并与

2023-10-23 11:55:02 907

907

电子设计自动化领域领先的供应商 Cadence,诚邀您参加“2023 Cadence 中国技术巡回研讨会”。会议将集聚 Cadence 的开发者与资深技术专家,与您分享系统验证及 IC 验证解决方案

2023-10-23 11:55:02 987

987

电子设计自动化领域领先的供应商 Cadence,诚邀您参加“2023 Cadence 中国技术巡回研讨会”。会议将集聚 Cadence 的开发者与资深技术专家,与您分享系统验证及 IC 验证解决方案

2023-10-25 10:40:02 792

792

电子设计自动化领域领先的供应商 Cadence,诚邀您参加“2023 Cadence 中国技术巡回研讨会”。会议将集聚 Cadence 的开发者与资深技术专家,与您分享数字设计与签核解决方案,并与

2023-10-30 11:35:02 885

885

分享数字设计与签核解决方案,并与技术专家们面对面直接沟通交流。Cadence 期待您的参与! 会议报名 Cadence 将在 北京 开展 “数字设计与签核研讨会 专场 ” 。 您可以 扫描下方二维码 或

2023-11-16 16:30:02 789

789

,并取得了更好的 PPA 结果 2 首次部署 Cadence 签核解决方案后,Samsung Foundry 实现了两倍的生产力提升,加速了设计收敛 中国上海,2023 年 12 月 4 日——楷登

2023-12-04 10:15:01 1087

1087 分享数字设计与签核解决方案,并与技术专家们面对面直接沟通交流。Cadence 期待您的参与! 会议报名 Cadence 将在 北京 开展 “数字设计与签核研讨会 专场 ” 。 您可以 扫描下方二维码 或

2023-12-07 09:30:02 753

753

新思科技3DIC Compiler集成了3Dblox 2.0标准,可用于异构集成和“从架构探索到签核”的完整解决方案。

2024-01-12 13:40:50 973

973

●CelsiusStudio采用大规模并行架构,与之前的解决方案相比,性能快10倍●CelsiusStudio与Cadence芯片、封装、PCB和微波设计平台无缝集

2024-02-19 13:00:09 1477

1477

Ansys携手英特尔代工,共同打造2.5D芯片先进封装技术的多物理场签核解决方案。此次合作,将借助Ansys的高精度仿真技术,为英特尔的创新型2.5D芯片提供强大支持,该芯片采用EMIB技术实现芯片间的灵活互连,摒弃了传统的硅通孔(TSV)方式。

2024-03-11 11:24:19 1491

1491 Ansys的多物理场签核解决方案已经成功获得英特尔代工(Intel Foundry)的认证,这一认证使得Ansys能够支持对采用英特尔18A工艺技术设计的先进集成电路(IC)进行签核验证。18A工艺技术集成了新型RibbonFET晶体管技术和背面供电技术,代表了半导体制造领域的一项重大突破。

2024-03-11 11:25:41 1358

1358 楷登电子(Cadence)上半年震撼发布了新一代Cadence® Palladium® Z3 Emulation和Protium™ X3 FPGA原型验证系统,标志着加速验证、软件开发和数字孪生

2024-12-30 10:37:50 1158

1158 随着 SoC 设计日益复杂,形式等效性检查面临更大挑战。为此,Cadence 推出了 Conformal AI Studio —— 一套全新的逻辑等效性检查(LEC)、自动化 ECO(Conformal ECO)和低功耗静态签核解决方案。

2025-03-21 13:50:03 1154

1154 DeepSeek-V3 / R1 等模型采用大规模细粒度混合专家模型 (MoE) 架构,大幅提升了开源模型的质量。Llama 4 和 Qwen3 等新发布的开源模型的设计原则也采用了类似的大规模细粒度 MoE 架构。但大规模 MoE 模型为推理系统带来了新的挑战,如高显存需求和专家间负载失衡等。

2025-09-06 15:21:11 1035

1035

之前文章已介绍引入大规模 EP 的初衷,本篇将继续深入介绍 TensorRT-LLM 的大规模专家并行架构设计与创新实现。

2025-09-23 14:42:53 859

859

在半导体设计中,“签核”通常被视为一个里程碑。但实际上,这涵盖了多个具有特定目标的独立验证阶段。

2025-10-21 10:15:51 682

682

电子发烧友App

电子发烧友App

评论