在半导体设计中,“签核”通常被视为一个里程碑。但实际上,这涵盖了多个具有特定目标的独立验证阶段。

功能签核和RTL签核就是其中的两个环节,二者各自侧重于正确性的不同方面,缺一不可。功能签核主要验证设计是否按预期运行,而RTL签核则侧重于寄存器传输级实现的结构是否合理,能否为后续的综合和物理实现做好准备。

目前,IP模块持续增多、多个异步时钟域并存,电源管理方案也愈加严苛,这让片上系统(SoC)的复杂性不断增加,与此同时,这些签核阶段也变得越来越专业化。验证流程必须确认设计的意图和完整性,才能迈入下一阶段。然而,功能层级与RTL层级“完成标准”的界限并不总是清晰,这个问题在覆盖范围、功耗设计意图和时序就绪性方面存在重叠时尤为突出。

值得庆幸的是,新思科技提供了一套完整的工具,为RTL和功能签核带来了结构化与智能化的双重保障。

什么是功能签核?

功能签核旨在确认设计是否准确实现了预期功能特性。该验证在RTL抽象层执行,此时设计通常仍然以Verilog或VHDL等源代码表示,尚未进行任何综合或布局转换。其目标是验证RTL是否在所有定义的应用场景、运行模式和边界条件下满足设计规格,而暂不考虑后续物理实现问题。

此阶段通常涉及仿真和形式化分析。开发者常使用基于通用验证方法(UVM)的测试平台来施加激励并检查预期响应。他们通过覆盖组和断言来定义功能覆盖率,以此衡量在仿真期间是否发生了重要事件和行为。代码覆盖率则作为补充指标,用于跟踪是否RTL的所有部分都已执行。

虽然代码覆盖率相对容易达到高值,但功能覆盖率仍更具主观性,具体取决于规格的质量和验证团队对实际场景的预测能力。即使覆盖率指标显示已达100%,开发者仍常怀疑测试是否涵盖了关键部分。这种不确定性导致在流片后仍需持续开展验证工作。

为了消除这种不确定性,我们在VSO.ai解决方案中引入AI驱动的机器学习技术,该解决方案和新思科技业界领先的VCS功能验证解决方案集成,能够识别未测试行为、生成针对性输入并简化测试用例选择。VSO.ai不仅能提高覆盖结果,还增强了用户对验证全面性和有效性的信心。

什么是RTL签核?

相比于行为,RTL签核更侧重于结构正确性。它可用于确认RTL代码是否已实施就绪,且不存在可能影响综合、时序或物理集成的问题。

RTL签核期间执行的重要检查包括跨时钟域(CDC)、跨复位域(RDC)、Lint检查和低功耗设计意图验证。这些分析旨在发现诸如跨独立时钟域的信号不同步、复位逻辑不完整或违反命名惯例和设计规则等风险。借助新思科技VC SpyGlass和新思科技VC Formal等工具,我们能够在流程早期识别这些问题,以免它们在门级或布局层级成为缺陷。

功耗感知验证同样是RTL签核的核心原则。开发者需要确认是否已借助统一功耗格式(UPF)等技术正确定义和集成隔离单元、电压转换器和保留策略。这些结构在纯RTL层级通常是不可见的,因此需要通过综合或静态分析才能揭示它们在实际情境中的行为。

RTL和功能签核的交集

虽然功能和RTL签核用途不同,但二者紧密相连。一个用于验证设计行为,另一个则用于验证结构可行性。

两者都是设计收敛的必要条件,且能互相揭示另一种方法无法发现的问题。

二者在时间上常常并行推进,但所要解答的问题却有着本质区别。

一个领域的问题可能会影响另一个领域。

例如,在RTL签核过程中发现同步器缺失,这可能会导致间歇性故障,而这类问题单纯依靠功能覆盖率指标难以捕捉。同样地,功能签核中如果存在未经测试的状态转换,即使通过了结构检查,也可能导致芯片故障。

将这两个签核阶段视为既相互独立又协同配合的过程,有助于避免盲目乐观,帮助团队选择合适的工具和技术解决正确的问题。仿真和测试平台更适合探索应用场景和逻辑条件,而静态分析则更擅于发现设计规则违例或同步器缺失。

对于这两个阶段,新思科技Verdi可以作为通用调试平台,帮助开发者查看、分析和识别故障与覆盖率缺口的根本原因。

现代签核中的AI应用

随着验证复杂性不断增加,完成签核所需的工作量也与日俱增。传统验证流程中,工程师往往需要耗费数周时间疲于捕捉那些难以复现的极端案例,或是反复调试测试输入序列。如今,AI技术正在重塑这一现状。

VSO.ai解决了功能签核中最棘手的问题之一,即如何实现重要的覆盖率目标。区别于单纯依赖随机测试生成或人工调整的技术,该方案侧重于分析仿真数据、识别缺口并自主生成更有可能触发未测试行为的输入条件。这些功能显著降低了人工干预强度,大幅缩短了有效覆盖率目标的达成周期。

我们最新一代Verdi平台还借助AI技术增强了故障分类和根本原因分析,大幅提升了工作效率。

AI有助于提高覆盖率本身的质量,同时不可达性分析(VC Formal的一项关键功能)有助于确定RTL中永远不会被执行的部分。这使得设计团队能够将无用代码排除在覆盖率目标之外,避免在那些对功能可信度没有帮助的目标上浪费时间。

展望未来,智能体AI将带来更大潜力。通过将自然语言描述的设计规范转化为形式化断言,开发者团队将能更快、更准确地定义功能覆盖率。

构建完整的验证信心体系

功能签核和RTL签核代表着同一验证工作这枚硬币的两面,一面确认设计的行为符合预期,而另一面则确认构建方式足以支持可靠的实现。

两者同等重要,无法相互替代。在如今SoC日益异构化且对功耗极为敏感的背景下,忽视任何一个签核里程碑都将引入风险,且这种风险难以通过硅后调试彻底修复。

-

半导体

+关注

关注

339文章

31238浏览量

266571 -

RTL

+关注

关注

1文章

395浏览量

62883 -

新思科技

+关注

关注

5文章

979浏览量

52989

原文标题:RTL与功能签核:新思科技如何为异构低功耗SoC构建双重验证堡垒?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

英诺达ECDC上线RDC跨复位域检查新功能

为什么选择 Nordic 的低功耗蓝牙解决方案?

RTL8762CMF/RTL8752CMF:蓝牙低功耗SOC的卓越之选

乐鑫 ESP32-H4:新一代双核超低功耗 SoC,面向长续航与 HMI

新思科技发布全新软件定义硬件辅助验证解决方案

基于低功耗蓝牙SoC的新国标充电宝方案

西门子Questa One验证解决方案引入智能体AI功能

新思科技EDA工具和车规IP助力芯粒架构汽车SoC设计

深入解析CC430系列SoC:低功耗无线通信的理想之选

什么是低功耗设计,如何评估低功耗MCU性能?

新思科技HAPS-200助力阿里巴巴达摩院加速玄铁C930开发验证

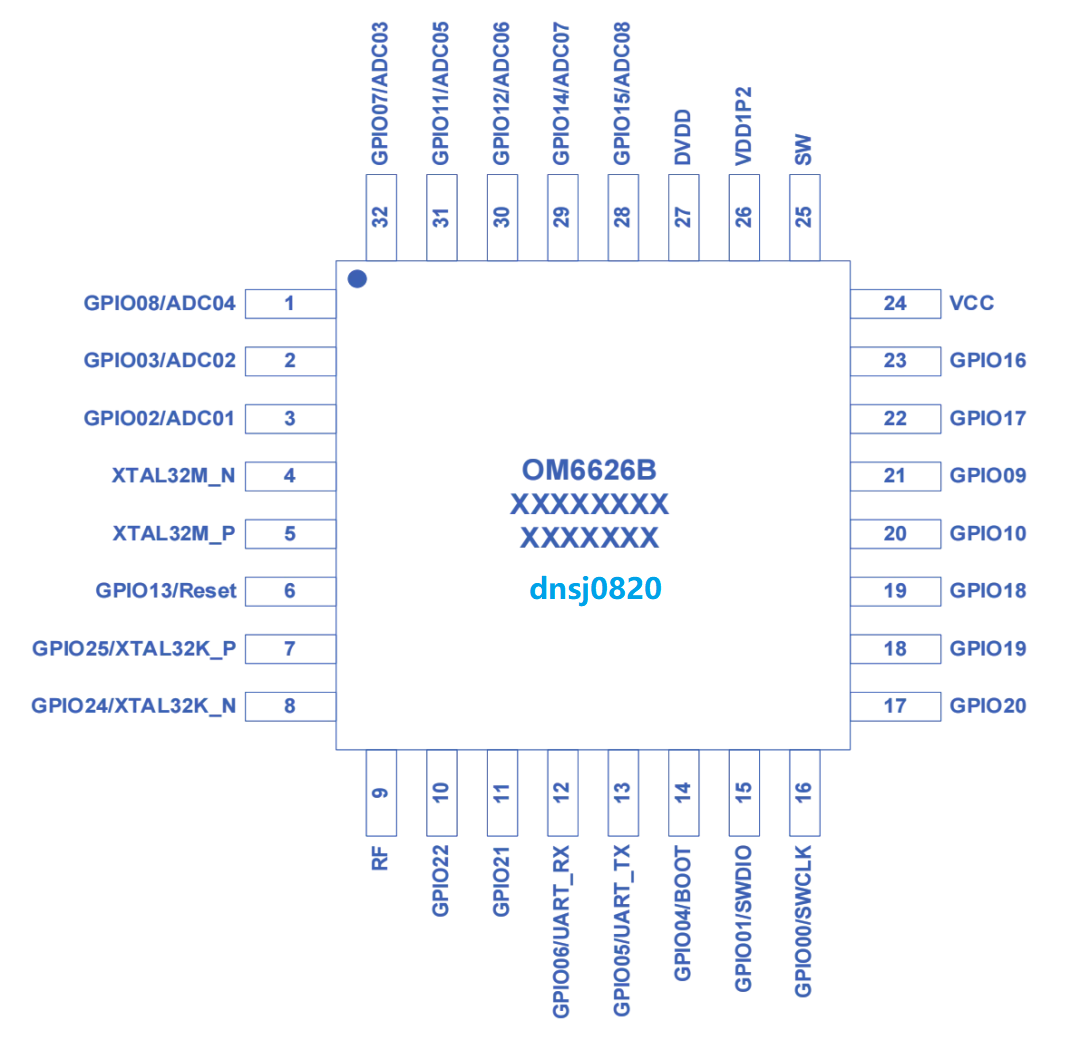

高性能超低功耗蓝牙电子价签方案 OM6626 NRF52832

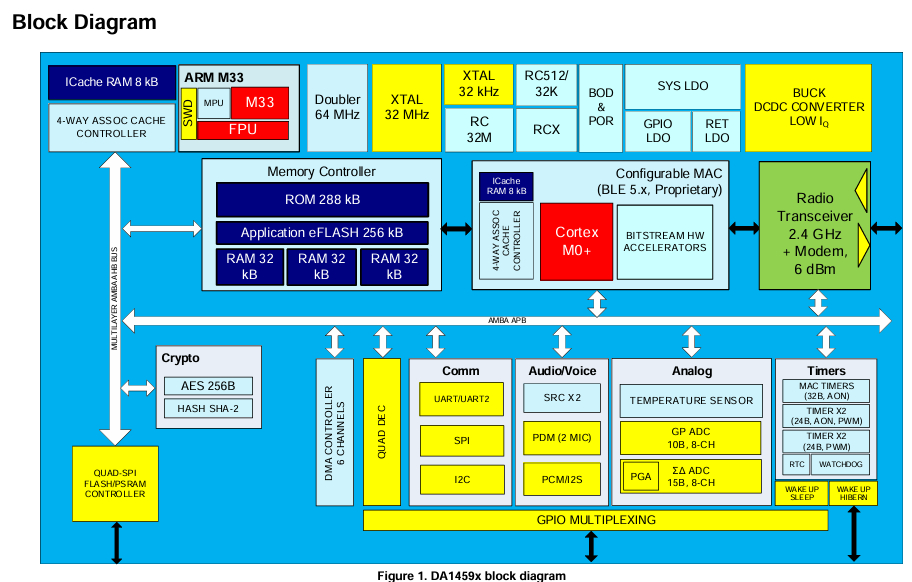

DA14594 SmartBond双核低功耗蓝牙5.3 SoC 数据手册和产品介绍

新思科技RTL与功能签核助力低功耗SoC验证

新思科技RTL与功能签核助力低功耗SoC验证

评论