拥有更佳的电性参数,并且得益于12英寸制程的稳定性,良率优异,为数字电源、数字音频功放等芯片应用提供了更具竞争力的制造方案。 作为全球领先的特色工艺纯晶圆代工企业,华虹半导体拥有先进的模拟及电源管理IC工艺平台,涵盖0.5微米到90纳米工艺节点,

2021-06-04 09:36:17 7273

7273 据国际物理系统研讨会(ISPD)上专家表示:实现14纳米芯片生产可能会比原先想象的更困难;14纳米节点给设计师带来了许多挑战。这些困难和挑战何在?详见本文...

2013-04-08 09:30:51 3956

3956 Cadence设计系统公司(Cadence Design Systems, Inc.)(纳斯达克代码:CDNS)今日宣布与TSMC签订了一项长期合作协议,共同开发16纳米FinFET技术,以其适用于

2013-04-09 11:00:05 1123

1123 楷登电子今日正式发布Cadence® Virtuoso®定制 IC设计平台的技术升级和扩展,进一步提高电子系统和 IC设计的生产力。新技术涉及Virtuoso 系列几乎所有产品,旨在为系统工程师提供更稳健的设计环境和生态系统,助其实现并分析复杂芯片、封装、电路板和系统。

2018-04-11 16:40:16 10275

10275 技术节点的每次进步都要求对制造工艺变化进行更严格的控制。最先进的工艺现在可以达到仅7 nm的fin宽度,比30个硅原子稍大一点。半导体制造已经跨越了从纳米级到原子级工艺的门槛。

2020-06-02 18:04:46 3006

3006

这是一个业界用于打造差异化定制芯片的领先平台,可借助生成式 AI 技术显著提升设计生产力; Virtuoso Studio 与 Cadence 最前沿的技术和最新的底层架构集成,助力设计工程师在

2023-04-20 15:52:13 1036

1036

3nm 时代来临了!Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示,这是

2023-05-19 16:25:12 1405

1405

有参考价值的信息。 英特尔路线图 从7nm到1.4nm 首先将目光放到最远,英特尔预计其工艺制程节点将以2年一个阶段的速度向前推进。从2019年推出10nm工艺开始(实际产品在市场上非常少见

2020-07-07 11:38:14

(Microcontroller Unit, MCU)市场,最新推出95纳米单绝缘栅非易失性嵌入式存储器(95纳米5V SG eNVM)工艺平台。在保证产品稳定性能的同时,95纳米5V SG eNVM工艺平台以其低功耗、低成本

2017-08-31 10:25:23

各位大佬好,我正在学习IC设计,对于Cadence Virtuoso这个软件有一些入门级的小问题:我从AnaglogLib拷贝NMOS管和PMOS管到自己的library下面,打开他们的CDF参数看

2017-10-16 00:26:33

Cadence设计系统公司发布了Cadence Allegro系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和技术增强。改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2018-11-23 17:02:55

结合了 3D 探索流程,利用 2D 设计网表根据用户输入创建多个 3D 堆叠场景,自动选择最佳的最终 3D 堆叠配置。此外,平台数据库支持所有 3D 设计类型,让工程师可以同时在多个工艺节点创建

2021-10-14 11:19:57

cadence virtuoso教程 1990-2006 Cadence Design Systems, Inc. All rights reserved.Printed

2012-08-10 18:37:59

PDK 套件支持我们先进的一流 IPD1 和 IPD2 工艺。此款 PDK 套件配备完全可扩展的布局参数单元 (Pcell)、先进布局实用程序以及准确的电磁 (EM) 仿真功能。此套件可应客户要求供下载

2018-10-26 08:54:41

纳米定位平台跟纳米平台的区别是什么?

2015-07-19 09:42:13

工艺节点中设计,但是 FD-SOI 技术提供最低的功率,同时可以承受辐射效应。与体 CMOS 工艺相比,28 纳米 FD-SOI 芯片的功耗将降低 70%。射频数据转换器需要同时具有高带宽和低功耗,以

2023-02-07 14:11:25

`7纳米芯片一直被视为芯片业“皇冠上的珍珠”,令全球芯片企业趋之若鹜。在大家热火朝天地竞相布局7纳米工艺时,全球第二大的芯片大厂GlobalFoundries(格罗方德,格芯,以下简称GF)突然宣布

2018-09-05 14:38:53

LS2088A的工艺节点是什么?

2023-03-17 07:12:36

:不同代工厂、不同工艺节点、不同工艺平台、不同工艺版本等 基于器件/工艺评估的设计辅助功能 模型库的质量和精度验证 内嵌超过200多个检查项的预先配置的模板 并行处理引擎,支持内嵌和外置SPICE

2020-07-01 09:34:29

STM32WL MCU 的生产工艺(nm)是多少?我们正在考虑设计一个系统,该系统必须在可能的辐射环境中运行,而工艺的纳米尺寸将对此产生影响。

2022-12-26 07:15:25

`书籍:《炬丰科技-半导体工艺》文章:GaN 纳米线制造和单光子发射器器件应用的蚀刻工艺编号:JFSJ-21-045作者:炬丰科技网址:http://www.wetsemi.com

2021-07-08 13:11:24

什么是纳米?为什么制程更小更节能?为何制程工艺的飞跃几乎都是每2年一次?

2021-02-01 07:54:00

系统,为广大国内外用户降低设计门槛。另外,该系统采用的是跨平台开发,既适用于UNIX也适用于Windows操作系统,兼容其他MEMS CAD工具软件,如L-EDIT、ANSYS等,还支持用户自主扩展其他功能模块。

2019-06-25 06:41:25

关于黑孔化工艺流程和工艺说明,看完你就懂了

2021-04-23 06:42:18

一半,而性能提高两倍。通过选择一个高性能低功耗的工艺技术,一个覆盖所有产品系列的、统一的、可扩展的架构,以及创新的工具,赛灵思将最大限度地发挥 28 纳米技术的价值, 为客户提供具备 ASIC 级功能

2019-08-09 07:27:00

小白求助,cadence里通过Library Path Editor添加工艺库文件最后一步是点击File下面的save,但是它是灰色的点不了,不知道该如何解决,求大佬指点一二,感激不尽。

2021-06-25 06:26:01

FPGA在系统中表现出的特性是由芯片制造的半导体工艺决定的,当然它们之间的关系比较复杂。过去,在每一节点会改进工艺的各个方面,每一新器件的最佳工艺选择是尺寸最小的最新工艺。现在,情况已不再如此。

2019-09-17 07:40:28

英特尔联合创始人戈登·摩尔在半世纪前提出的摩尔定律,是指每代制程工艺都要让芯片上的晶体管数量翻一番。纵观芯片每代创新历史,业界一直遵循这一定律,并按前一代制程工艺缩小约 0.7倍来对新制程节点命名

2019-07-17 06:27:10

表示将在2015年年底开始量产10nm晶圆,但在10纳米工艺制程上遇到了瓶颈及一系列因素,致该计划最终一拖再拖,英特尔公司首席执行官Brian Krzanich曾表示,下一代先进制程大约要等到2017

2016-01-25 09:38:11

请问各位大佬,Cadence610能同时装两个工艺库吗,例如TSMC和SMIC同时装上?

2021-06-25 07:42:12

纳米磁性薄膜材料的湿法工艺冯则坤,何华辉关键词:纳米薄膜,磁性材料,电镀摘 要:介绍了纳米磁性薄膜材料特性、类型,综述了近年来兴起的湿法工艺及其用湿法

2010-02-07 16:42:46 37

37 台积电率先量产40纳米工艺

台积电公司日前表示,40纳米泛用型(40G)及40纳米低耗电(40LP)工艺正式进入量产,成为专业集成电路制造服务领域唯一量产40纳米工艺的公司

2008-11-22 18:27:07 1112

1112 随着微电子技术的进步,超大规模集成电路(VLSI)的特征尺寸已经步入纳米范围。纳米级工艺存在着很多不同于以往微米、亚微米工艺的特点,因此为制造和设计都带来了很多难题,诸

2011-05-28 16:36:27 0

0 ARM处理器部门主管西蒙·赛加斯(Simon Segars)周一在Computex大展上表示,采用20纳米工艺生产的ARM芯片最快将于明年底发布

2012-06-05 08:57:19 1108

1108 ARM处理器部门主管西蒙·赛加斯(SimonSegars)周一在Computex大展上表示,采用20纳米工艺生产的ARM芯片最快将于明年底发布。赛加斯说:“整个行业都推进下一代技术,只要在经济和技

2012-06-06 08:55:04 1665

1665 Cadence与三星的合作为移动消费电子产品带来了新的工艺进展,使得20纳米及未来工艺节点设计成为可能。

2012-06-10 10:43:54 1438

1438 随着芯片微缩,开发先进工艺技术的成本也越来越高。TSMC对外发言人孙又文表示,台积电会继续先进工艺技术节点的投入和开发,今年年底台积电将推出20nm工艺

2012-08-30 14:34:30 2301

2301 全球电子设计创新领先企业Cadence设计系统公司日前宣布TSMC已选择Cadence解决方案作为其20纳米的设计架构。Cadence解决方案包括Virtuoso定制/模拟以及Encounter RTL-to-Signoff平台。

2012-10-22 16:48:03 1286

1286 该14纳米产品体系与芯片是ARM、Cadence与IBM之间在14纳米及以上高级工艺节点上开发系统级芯片(SoC)多年努力的重要里程碑。使用FinFET技术以14纳米标准设计的SoC能够大幅降低功耗。 这

2012-11-16 14:35:55 1642

1642 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)近日宣布,GLOBALFOUNDRIES已携手Cadence®,为其20和14纳米制程提供模式分类数据

2013-05-13 10:20:02 1094

1094 为专注于解决先进节点设计的日益复杂性,全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布,台积电已与Cadence在Virtuoso定制和模拟设计平台扩大合作以设计和验证其尖端IP。

2013-07-10 13:07:23 1201

1201 全球电子创新设计Cadence公司与上海华力微电子,15日共同宣布了华力微电子基于Cadence Encounter数字技术交付55纳米平台的参考设计流程。华力微电子首次在其已建立55纳米工艺上实现了从RTL到GDSII的完整流程。

2013-08-16 11:08:11 2474

2474 中芯国际新款40纳米 Reference Flow5.1结合了最先进的Cadence CCOpt和GigaOpt工艺以及Tempus 时序签收解决方案, 新款RTL-to-GDSII数字流程支持Cadence的分层低功耗流程和最新版本的通用功率格式(CPF).

2013-09-05 10:45:03 2485

2485 2016年3月22日,中国上海——楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日宣布,用于10纳米 FinFET工艺的数字、定制/模拟和签核工具通过台积电(TSMC)V1.0设计参考手册(DRM)及SPICE认证。

2016-03-22 13:54:54 1453

1453 FastSPICE™ (AFS) 平台。除此之外,Calibre 和 Analog FastSPICE 平台已可应用在基于TSMC 7 纳米 FinFET 工艺最新设计规则手册 (DRM) 和 SPICE 模型的初期设计开发和 IP 设计。

2016-03-24 11:13:19 1110

1110 4月15日,中国上海—楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日宣布Cadence® Virtuoso® 版图依赖效应(Layout-Dependent Effects

2016-04-15 10:09:07 2638

2638 “我们与 Cadence 密切合作开发参考流程,帮助我们的客户加快其差异化的低功耗、高性能芯片的设计,”中芯国际设计服务中心资深副总裁汤天申博士表示,“Cadence创新的数字实现工具与中芯国际28纳米工艺的紧密结合,能够帮助设计团队将28纳米设计达到更低的功耗以及更快的量产化。”

2016-06-08 16:09:56 3225

3225 节点FinFET技术,7LPP和8LPP工艺技术不仅进一步优化了功耗、性能和面积特性,扩展能力也更为出色。目前,客户已经可以应用下一代技术开始早期设计。

2017-06-02 16:04:34 1668

1668 中国上海,2017年6月12日 – 楷登电子(美国Cadence公司,NASDAQ: CDNS)今日发布全新Cadence® Virtuoso® System Design Platform

2017-06-13 14:26:28 3882

3882 赛灵思、Arm、Cadence和台积公司今日宣布一项合作,将共同构建首款基于台积7纳米FinFET工艺的支持芯片间缓存一致性(CCIX)的加速器测试芯片,并计划在2018年交付

2017-09-23 10:32:12 4604

4604 赛灵思、Arm、Cadence和台积公司今日宣布计划在 2018 年交付 7 纳米 FinFET 工艺芯片。这一测试芯片旨在从硅芯片层面证明 CCIX 能够支持多核高性能 Arm CPU 和 FPGA 加速器实现一致性互联。

2017-09-25 11:20:20 7378

7378 7纳米工艺将成为明年的重点制程工艺,但受成本太高的原因,据悉明年仅三星苹果两家手机继续采用7纳米处理器。高通没有采用台积电最新的7纳米工艺,会继续延用三星电子的10纳米工艺。

2017-12-14 08:59:36 6647

6647 据国外媒体报道,芯片代工商 台积电 的CEO魏哲家日前透露,他们的7纳米工艺已投入生产,更先进的5纳米工艺最快会在明年底投产。

2018-08-01 16:48:34 3903

3903 据国外媒体援引业内人士的观点指出,由于10纳米以下芯片的生产工作需要大量资本投入,大量芯片制造商纷纷基于成本考虑选择将业务重点继续放在现有14/12纳米工艺上,同时减缓了自己对更先进纳米工艺的投资脚步。

2018-09-09 09:35:33 4847

4847 解决方案。这次Credo的第三个硅验证的7纳米112G SerDes架构现允许系统级芯片(SoC)的研发来采用台积公司先进的7纳米工艺节点。

2018-10-30 11:11:12 5979

5979 IRIS为IC设计人员提供了一种在主流设计环境中运行复杂的3D EM分析的简单方法。IRIS基于加速矩量法(MoM)的全波电磁求解器引擎已在多个先进工艺节点上验证了其准确性。Virtuoso无缝集成

2018-11-20 14:22:14 4779

4779 目前来看,在资本与技术拉高进入门槛下,GlobalFoundries(GF)退场、代工并非本业的英特尔则放弃代工业务,7纳米以下先进工艺代工战场已成为台积电、三星晶圆代工双雄对战竞况。

2018-12-21 10:55:44 3504

3504 最近,三星以及台积电在先进半导体制程打得相当火热,彼此都想要在晶圆代工中抢得先机以争取订单,几乎成了14纳米与16纳米之争,然而14纳米与16纳米这两个数字的究竟意义为何,指的又是哪个部位?而在缩小工艺后又将来带来什么好处与难题?以下我们将就纳米工艺做简单的说明。

2019-04-29 10:35:44 10662

10662

即将到来的“N6”工艺节点将使用与“N7”节点相同的设计规则,使客户更容易转换到更新,更密集的节点。

2019-05-06 15:27:00 2691

2691 三星的3nm工艺节点采用的GAAFET晶体管是什么?

2019-05-17 15:38:54 12185

12185

5月29日,在今天的台北国际电脑展上,联发科对外发布全新5G移动平台,该款多模 5G系统单芯片(SoC)采用7nm工艺制造。

2019-05-29 17:01:15 3730

3730 柏燕民表示,中兴的5G芯片已经发展到了第三代产品,基于7纳米工艺,相关产品将在下半发布

2019-06-28 10:27:40 3883

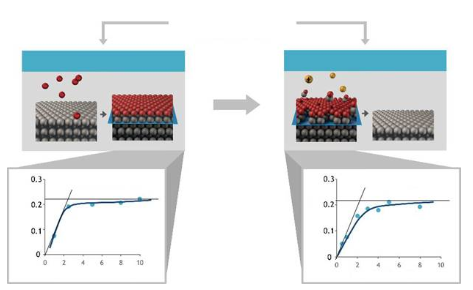

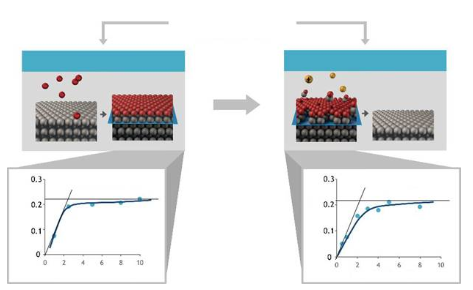

3883 集成电路设计自动化软件领导企业新思(Synopsys)近日宣布,面向三星7LPP(7nm Low Power Plus)和更先进工艺的良率学习平台设计取得最大突破,也为三星后续5nm、4nm、3nm工艺的量产和良品率奠定了坚实基础。

2019-07-08 15:56:45 3656

3656 英特尔预计其制造工艺节点技术将保持2年一飞跃的节奏,从2019年的10纳米工艺开始,到2021年转向7纳米EUV(极紫外光刻),然后在2023年采用5纳米,2025年3纳米,2027年2纳米,最终到2029年的1.4纳米。

2019-12-11 10:31:20 3933

3933 12月11日消息,据外媒报道,在今年的IEEE国际电子设备会议(IEDM)上,芯片巨头英特尔发布了2019年到2029年未来十年制造工艺扩展路线图,包括2029年推出1.4纳米制造工艺。

2019-12-11 14:37:11 3912

3912 12月11日消息,据外媒报道,在今年的IEEE国际电子设备会议(IEDM)上,芯片巨头英特尔发布了2019年到2029年未来十年制造工艺扩展路线图,包括2029年推出1.4纳米制造工艺。

2019-12-12 15:21:11 3237

3237 作为中国半导体行业最薄弱但也是最重要的环节,芯片工艺一直是国内的痛点,所以国内最大的晶圆代工厂中芯国际任重而道远。此前中芯国际已经表态14nm工艺已经试产,今年就会迎来一轮爆发,年底的产能将达到目前的3-5倍,同时今年内还有可能试产更先进的7nm工艺。

2020-01-07 09:54:45 6543

6543 在摩尔定律迈向5纳米之际,人们的目光多被几家半导体公司间的先进工艺之争所吸引。然而,逻辑芯片的制造工艺极其复杂多样,5纳米、7纳米等标准工艺只是一部分,晶圆代工厂可以发展的制造工艺平台还有很多,如

2020-06-10 14:35:25 2474

2474 作为中国大陆技术最先进、规模最大的晶圆代工企业,中芯国际的制程工艺发展一直备受关注。历经20年,其制程工艺从0.18微米技术节点发展至如今的N+1工艺。

2020-10-20 16:50:10 8031

8031 12月9日,美国芯片巨头高通已经悄然成为台积电7纳米半导体制造工艺节点的最大客户,并已经向苹果发运1.76亿个5G调制解调器。

2020-12-10 14:10:16 1809

1809 性能、功耗和面积 (PPA) 目标受多个静态指标影响,包括时钟和数据路径时序、版图规划以及特定电压水平下的功耗。这些指标会进一步推动技术库的表征,设计优化和签核收敛。 先进工艺节点设计,尤其是高性能

2021-05-06 11:12:01 2951

2951 Cadence 数字和定制/模拟先进工艺节点解决方案支持 Cadence 智能系统设计(Intelligent System Design)战略,旨在系统级芯片(SoC)上实现卓越设计,如需了解更多信息,请访问:

2021-10-26 14:44:47 4148

4148 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence® 数字全流程获得了 GlobalFoundries (GF) 12LP/12LP+ 工艺平台认证,以推动移动和消费市场的航空航天、超大规模计算、人工智能、移动和消费电子应用的设计。

2022-05-24 16:33:23 2260

2260 就晶体管数量和复杂性而言,先进工艺节点的设计尺寸正在迅速增加。因此,Veloce Strato 仿真平台可扩展到 150 亿门。

2022-06-29 15:23:24 987

987 5纳米芯片相比7纳米芯片的工艺技术要求更高、更好更低、性能更好。芯片工艺中5nm和7nm的两个数值,代表的是芯片晶体管导电沟道的长度。

2022-06-29 17:00:39 30825

30825 在芯片设计和制造中,纳米表示的是芯片中晶体管与晶体管之间的距离,在体积相同大小的情况下,7纳米工艺的芯片容纳的晶体管的数量,几乎是14纳米工艺芯片的2倍。

2022-07-06 16:35:55 136833

136833 工艺认证,支持新的设计规则手册(DRM)和 FINFLEX 技术。通过持续的合作,两家公司还提供了相应的 N4P 和 N3E 工艺设计套件(PDKs),可加快移动、人工智能和超大规模计算先进节点

2022-10-27 11:01:37 2277

2277 中芯国际南方厂2019年实现了14nm工艺的量产,该生产线总投资90.59亿美元,产能3.5万片/月,代表作麒麟710A;但在2020年中芯国际被纳入了实体清单,被卡在10nm(含)工艺节点。

2023-03-14 10:45:24 50489

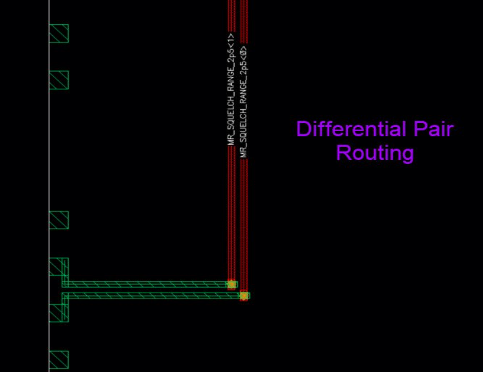

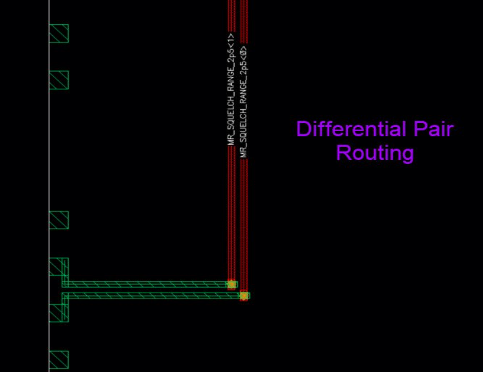

50489 交互式路由允许您在自动路由之前完成关键网络,并在自动路由后完成未布线的不完整网络。Virtuoso 交互式和辅助路由功能允许您在 Virtuoso 环境中以交互方式路由连接,以满足关键的设计约束和规则。在所有工艺节点上启用交互式和自动布线功能,包括最先进的工艺技术。

2023-04-20 10:58:23 4447

4447

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Virtuoso Design Platform 的节点到节点设计迁移流程,能兼容所有的台积电先进节点

2023-05-06 15:02:15 1934

1934 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 数字和定制/模拟设计流程已通过 TSMC N3E 和 N2 先进工艺的设计规则手册(DRM)认证。两家公司还发布

2023-05-09 10:09:23 2046

2046 3nm 时代来临了!Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示,这是 Cadence 112G-ELR SerDes IP 系列产品的新成员。

2023-05-19 15:23:07 1735

1735

了新一代定制设计平台 Cadence Virtuoso Studio ,该平台采用全新的底层架构,以独特的方法来管理设计流程,可将当今大型设计的设计同步吞吐量提升 3 倍,是面临大型复杂项目和有短时间

2023-06-13 12:15:02 3455

3455

,2023 年 6 月 30 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,基于 AI 的 Cadence Virtuoso Studio 设计工具和解决方案已获得 Samsung Foundry 认证。 双方的共同客户可以放心利用 Virtuoso Studio 和

2023-06-30 10:08:30 2222

2222 先进节点经过优化 中国上海, 2023 年 7 月 4 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,搭载最新生成式 AI 技术的 Cadence Virtuoso

2023-07-04 10:10:01 1516

1516 已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ● Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio,已

2023-07-05 10:10:01 1140

1140 已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ●Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio,已针对

2023-07-05 10:12:14 1322

1322 3nm 时代来临了!Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示,这是 Cadence 112G-ELR SerDes IP 系列产品的新成员。

2023-07-10 09:26:20 1241

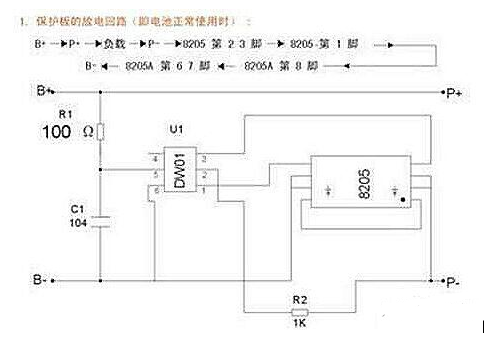

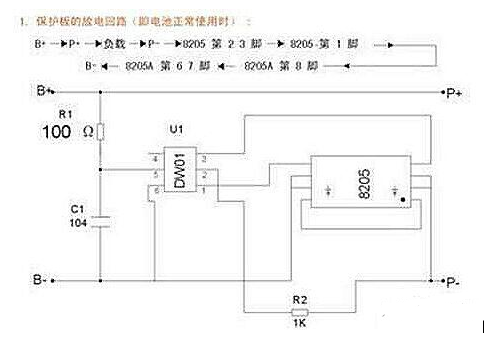

1241 电池保护IC(Integrated Circuit)的纳米工艺并没有固定的规定或标准。电池保护IC的制造工艺通常与集成电路制造工艺一样,采用从较大的微米级工艺(如180nm、90nm、65nm等)逐渐进化到更先进的纳米级工艺(如45nm、28nm、14nm等)。

2023-07-11 15:42:37 3464

3464

了新一代定制设计平台 Cadence Virtuoso Studio ,该平台采用全新的底层架构,以独特的方法来管理设计流程,可将当今大型设计的设计同步吞吐量提升 3 倍,是面临大型复杂项目和有短时间

2023-09-01 12:20:01 1452

1452

Cadence Virtuoso定制设计平台的一套全面的集成电流(IC)设计系统,能够在多个工艺节点上加速定制IC的精确芯片设计,其定制设计平台为模拟、射频及混合信号IC提供了极其方便、快捷而精确的设计方式。

2023-09-11 15:14:16 12455

12455

// 中国上海,2023 年 9 月 27 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布扩展基于 Cadence Virtuoso Studio 的节点到节点设计迁移

2023-09-27 10:10:04 1634

1634 来源:IMEC 设计探路PDK降低了学术界和工业界接触最先进半导体技术的门槛 在2024年IEEE国际固态电路会议 (ISSCC) 上,世界领先的纳米电子和数字技术研究与创新中心imec推出了其

2024-02-22 18:24:00 1476

1476 如今,一颗芯片可以集成数十亿个晶体管,晶体管排列越紧密,所需的工艺节点就越小,某些制造工艺已经达到 5 纳米甚至更小的节点。

2024-04-11 15:02:16 1668

1668

近日,安森美(onsemi,纳斯达克股票代号:ON)宣布推出Treo平台,这是一个采用先进的65nm节点的BCD(Bipolar–CMOS-DMOS)工艺技术构建的模拟和混合信号平台。该平台为安森美

2024-11-12 11:03:21 1375

1375 本文介绍了7纳米工艺面临的各种挑战与解决方案。 一、什么是7纳米工艺? 在谈论7纳米工艺之前,我们先了解一下“纳米”是什么意思。纳米(nm)是一个长度单位,1纳米等于10的负九次方米。对于半导体芯片

2024-12-17 11:32:21 2561

2561 当前全球半导体工艺水平已进入纳米级突破阶段,各大厂商在制程节点、材料创新、封装技术和能效优化等方面展开激烈竞争。以下是目前最先进的半导体工艺水平的详细介绍: 一、制程工艺突破 英特尔18A(约

2025-10-15 13:58:16 1420

1420

电子发烧友App

电子发烧友App

评论