内容提要

● Cadence 和 Samsung 的合作,使客户能够利用两个公司最新的技术,进行手机、汽车、AI 和超大规模设计的创新

● 工程师们能够在 PDK 上设计 IC 产品,这些 PDK 已经过 SF2 和 SF3 流程认证

●Cadence 数字全流程针对先进节点实现了最佳 PPA 结果

●Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio,已针对最新节点进行优化

中国上海, 2023 年 7 月 5 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,其数字和定制/模拟流程已通过 Samsung Foundry 的 SF2 和 SF3 工艺技术认证。两家公司还合作开发了新的制程设计套件(PDK),旨在简化于这些最新节点上的移动、汽车、AI 和超大规模 IC 产品的流程。双方的共同客户现正在积极使用 Cadence流程,全力开发基于 SF2 和 SF3 工艺的设计。

Cadence 数字工具

针对 SF2 和 SF3 技术进行优化

Cadence 全面的 Cadence RTL-to-GDS 设计流程支持 Samsung 的 SF2 和 SF3 技术,可提供最佳的功率、性能和面积(PPA)结果。该流程包括 GenusSynthesis Solution、Modus DFT Software Solution、InnovusImplementation System、QuantusExtraction Solution 及 Quantus Field Solver、TempusTiming Signoff Solution 以及 Tempus ECO Option、PegasusVerification System、LiberateCharacterization Portfolio、VoltusIC Power Integrity Solution 和 Cadence CerebrusIntelligent Chip Explorer。

借助这个经过认证的流程,客户能轻松实现先进节点上的 IC 设计。比如支持单元交换旨在帮助设计人员对齐单元引脚,进行直接连接,以节省布线资源;支持混合行(各种组合)解决方案,以最大化基于面积的设计规则;利用有 mask 位移的单元和在水平方向上有半轨道位移的单元,工具具有摆放和精细调整走线的能力,可以减少移位;支持各种直线型不规则形状的标准单元,以实现更高的密度;以及插入增强过的、兼顾 trim metal 的通孔钉,以减少压降。

Cadence 定制/模拟工具

针对 SF2 和 SF3 技术经过优化

Cadence 定制和模拟工具针对 Samsung 的 SF3 和 SF2 节点经过优化,包括基于 AI 的 VirtuosoStudio 设计工具——Virtuoso Schematic Editor、Virtuoso ADE Suite 及 Cadence Virtuoso Layout Suite——SpectreSimulation Platform——Spectre X Simulator、Spectre FX 及 Spectre RF,以及 Voltus-XFi Custom Power Integrity Solution。

定制/模拟设计工具是客户的得力助手,可提供更好的工艺角仿真管理、统计分析、中心化设计和电路优化;支持在现代计算集群、私有云及公共云配置上并行操作;在整个 layout 环境中提供更好的性能和可扩展性;混合信号 OpenAccess 设计套件与 Innovus Implementation 的摆放和布线引擎无缝集成,提高结果质量;汇总 EM-IR 信息,高亮违例和详细的电阻值、金属层、宽度和长度信息;提供电路性能和可靠性方面的反馈。

“

“得益于此次与 Cadence 的合作,已有客户成功利用 Cadence 经过认证的设计流程和我们先进的 SF2 和 SF3 工艺技术提高了生产力,”Samsung Electronics 代工厂设计技术团队副总裁 Sangyun Kim 说,“利用新的 PDK,开发人员在开发下一代移动、汽车、人工智能和超大规模设计的时候能更简单、更快地将创新产品推向市场。”

“

“Cadence 研发团队与 Samsung Foundry 团队精诚合作,针对 Samsung 的 SF2 和 SF3 工艺技术精细调整我们相应的数字和定制/模拟流程,以帮助客户提高设计效率,”Cadence 数字和签核事业部副总裁 Vivek Mishra 表示,“我们的数字流程有PPA方面的优势,而我们的定制/模拟流程依托 Virtuoso Studio,为定制 IP 开发设定了新的标准,助力双方的共同客户利用 Samsung 的 SF2 和 SF3 工艺技术推进产品创新。”

Cadence 的数字和定制/模拟设计流程支持 Cadence 的智能系统设计(Intelligent System Design)战略,旨在实现系统级芯片(SoC)的卓越设计。

要了解更多关于

Cadence 先进节点解决方案信息,请访问 www.cadence.com/go/advdndsf2sf3

(您可复制至浏览器或点击阅读原文打开)

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续九年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站www.cadence.com。

2023 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

-

Cadence

+关注

关注

68文章

1031浏览量

147386

发布评论请先 登录

Freescale K40P100M100SF2芯片:性能卓越的嵌入式解决方案

NXP K20P100M100SF2V2芯片:设计工程师的全面指南

MUN3CAD03-SF:多场景电源模块替代的优选方案

MUN3CAD03-SF:多场景电源模块替代的优选方案

三星2nm良率提升至50%,2027年前实现晶圆代工业务盈利可期

松下SF系列超薄安全继电器:设计与应用的全面解析

安森美NHP160SF与NRVHP160SF:SOD - 123FL封装超快功率整流器的卓越之选

对 AN65974 项目中 SF_streamIN.img 和 SF_streamOUT.img 的使用有疑问,求解答

Cadence扩大与三星晶圆代工厂的合作

无线SF6传感器是干什么用

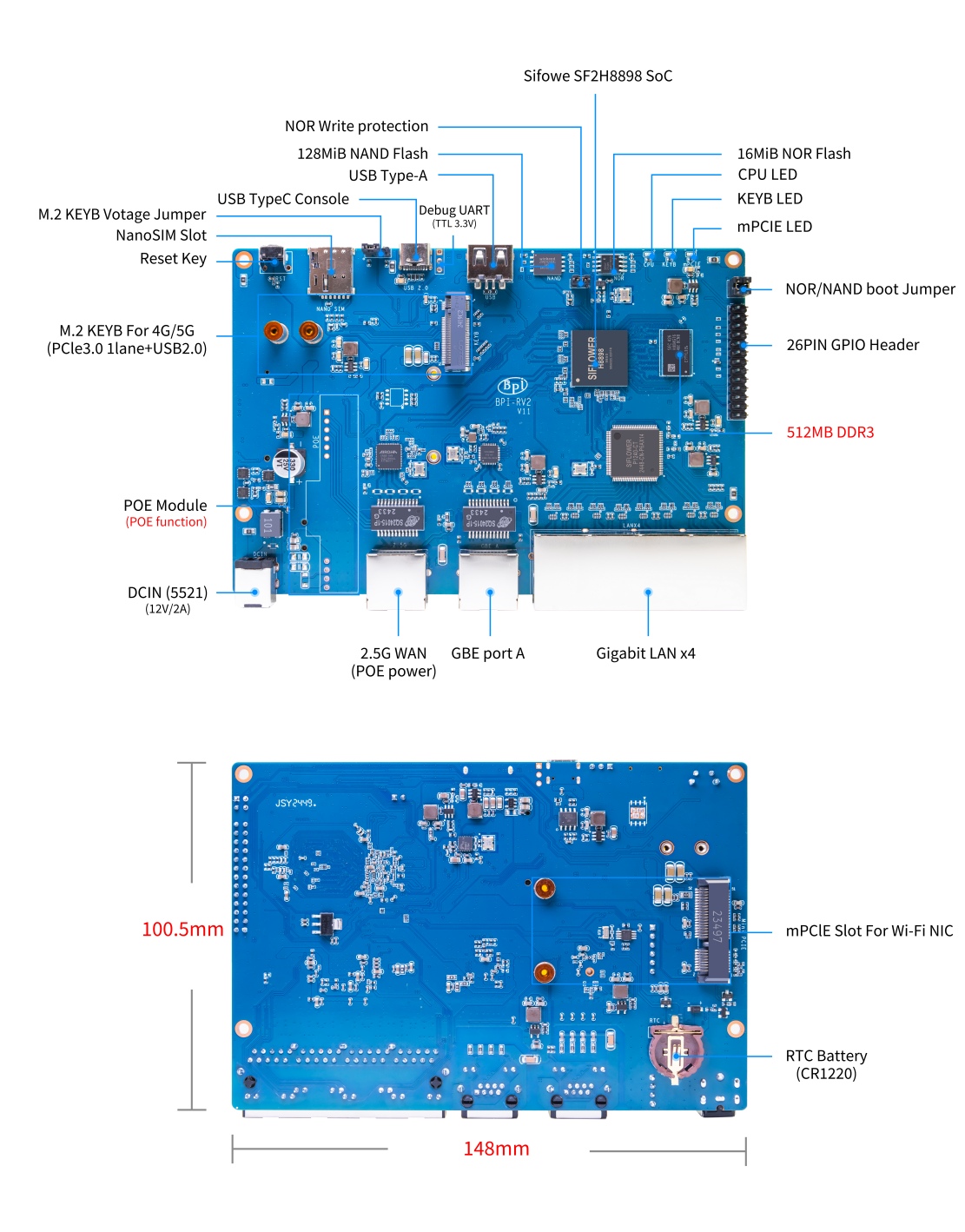

香蕉派BPI-RV2 RISC-V路由器开发板矽昌 SF21H8898网关SOC设计

Cadence 数字和定制/模拟设计流程获得 Samsung Foundry SF2 和 SF3 工艺技术认证

Cadence 数字和定制/模拟设计流程获得 Samsung Foundry SF2 和 SF3 工艺技术认证

评论