在芯片设计和制造中,纳米表示的是芯片中晶体管与晶体管之间的距离,在体积相同大小的情况下,7纳米工艺的芯片容纳的晶体管的数量,几乎是14纳米工艺芯片的2倍。

7nm芯片:7nm,也就是7纳米,它是一个长度单位。在集成电路领域完整的叫法应该是7nm制程工艺,或者7nm工艺。它表示在集成电路(芯片)中,一个元件的尺寸可以做到7nm那么微小。以此类推,16nm工艺的意思是元件可以做到16nm大小。很显然,元件尺寸越微小,技术越先进,制造难度越高。

先进的蚀刻技术还可以减小晶体管间电阻,让CPU所需的电压降低,从而使驱动它们所需要的功率也大幅度减小,有效降低功耗和发热量。因此,7纳米芯片不仅意味着尺寸面积更小,各方面的表现也会代际提升。

综合链门户和码不亭蹄整合

审核编辑:郭婷

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54443浏览量

469446 -

cpu

+关注

关注

68文章

11331浏览量

225908 -

纳米

+关注

关注

2文章

731浏览量

42652

发布评论请先 登录

相关推荐

热点推荐

华中科技大学:研发纳米材料与MEMS的“微纳合奏”传感芯片

和熊掌不可兼得”的难题:高性能纳米功能材料往往与硅基加工工艺(如强碱性腐蚀液TMAH)不兼容。传统“先制造结构,后转移材料”模式,极易导致纳米薄膜厚度不均匀或传感器件结构受损,严重制约了芯片的灵敏度和一致性。长期以来,如何将高性

纳米AZO

纳米AZO 杭州九湖新材料科技有限公司 热线 壹伍贰陆捌壹捌贰伍零玖 李经理

基本信息:

特点:在Zn0中掺杂A1203简称AZ0,耐高温,导电性好,高温稳定性强,防辐射性能好。该产品是一种价格相对

发表于 03-23 13:22

3纳米芯片的发展对锡膏行业的挑战?

3纳米芯片的发展对锡膏行业提出了更高技术要求、加剧了市场竞争、推动了材料创新并带来了成本控制压力,但同时也为行业带来了新的市场机遇。下面是一些应对策略与亮点可简要概括:

台积电熊本二厂转攻2纳米背后:AI需求重塑半导体供应链,国产功率器件迎机遇

台积电2024年宣布兴建的日本熊本二厂,在10月动工不到两月便因制程规划调整暂停。据悉,原计划的6/7纳米制程因市场需求下滑被弃用,最新方案拟跳过4纳米直接转向2纳米,以适配辉达、超微

光刻机的“精度锚点”:石英压力传感器如何守护纳米级工艺

在7纳米、3纳米等先进芯片制造中,光刻机0.1纳米级的曝光精度离不开高精度石英压力传感器的支撑,其作为“隐形功臣”,是保障工艺稳定、设备安全

决战纳米级缺陷!东亚合成IXEPLAS纳米离子捕捉剂如何助力先进封装?

随着芯片制程不断微缩,先进封装中的离子迁移问题愈发凸显。传统微米级添加剂面临分散不均、影响流动性等挑战。本文将深度解析日本东亚合成IXEPLAS纳米级离子捕捉剂的技术突破,及其在解决高密度封装可靠性难题上的独特优势。

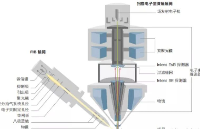

纳米加工技术的核心:聚焦离子束及其应用

聚焦离子束技术的崛起在纳米科技蓬勃发展的浪潮中,纳米尺度制造业正以前所未有的速度崛起,而纳米加工技术则是这一领域的心脏。聚焦离子束(FocusedIonBeam,FIB)作为纳米加工的

MediaTek采用台积电2纳米制程开发芯片

MediaTek 今日宣布,MediaTek 首款采用台积电 2 纳米制程的旗舰系统单芯片(SoC)已成功完成设计流片(Tape out),成为首批采用该技术的公司之一,并预计明年底进入量产。双方

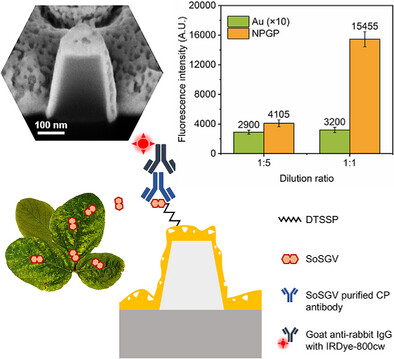

上海交通大学:研究可调多孔金覆盖纳米光学天线生物传感芯片

,如何最大化利用纳米光学结构的等离子共振效应,使得低浓度、低样本量目标分子在生物免疫实验中达到更高的检测信号强度是技术创新的关键。本项研究通过三维纳米级制造方法,批量化制造具有宏观阵列结构与纳米级金属孔径的

今日看点丨台积电开除多名违规获取2纳米芯片信息的员工,苹果脑控实机视频曝光

违规获取2纳米芯片信息,台积电开除多名员工 据《日经亚洲》报道,台积电已开除多名违反尖端芯片技术敏感信息获取规定的员工,并就此启动法律程序。多位知情人士透露,多名台积电前员工涉嫌在任

发表于 08-06 09:34

•1881次阅读

中芯国际 7 纳米工艺突破:代工龙头的技术跃迁与拓能半导体的封装革命

流转。这家全球第三大晶圆代工厂,正以每月 3 万片的产能推进 7 纳米工艺客户验证,标志着中国大陆在先进制程领域的实质性突破。 技术突围的底层逻辑 中芯国际的 7 纳米工艺采用自主研发

下一代高速芯片晶体管解制造问题解决了!

晶体管的密度,同时减少了芯片的横向面积。

相比传统的FinFET和纳米片晶体管,叉片晶体管能够显著减少nFET和pFET之间的间距,从而在相同的芯片面积上容纳更多的晶体管。例如,IMEC的2nm叉片晶

发表于 06-20 10:40

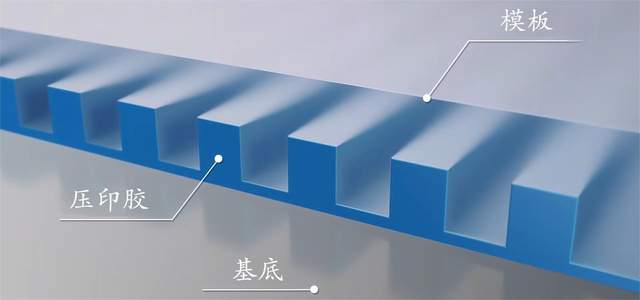

压电纳米定位系统如何重塑纳米压印精度边界

的问题,还存在工艺复杂度大幅增加的瓶颈。而纳米压印技术凭借其在高分辨率加工、低成本生产以及高量产效率等方面的显著优势,正逐步成为下一代微纳制造领域的核心技术之一。 (注:图片来源于网络) 一、纳米压印:芯片制造领域的

超声波指纹模组灵敏度飞升!低温纳米烧结银浆立大功

”

除了优异的导电性能,低温纳米烧结银浆对各种基材的优良粘附性也是提升指纹模组灵敏度的重要因素。在指纹模组中,银浆需要与传感器芯片、基板等多个部件紧密连接,确保整个电路系统的稳定运行。

低温纳米烧结银

发表于 05-22 10:26

7纳米芯片什么意思 7纳米芯片多大

7纳米芯片什么意思 7纳米芯片多大

评论