新品采用高爬电距离TO-247-4引脚封装的CoolSiC1400VMOSFETG2CoolSiC1400VMOSFETG2器件采用TO-247-4引脚封装,兼具前沿的SiC技术与高爬电距离的坚固

2026-01-04 17:06:49 679

679

怎么封装函数库,只留一些回调函数和引脚定义,完整程序不让人看

2025-12-22 13:49:13

电子发烧友网综合报道 TOLL(TO-LeadLess,薄型无引脚)封装得益于其高密度、小型化的特性,在近年受到了功率半导体厂商的关注,在SiC、GaN等宽禁带半导体中得到越来越多的应用。 近期

2025-12-20 07:40:00 9993

9993 本产品是一款小型液压纽扣电池封装机产品。标准配置可用于封装CR2016、CR2032纽扣电池。也可更换部分模具配件后封装CR2450、CR2012等纽扣电池.具有体积小,操作方便,成型精确等优点。主要应用于电池材料研发的样本制作。

2025-12-02 15:42:37 316

316

TPS650061RUKR进行电源设计。电源输出1.2v,1.8v,3.3v均正常。

由于板子未挂载SDRAM或DDR,将程序的下载地址改为L2RAM(0x11800000)位置也没办法正确load,并通过JTAG调试

2025-11-19 19:53:00

无论是4引脚还是6引脚封装,有源晶振的核心都是一个集成了振荡电路与石英晶体的完整振荡器。 其核心功能一致:只需施加额定电源电压(通常为3.3V或5V),即可在输出引脚产生稳定、精确的方波时钟信号,无需任何外部元件。供电是其唯一必要的工作条件。

2025-11-08 15:25:39 2097

2097

下面是HummingBird EV Kit给的版图,其中DDR3_D0对应的应该是板子上的FPGA的C2引脚:

不过我在配置MIG的时候,通过读入ucf文件的方式配置DDR3 SDRAM的引脚

2025-11-06 07:57:09

电子发烧友网站提供《DDR3 SDRAM参考设计手册.pdf》资料免费下载

2025-11-05 17:04:01 4

4 1、概 述

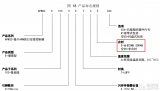

型号:FZH1631

厂商:深圳市方中禾科技有限公司(Premier Chip Limited)

FZH1631是一款标准I2C接口通讯LCD控制/驱动芯片。该芯片提供1/4占空比和1

2025-11-04 09:22:32

在有些情况下,我们想要把代码放到SDRAM运行。下面介绍在APM32的MCU中,如何把代码重定位到SDRAM运行。对于不同APM32系列的MCU,方法都是一样的。

2025-11-04 09:14:18 4981

4981

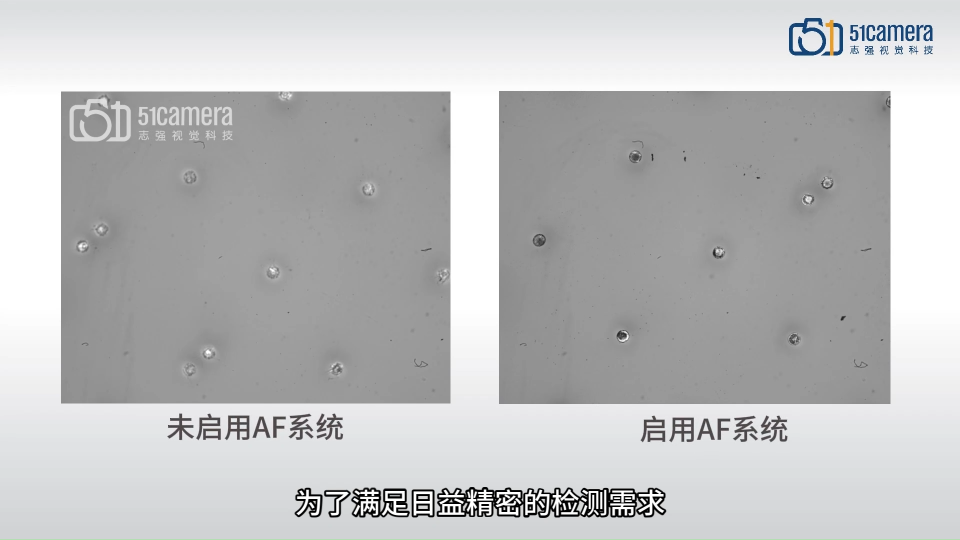

,对企业优化制程、提升产品良率至关重要。

一、核心功能定位:从“形态塑造”到“缺陷修正”

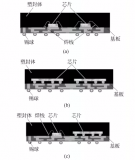

引脚成型:实现引脚的“标准成形”

引脚成型设备的核心功能,是在芯片封装制程中完成引脚的初次塑形。它将原始的直线状引脚

2025-10-30 10:03:58

近期,科准测控小编收到了不少来自半导体行业客户的咨询,大家最关心的问题之一便是:“IC管脚推力测试,我们该用什么设备?” 这确实是一个核心问题。 在集成电路(IC)封装领域,芯片与引线框架或基板之间

2025-10-27 10:42:44 339

339

2 级标准)的引脚图、接线图、封装手册、中文资料、英文资料,0.1 至 8.5 GHz SPDT 开关(符合 AEC-Q100 2 级标准)真值表,0.1 至 8.5 GHz SPDT 开关(符合 AEC-Q100 2 级标准)管脚等资料,希望可以帮助到广大的电子工程师们。

2025-10-21 18:32:18

而研制的。总体说来,它大概有三次重大的革新:第一次是在上世纪 80 年代从引脚插入式封装到表面贴片封装,极大地提高了印刷电路板上的组装密度;第二次是在上世纪 90 年代球型矩正封装的出现,它不但满足了市场高引脚的需求,而且大大地改善了半导体器件的性能;晶片级

2025-10-21 16:56:30 862

862

与封装企业的标配,其价值在于为大规模生产提供标准化的合格半成品,从源头提升直通率。

整形设备则更多服务于电子组装厂、测试实验室及维修中心。它能显著降低因引脚变形导致的物料报废和焊接不良,是提升整体组装效率

2025-10-21 09:40:14

波峰焊引脚的爬锡高度有标准么?另外引脚高度与焊盘的面积要如何搭配才比较合适?

2025-10-13 10:28:35

keil+Env怎么把很大的数组定义到SDRAM中?

RTT自带的SDRAM程序运行正常,能够申请里面的空间。

但是没有办法把很大的数组——ltdc_lcd_framebuf[1280][800]

定义到SDRAM中,一运行就出错,请问各位大佬怎么解决啊?

2025-10-11 16:10:01

问题:首先使用RT-Thread Studio创建了一个rtthread的标准工程,接着直接将正点原子例程LCD驱动的LCD文件夹和SDRAM文件夹移植到rtthread的标准工程,并做对应的适配

2025-09-25 08:16:11

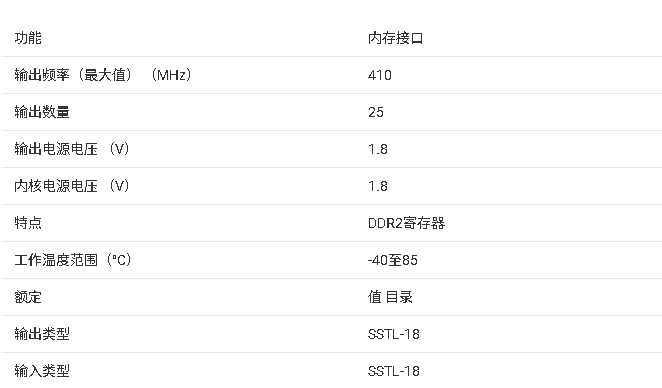

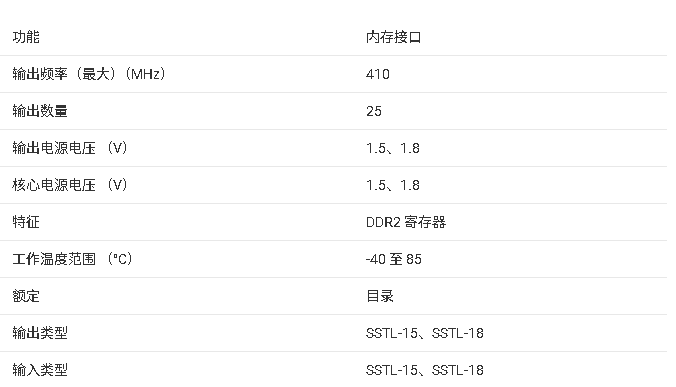

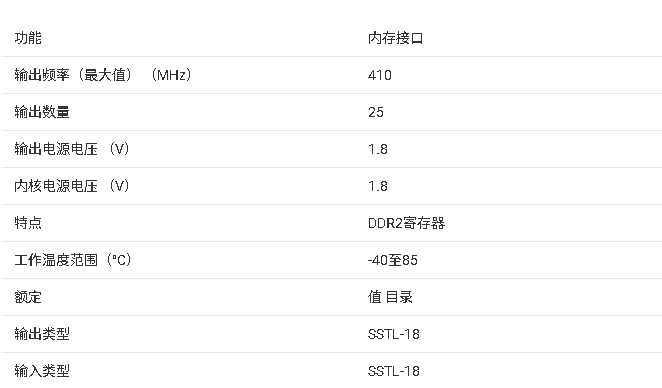

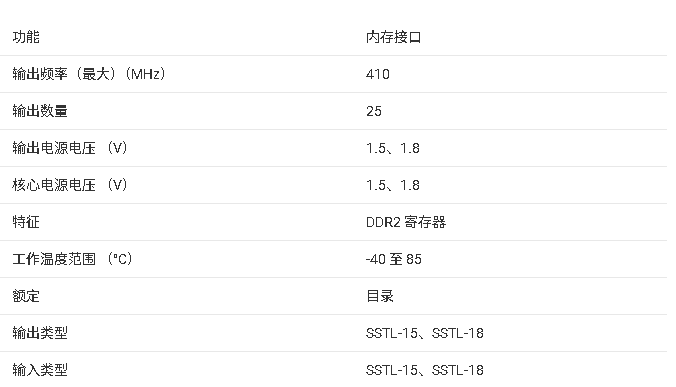

这款 25 位 1:1 或 14 位 1:2 可配置寄存器缓冲器设计用于 1.7V 至 1.9V VCC 工作。在 1:1引脚配置,每个DIMM只需要一个器件即可驱动9个SDRAM负载。在 1:2 引脚排列中 配置中,每个 DIMM 需要两个设备来驱动 18 个 SDRAM 负载。

2025-09-18 16:52:01 801

801

裸机以及RTT初始化是可以正常读写的,但在线程中,用了rt_thread_mdelay,SDRAM内的数据会被清理,数据丢失,也无法读写了,调试发现是rt_schedule导致的,请问这个该问题如何解决?

2025-09-18 07:53:44

这款 25 位 1:1 或 14 位 1:2 可配置寄存器缓冲器设计用于 1.425V 至 1.9V VCC 工作。在 1:1 引脚配置中,每个 DIMM 只需要一个器件即可驱动 9 个 SDRAM 负载。在 1:2 引脚配置中,每个 DIMM 需要两个器件来驱动 18 个 SDRAM 负载。

2025-09-17 14:19:28 577

577

挂载sramfs文件系统到外挂sdram ,挂载时返回错误码为-1。求大神指点。谢谢各位大佬。

2025-09-16 06:41:18

新品CoolSiCMOSFET1200V分立器件TO247-4引脚IMZA封装第二代CoolSiCMOSFETG21200V/53mΩ,TO247-4引脚IMZA封装,确保安装兼容性并可轻松替换现有

2025-09-08 17:06:34 931

931

AEC-Q100 标准)的引脚图、接线图、封装手册、中文资料、英文资料,20 MHz 至 3.0 GHz SPDT 开关(符合 AEC-Q100 标准)真值表,20 MHz 至 3.0 GHz SPDT 开关(符合 AEC-Q100 标准)管脚等资料,希望可以帮助到广大的电子工程师们。

2025-08-18 18:31:01

两个总线能不能同时使用,用了华邦的SDRAM发现SDRAM数据高概率读写错误,但是用ISSI的没问题。如果不对外部SRAM读写就正常。

2025-08-12 06:56:57

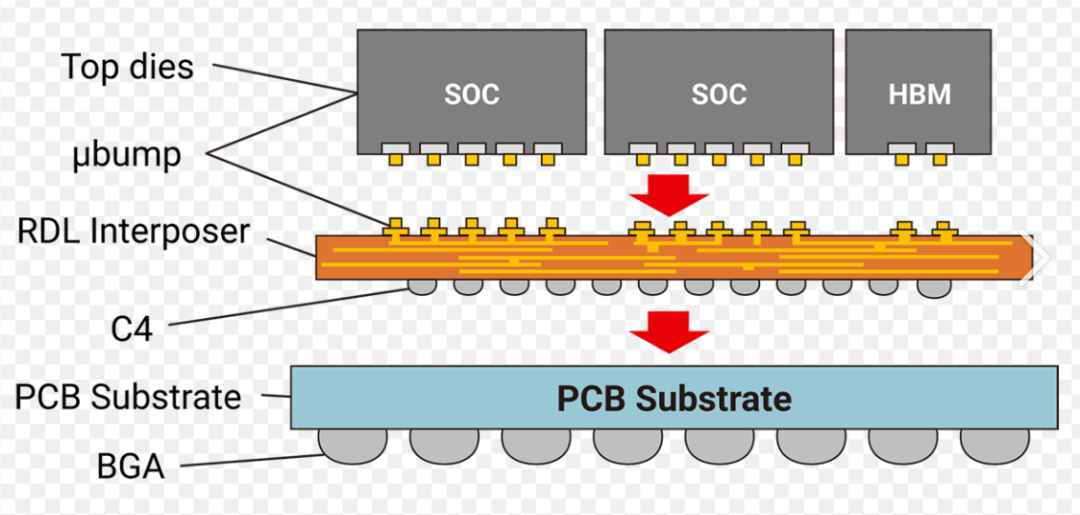

本文主要讲述什么是系统级封装技术。 从封装内部的互连方式来看,主要包含引线键合、倒装、硅通孔(TSV)、引线框架外引脚堆叠互连、封装基板与上层封装的凸点互连,以及扇出型封装和埋入式封装中的重布线等

2025-08-05 15:09:04 2135

2135

单片机封装是将芯片内部电路与外部引脚连接并包裹保护的结构,不仅影响单片机的安装方式、适用场景,还与电路设计的紧凑性、散热性能密切相关。不同封装类型各有特点,适配从简单电路到复杂系统的多样化需求

2025-08-01 13:47:34 1042

1042 。这场技术矛盾推动JEDEC、EIAJ等标准组织重构封装规范,催生出倒装芯片、BGA、WLP等创新封装范式。

2025-07-26 09:21:31 1667

1667

对引脚进行精细的调整。例如,上海桐尔科技推出的芯片引脚整形机,采用先进的机械设计和精密的控制技术,能够对多种封装形式的芯片引脚进行精确整形。设备配备了高精度的模具和定位系统,确保引脚在整形过程中能够

2025-07-19 11:07:49

一般我们开发MCU自带的SRAM,对一般应用来说,已经够用了,但是对于内存需求较高的场合,比如跑GUI或者算法等,自带的内存会就不够用,这个时候就要外扩SRAM或SDRAM。

2025-07-15 09:33:09 1781

1781

端口与外围设备域相关联

这个端口的引脚数量取决于所使用的封装。对于 QFN-48 封装,有 15 个引脚:P1.00-P1.14。

P1 上信号的最大速度为 8 MHz。

仅支持标准和高速驱动。

P1

2025-06-28 11:44:24

PCB标准封装库文件

2025-05-22 17:43:15 9

9 PMG1-S3 48 引脚封装的 IBIS 文件,其 D+/D- 为空。 IFX 能否修复 IBIS 文件?

2025-05-22 06:26:05

。4. 材料选择:封装材料的热导率对散热性能至关重要。高热导率的材料可以更有效地传导热量,从而降低模块内部温度。5. 封装结构:封装的结构设计,如引脚布局、散热孔等,也会影响散热性能。合理的结构设计可以

2025-05-19 10:02:47

微电子封装技术每15年左右更新迭代一次。1955年起,晶体管外形(TO)封装成为主流,主要用于封装晶体管和小规模集成电路,引脚数3 - 12个。1965年,双列直插式封装兴起,引脚数增至6 - 64

2025-05-13 10:10:44 2670

2670

业界普遍认为,倒装封装是传统封装和先进封装的分界点。

2025-05-13 10:01:59 1667

1667

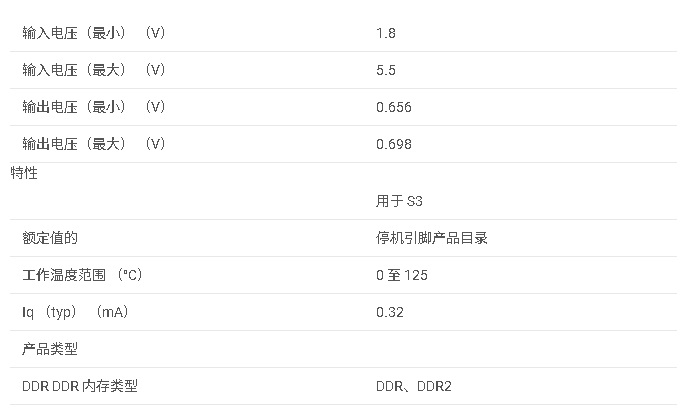

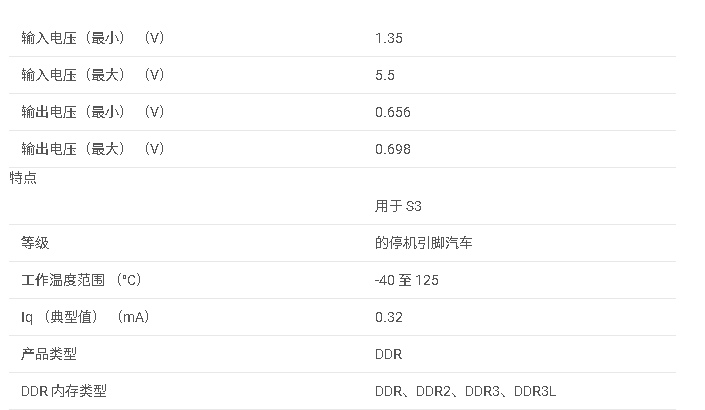

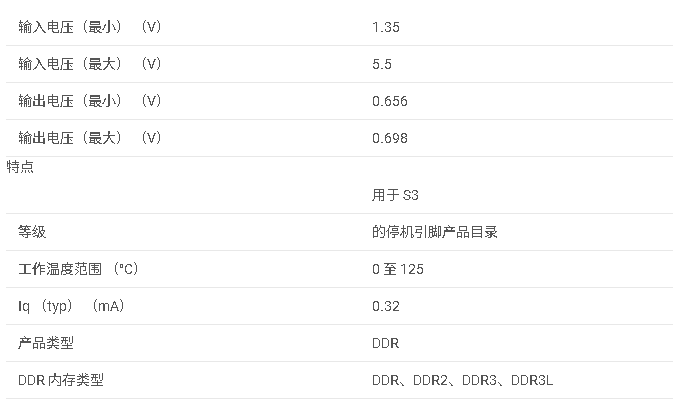

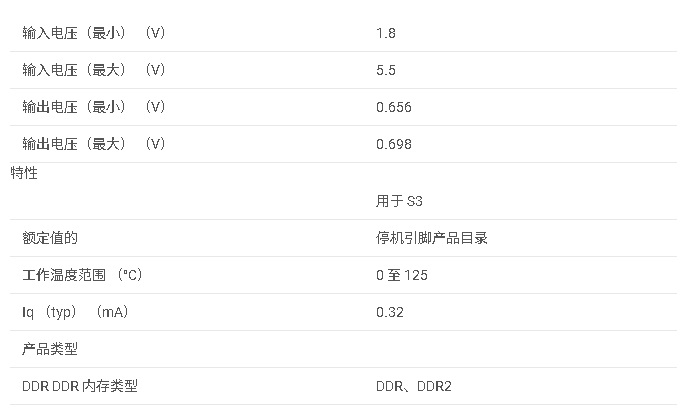

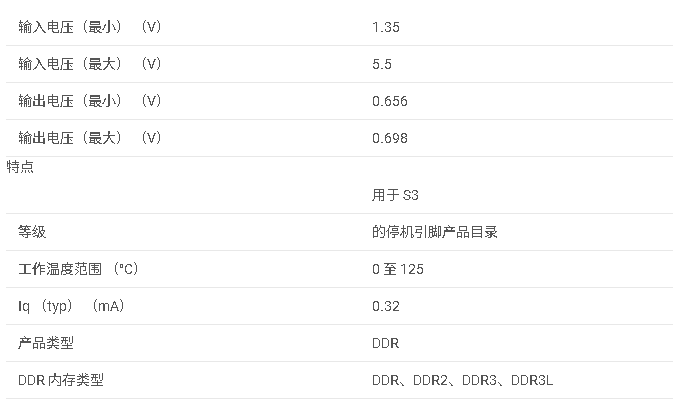

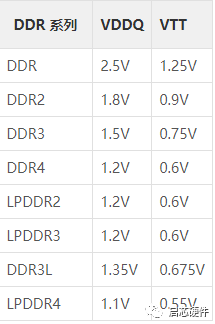

LP2996-N 和 LP2996A 线性稳压器旨在满足 JEDEC SSTL-2 标准 DDR-SDRAM 终止规范。该器件还支持 DDR2,而 LP2996A 支持 DDR3 和 DDR3L

2025-04-29 18:11:05 834

834

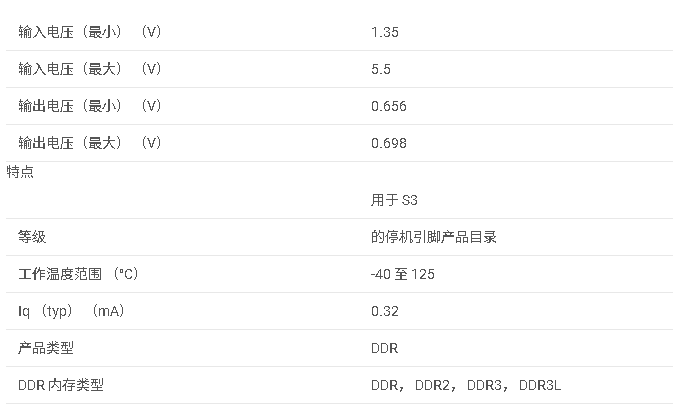

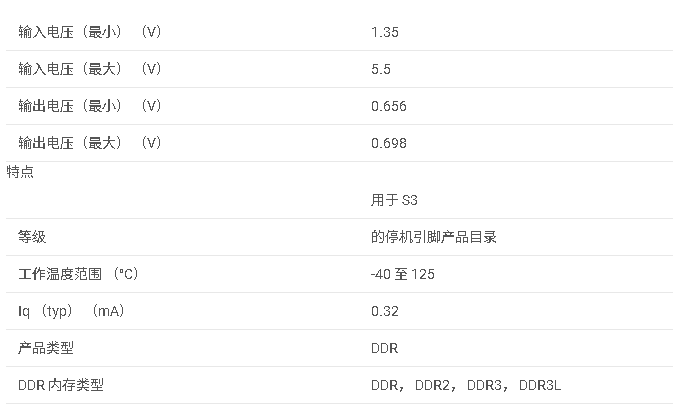

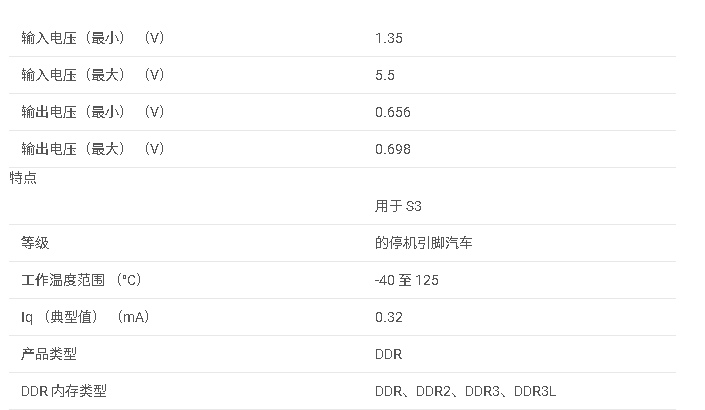

LP2998 线性稳压器旨在满足 JEDEC SSTL-2 和 JEDEC SSTL-18 标准 DDR-SDRAM 和 DDR2 内存终止的规范。该器件还支持 DDR3 和 DDR3L VTT

2025-04-29 11:34:59 810

810

LP2998 线性稳压器旨在满足 JEDEC SSTL-2 和 JEDEC SSTL-18 标准 DDR-SDRAM 和 DDR2 内存终止的规范。该器件还支持 DDR3 和 DDR3L VTT

2025-04-27 09:40:04 874

874

。 该器件包含一个高速运算放大器,可提供出色的负载响应 瞬 变。输出级可防止击穿,同时提供 1.5A 连续电流和 根据 DDR-SDRAM 端接的要求,应用中的瞬态峰值高达 3A。LP2996A 包含 V~意义~引脚提供出色的负载调节和 V~裁判~输出作为芯片组和 DIMM 的参考。

2025-04-26 15:02:50 746

746

:防止芯片受机械损伤、湿气、灰尘等外界环境影响; 电气连接:通过引脚或焊料凸点实现芯片与外部电路的稳定信号传输; 散热管理:优化封装材料与结构设计,提升芯片散热效率; 机械支撑:增强芯片结构强度以应

2025-04-16 14:33:34 2232

2232 The issue was i need to run data from external SDRAM memory instead of using internal RAM(DTCM). I

2025-04-14 12:21:59

Hi,大家好,我最近要设计hpm6e80 ivm1带sdram的电路,我参考了官方的评估板,发现hpm6e80 sdram引脚编号与外挂SDRAM芯片没有对应上(DQ引脚没有对应上),PPI子模

2025-04-12 18:37:09

源晶振的引脚朝下,以正视的角度,按照逆时针方向依次为2脚、3脚和4脚。 基于封装外形的引脚识别 : 正方的DIP-8封装 :打点的是1脚,各引脚功能通常为:1脚一般为NC(空脚,不连接任何功能,在某些设计中也可能有特殊用途,但常规

2025-04-10 17:20:54 1413

1413

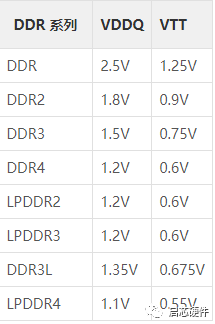

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代产品,相较于DDR2,DDR3有更高的运行性能与更低的电压。

2025-04-10 09:42:53 3930

3930

这个PCB库是嘉立创的标准集成库,使包含了一些常用元件和封装,使用本集成库进行设计的pcb在嘉立创进行投板时不用进行元件方向和位置的确认,节约成本和时间。

2025-04-09 13:59:06

使用的sdram型号是IS42S16160 32mb的是正常的但是更改到IS4216400 8mb的sdram后不能使用,请问1052支持吗?需要修改哪些配置,请大神讲解一下

2025-04-08 19:40:06

LPC553x MCU 具有硬件 I3C 外设。“PUR” 上拉电阻控制引脚是否仅提供 100 引脚封装?

如果是,是否有替代解决方案可用于 64 和 48 引脚封装来处理 SDA 线路上的外部引体向上?

2025-04-07 06:52:37

RT1176 与 DDR SDRAM 兼容吗?

2025-04-04 06:09:26

在封装设计中,原点是一个重要的参考点,通常根据封装类型被设置在关键位置,如几何中心或1脚焊盘等。例如,芯片封装的原点可能位于几何中心,而连接器封装的原点可能在引脚起始位置。Fanyskill 脚本为器件提供了灵活设置原点的功能,能够快速切换原点位置,以满足不同设计需求。

2025-03-31 09:37:09 1253

1253

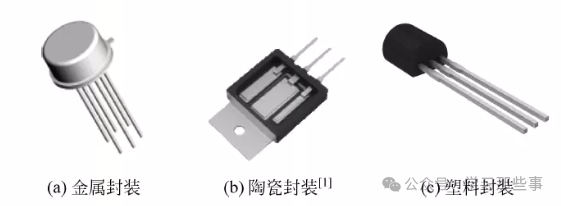

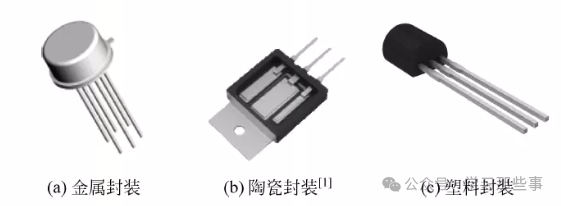

在集成电路(IC)产业中,封装是不可或缺的一环。它不仅保护着脆弱的芯片,还提供了与外部电路的连接接口。随着电子技术的不断发展,IC封装技术也在不断创新和进步。本文将详细探讨IC封装产线的分类,重点介绍金属封装、陶瓷封装以及先进封装等几种主要类型。

2025-03-26 12:59:58 2169

2169

STM32H750XBH6TR主芯片,当SDRAM频率设置为100MHz的时候,FMC_SDCLK和FMC_SDNWE延迟不符合标准,延迟偏大,造成100MHz SDRAM异常,这个延迟有办法调整

2025-03-14 15:15:19

SDRAM和NAND都使能了,都能正常工作,但是读取Nand数据然后存放到SDRAM中,发现SDRAM中的数据是错误的。但是将数据存到内部的IRAM中数据是正确的。请问NAND跟SDRAM不能同时访问么?该问题同时存在于STM32F767跟STM32H743中。请帮忙解答,谢谢!

2025-03-11 08:13:19

ma把怀疑是芯片引脚顺序问题,剪掉与带后缀smps后缀封装引脚有交叉的引脚重新焊会原来的板子电流变正常一点几ma,使用stlink可以读到芯片。

请问这是怎么回事哪里出错了,直接使用的立创的封装选型是stm32u575vit6

2025-03-11 06:29:17

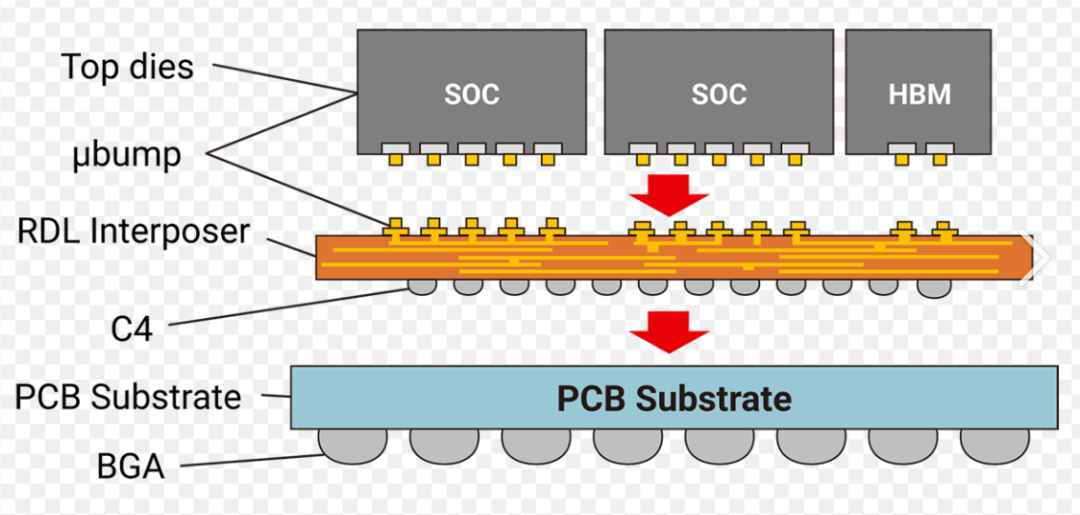

封装中的RDL(Redistribution Layer,重分布层)是集成电路封装设计中的一个重要层次,主要用于实现芯片内电气连接的重新分配,并且在封装中起到连接芯片和外部引脚之间的桥梁作用。RDL的设计和实现直接影响到封装的电气性能、可靠性和制造成本。

2025-03-04 17:08:35 4658

4658

由于现时高密度封装,如系统封装、倒装晶片、封装叠加等应用越来越多,而这些封装元件尺寸甚小。以倒装晶片为例,其焊球直径仅有0.05毫米, 焊球间距只有0.1毫米,对贴装设备的精度要求比标准元件更高。

2025-03-04 16:33:38 865

865

GPIO的控制等等。只有熟悉了这一个个的模块,才能让系统正常的转起来。 研究SDRAM也是一样,首先看看电源系统部分。 DDR的电源 主电源VDD和VDDQ,主电源的要求是VDDQ=VDD,VDDQ是给IO buffer供电的电源,VDD是给但是一般

2025-03-04 14:44:46 1115

1115

前言 SDRAM控制器里面包含5个主要的模块,分别是PLL模块,异步FIFO 写模块,异步FIFO读模块,SDRAM接口控制模块,SDRAM指令执行模块。 其中异步FIFO模块解读

2025-03-04 10:49:01 2301

2301

标准规格书的引脚图、接线图、封装手册、中文资料、英文资料,MHMF012L1U1-MINAS A6 系列 标准规格书真值表,MHMF012L1U1-MINAS A6 系列 标准规格书管脚等资料,希望可以帮助到广大的电子工程师们。

2025-02-27 19:21:33

为了加深读者对 FPGA 端控制架构的印象,在数据读取的控制部分,首先我们可以将SDRAM 想作是一个自来水厂,清水得先送至用户楼上的水塔中存放,在家里转开水龙头要用水时,才能及时供应,相同

2025-02-26 15:27:09 1813

1813

command.v文件对应图中SDRAM指令执行模块,它会从SDRAM接口控制模块接收指令,然后产生控制信号直接输出到SDRAM器件来完成所接收指令的动作。

2025-02-25 10:32:12 1034

1034

标准规格书的引脚图、接线图、封装手册、中文资料、英文资料,MHMF012L1S2-MINAS A6 系列 标准规格书真值表,MHMF012L1S2-MINAS A6 系列 标准规格书管脚等资料,希望可以帮助到广大的电子工程师们。

2025-02-24 19:24:04

标准规格书的引脚图、接线图、封装手册、中文资料、英文资料,MHMF012L1D3-MINAS A6 系列 标准规格书真值表,MHMF012L1D3-MINAS A6 系列 标准规格书管脚等资料,希望可以帮助到广大的电子工程师们。

2025-02-20 19:09:28

电子发烧友网站提供《SOD972-S1塑料、超小型和无引脚全密封封装.pdf》资料免费下载

2025-02-20 14:08:03 0

0 标准规格书的引脚图、接线图、封装手册、中文资料、英文资料,MGMF182L1D5-MINAS A6 系列 标准规格书真值表,MGMF182L1D5-MINAS A6 系列 标准规格书管脚等资料,希望可以帮助到广大的电子工程师们。

2025-02-18 19:04:39

谁有CS1262的封装库或者 DEMO 开发板的资料

2025-02-14 14:59:00

电子发烧友网站提供《SOD882L-1无引脚超小型塑料封装.pdf》资料免费下载

2025-02-13 14:15:09 0

0 标准规格书的引脚图、接线图、封装手册、中文资料、英文资料,MGMF182L1C5-MINAS A6 系列 标准规格书真值表,MGMF182L1C5-MINAS A6 系列 标准规格书管脚等资料,希望可以帮助到广大的电子工程师们。

2025-02-12 19:14:48

的封装形式有晶体管式的圆管壳封装、扁平封装、双列直插式封装及软封装等几种。 1、圆形结构集成电路 圆形结构集成电路形似晶体管,体积较大,外壳用金属封装,引脚有3、5、8、10多种。识别时将管底对准自己,从管键开始顺时针方

2025-02-11 14:21:22 1903

1903 按键KEY1触发写,将计数器产生的0到255的数据写到FIFO写模块里面,继而写到SDRAM 器件里面。

2025-02-07 09:33:41 1192

1192

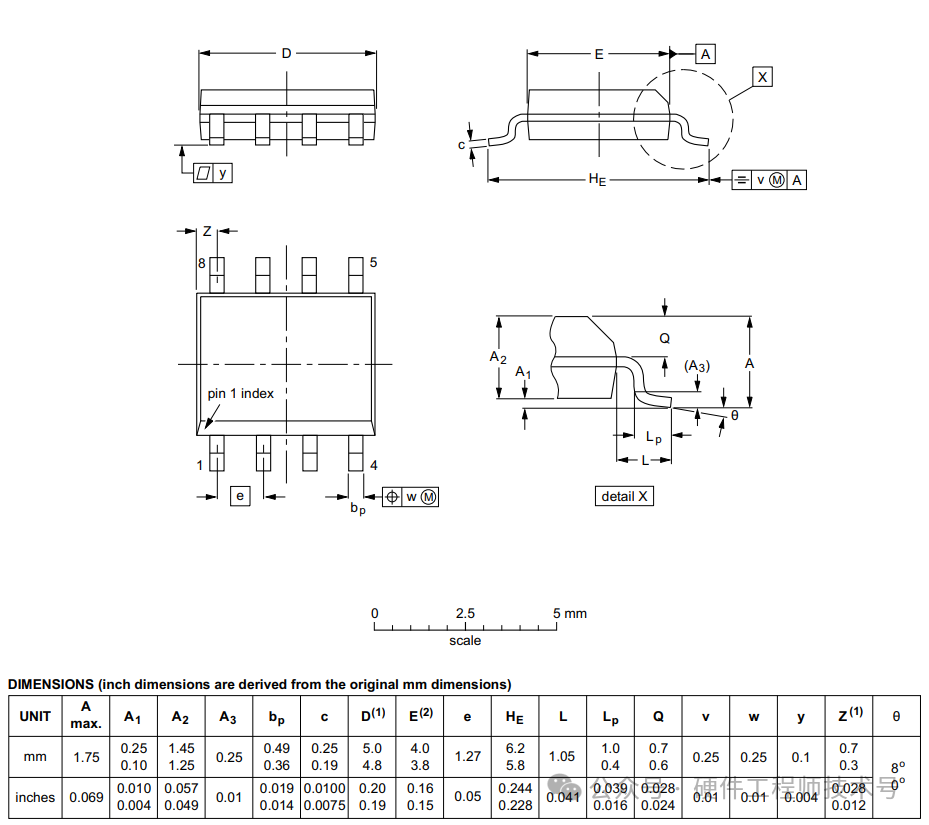

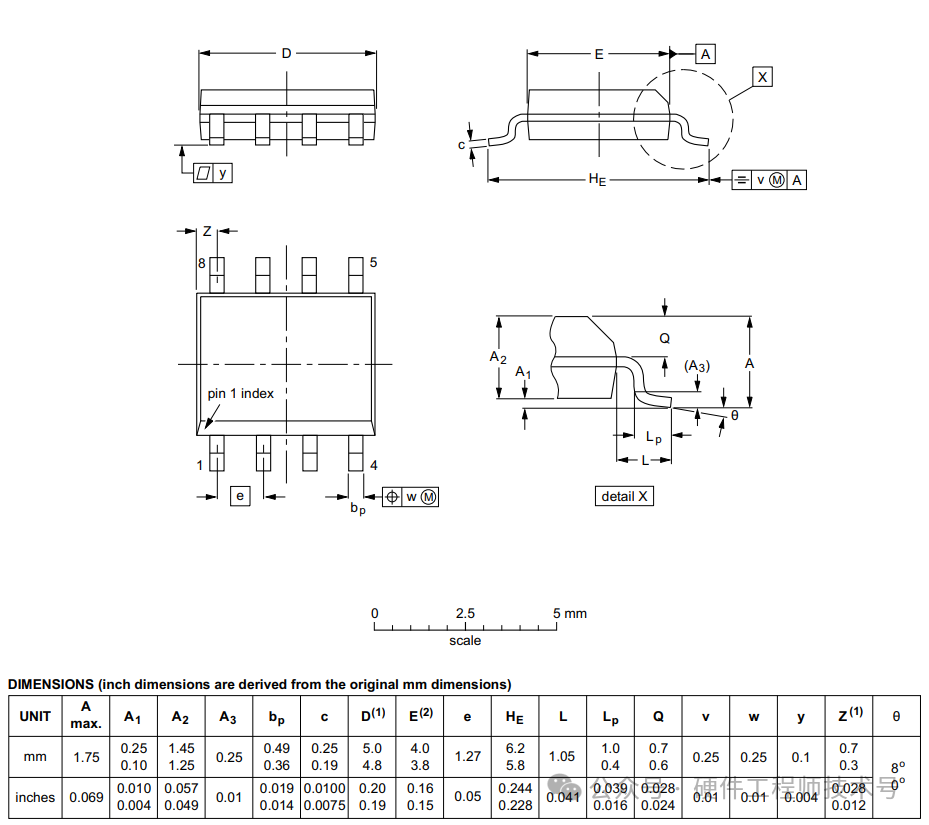

设计 SO-8(Small Outline-8)芯片的 PCB 封装需要遵循一定的规范和步骤。SO-8 是一种常见的表面贴装封装,具有 8 个引脚,引脚间距通常为 1.27mm(50 mil)。以下是设计 SO-8 封装的详细步骤和注意事项:

2025-02-06 15:24:26 5112

5112

射频电路中常见的元器件封装类型有以下几种: 表面贴装技术(SMT)封装 方型扁平式封装(QFP/PFP):引脚间距小、管脚细,适用于大规模或超大型集成电路,可降低寄生参数,适合高频应用,外形尺寸

2025-02-04 15:22:00 1351

1351 标准规格书的引脚图、接线图、封装手册、中文资料、英文资料,MDMF304A1DAM-MINAS A6 系列 标准规格书真值表,MDMF304A1DAM-MINAS A6 系列 标准规格书管脚等资料,希望可以帮助到广大的电子工程师们。

2025-01-17 19:07:21

标准规格书的引脚图、接线图、封装手册、中文资料、英文资料,MHMF092L1D3-MINAS A6 系列 标准规格书真值表,MHMF092L1D3-MINAS A6 系列 标准规格书管脚等资料,希望可以帮助到广大的电子工程师们。

2025-01-14 18:56:29

电子发烧友网站提供《EE-178:ADSP-TS101S TigerSHARC片上SDRAM控制器.pdf》资料免费下载

2025-01-14 15:00:14 0

0 描述这款小型低输入电流高增益光电耦合器为采用 5 引脚微型化尺寸的单通道器件,采用JEDEC 注册 SO-5 封装 (MO-155) 的表面贴装器件占用空间只有标准 DIP 封装的 1/4 ,引脚

2025-01-09 10:30:15

你好,我从TI官网上将ADC12D1800的bxl封装文件下载并传到ALTIUM 软件里了,但显示的原理图的引脚明显不够,在library框下还分为PART A,B,C三个部分,但只能看到一个原理图,不知道是什么原因(ps 芯片的pcb图是对的,引脚也够)

2025-01-09 08:13:45

标准规格书的引脚图、接线图、封装手册、中文资料、英文资料,MHMF092L1C3-MINAS A6 系列 标准规格书真值表,MHMF092L1C3-MINAS A6 系列 标准规格书管脚等资料,希望可以帮助到广大的电子工程师们。

2025-01-08 19:02:29

电子发烧友网站提供《EE-326: Blackfin处理器与SDRAM技术.pdf》资料免费下载

2025-01-07 14:38:14 0

0 电子发烧友网站提供《EE-286:SDRAM存储器与SHARC处理器的接口.pdf》资料免费下载

2025-01-06 15:47:01 0

0 电子发烧友网站提供《EE-127:ADSP-21065L片内SDRAM控制器.pdf》资料免费下载

2025-01-06 15:45:00 0

0 描述这款小尺寸、低输入电流、高增益光耦合器是一款单通道器件,采用五引脚微型封装。其SO-5 JEDEC注册(MO-155)封装外形不要求PCB上有“通孔”。这种封装约占标准双列直插式封装面积

2025-01-06 15:06:57

电子发烧友App

电子发烧友App

评论