文章来源:老虎说芯

原文作者:老虎说芯

本文介绍芯片封装中的RDL

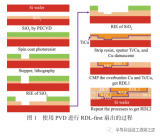

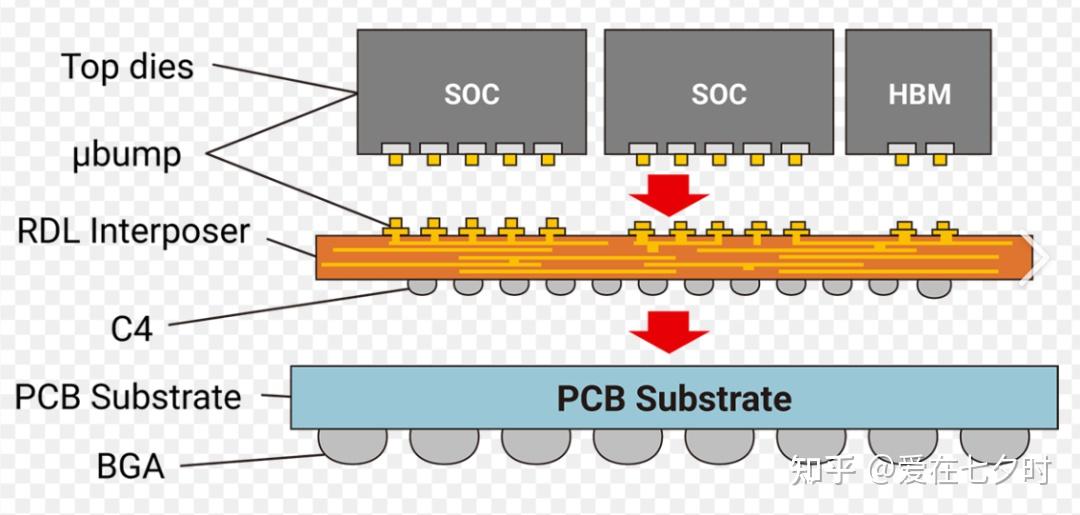

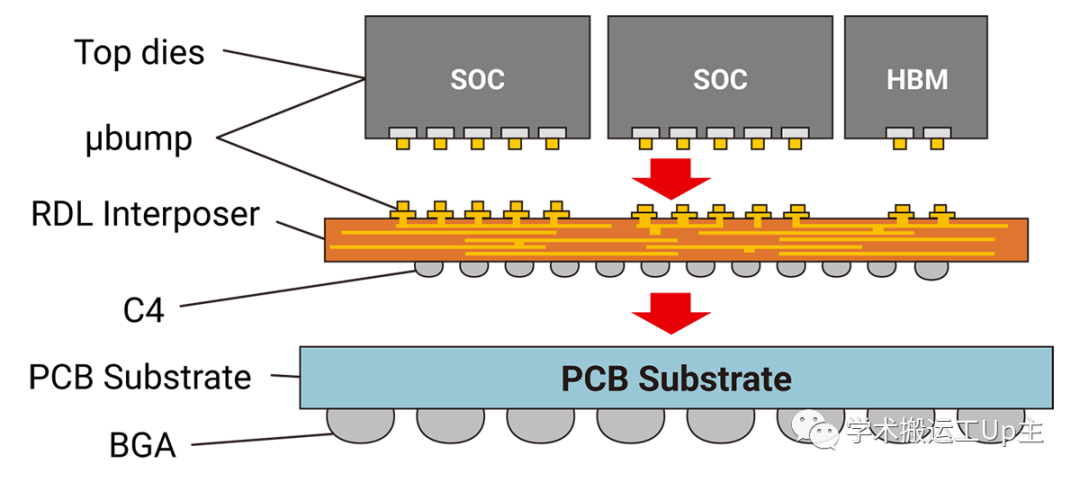

封装中的RDL(Redistribution Layer,重分布层)是集成电路封装设计中的一个重要层次,主要用于实现芯片内电气连接的重新分配,并且在封装中起到连接芯片和外部引脚之间的桥梁作用。RDL的设计和实现直接影响到封装的电气性能、可靠性和制造成本。

RDL的基本概念

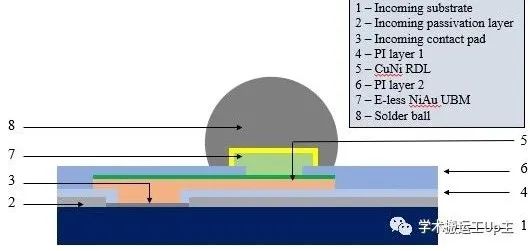

RDL是指在芯片的封装过程中,重新布置芯片表面上的信号线和电源线,以适应封装基板的布局需求。简单来说,它是芯片和封装基板之间的电路层,起到信号引导和分配的作用。通过RDL,芯片内部的引脚可以被重新分布到基板上的不同位置,提供与外部系统连接的功能。

2.RDL的设计目标

信号分配

RDL层的一个主要目标是将芯片的I/O(输入/输出)信号有效地分配到封装的不同区域。这样做可以优化信号传输路径,减少信号延迟和串扰。

电源分布

除了信号线的布置外,RDL还负责电源层的布置,确保芯片和封装基板之间的电流稳定传输,避免过高的电流密度导致过热或烧毁问题。

尺寸与性能平衡

通过优化RDL的布局,设计师可以在保持小封装尺寸的同时,满足高性能的要求。这对于高集成度的芯片尤为重要。

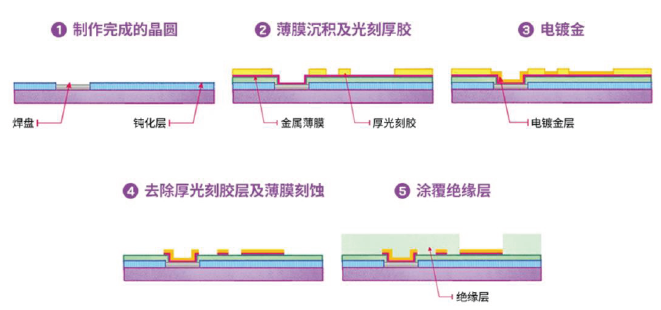

3.RDL的设计步骤

RDL的设计通常包括以下几个步骤:

信号分配分析:在设计RDL之前,首先要评估芯片内部的信号连接方式,分析每个I/O引脚的功能和其需要的连接路径。通过与芯片设计团队协作,确保信号线的最优布局。

布线设计:根据需求进行具体的RDL布线设计。RDL通常采用多层结构,通过不同层次的线路进行信号和电源的分配。设计时需要考虑布线路径、走线长度、宽度、间距等,以优化电气性能并避免信号干扰。

电气性能仿真:在设计完成后,通过仿真工具对RDL进行电气性能验证。这包括信号完整性(SI)和电源完整性(PI)分析,确保高频信号不会因布线不当产生衰减,电源分布稳定。

热力分析与优化:由于高功率芯片会产生大量热量,RDL的设计还需要进行热力学分析。通过模拟热流和散热路径,确保封装内的温度不会过高,避免对芯片性能产生负面影响。

制造与测试验证:RDL设计完成后,进入制造阶段。制造时需要根据设计图纸进行多层基板的制作,并通过各种测试方法验证RDL的电气连接性和机械稳定性,确保封装可以顺利通过后续的可靠性测试。

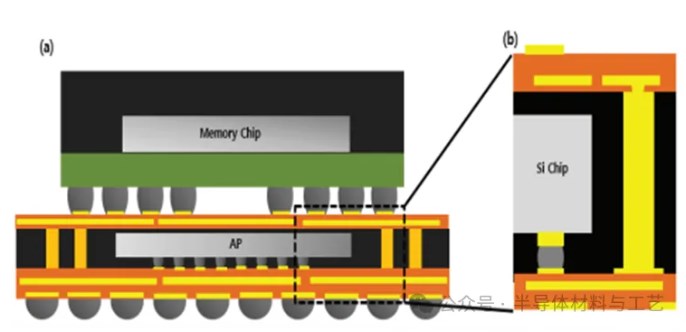

4.RDL与封装的关系

RDL层通常作为芯片封装的核心组成部分,与其他封装结构(如基板、外部引脚等)紧密配合。它不仅为芯片和封装基板之间的连接提供了通路,还决定了封装的电气性能、散热性能以及最终的封装尺寸。

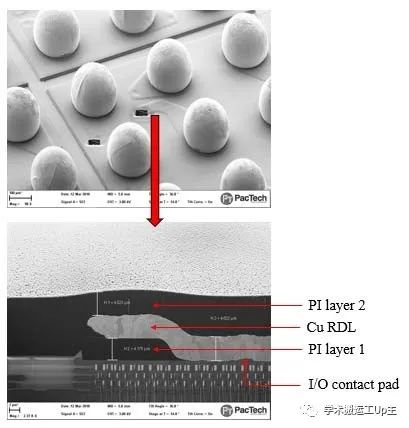

例如,像BGA(Ball Grid Array)或FCBGA(Flip Chip Ball Grid Array)封装中,RDL负责将芯片的I/O引脚重分布到基板上的焊球位置,确保信号从芯片传输到封装外部的电路板。

5.RDL的技术挑战

多层结构复杂性

RDL设计需要使用多层布线,这增加了设计的复杂性。设计师需要平衡信号传输质量、热性能和机械稳定性等因素。

信号完整性问题

随着芯片频率和集成度的增加,RDL中的信号完整性问题变得愈发严重。如何减少信号的损失、避免信号串扰、提高抗干扰能力是RDL设计的关键。

尺寸与成本控制

在保证性能的前提下,RDL的设计需要尽量减少封装的体积和制造成本。因此,如何通过优化布线来减小封装尺寸,并确保成本可控,是设计过程中必须考虑的因素。

6.RDL的应用与发展趋势

随着集成电路技术的不断进步,封装的要求也越来越高。RDL技术在高性能芯片封装中起着越来越重要的作用。尤其在像5G、AI、汽车电子等领域,对封装的要求更是不断提高。未来,RDL技术将朝着更高频、更小尺寸、更低成本的方向发展,同时加强与热管理、可靠性分析等其他封装领域的协同设计。

总结。RDL是集成电路封装中不可或缺的设计层,负责芯片与封装之间的电气连接与信号分配。它不仅影响封装的电气性能,还与封装的尺寸、热管理、成本等多个因素密切相关。随着技术的发展,RDL设计正变得越来越复杂,要求设计师在保证性能的同时,还需优化尺寸、成本,并解决信号完整性等技术挑战。

-

集成电路

+关注

关注

5446文章

12469浏览量

372691 -

芯片封装

+关注

关注

13文章

604浏览量

32084 -

封装设计

+关注

关注

2文章

48浏览量

12146

原文标题:芯片封装中的RDL

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

先进封装RDL-first工艺研究进展

新型WLCSP电路修正技术

集微连线:板级封装潜力无穷 RDL工艺勇挑大梁

Manz亚智科技RDL设备切入五家大厂

Manz亚智科技RDL制程打造CoPoS板级封装路线, 满足FOPLP/TGV应用于下一代AI需求

Manz亚智科技RDL制程打造CoPoS板级封装路线,满足FOPLP/TGV应用于下一代AI需求

半导体先进封装“重布线层(RDL)”工艺技术的详解;

芯片封装中的RDL(重分布层)技术

芯片封装中的RDL(重分布层)技术

评论