全球电子设计创新企业Cadence设计系统公司日前宣布其与TSMC在3D IC设计基础架构开发方面的合作。

2012-06-11 09:47:43 1071

1071 楷登电子今日正式发布Cadence® Virtuoso®定制 IC设计平台的技术升级和扩展,进一步提高电子系统和 IC设计的生产力。新技术涉及Virtuoso 系列几乎所有产品,旨在为系统工程师提供更稳健的设计环境和生态系统,助其实现并分析复杂芯片、封装、电路板和系统。

2018-04-11 16:40:16 9290

9290 Cadence Integrity 3D-IC 平台是业界首个全面的整体 3D-IC 设计规划、实现和分析平台,以全系统的视角,对芯片的性能、功耗和面积 (PPA) 进行系统驱动的优化,并对 3D-IC 应用的中介层、封装和印刷电路板进行协同设计。

2022-05-23 17:13:53 4218

4218 这是一个业界用于打造差异化定制芯片的领先平台,可借助生成式 AI 技术显著提升设计生产力; Virtuoso Studio 与 Cadence 最前沿的技术和最新的底层架构集成,助力设计工

2023-04-20 15:52:13 508

508

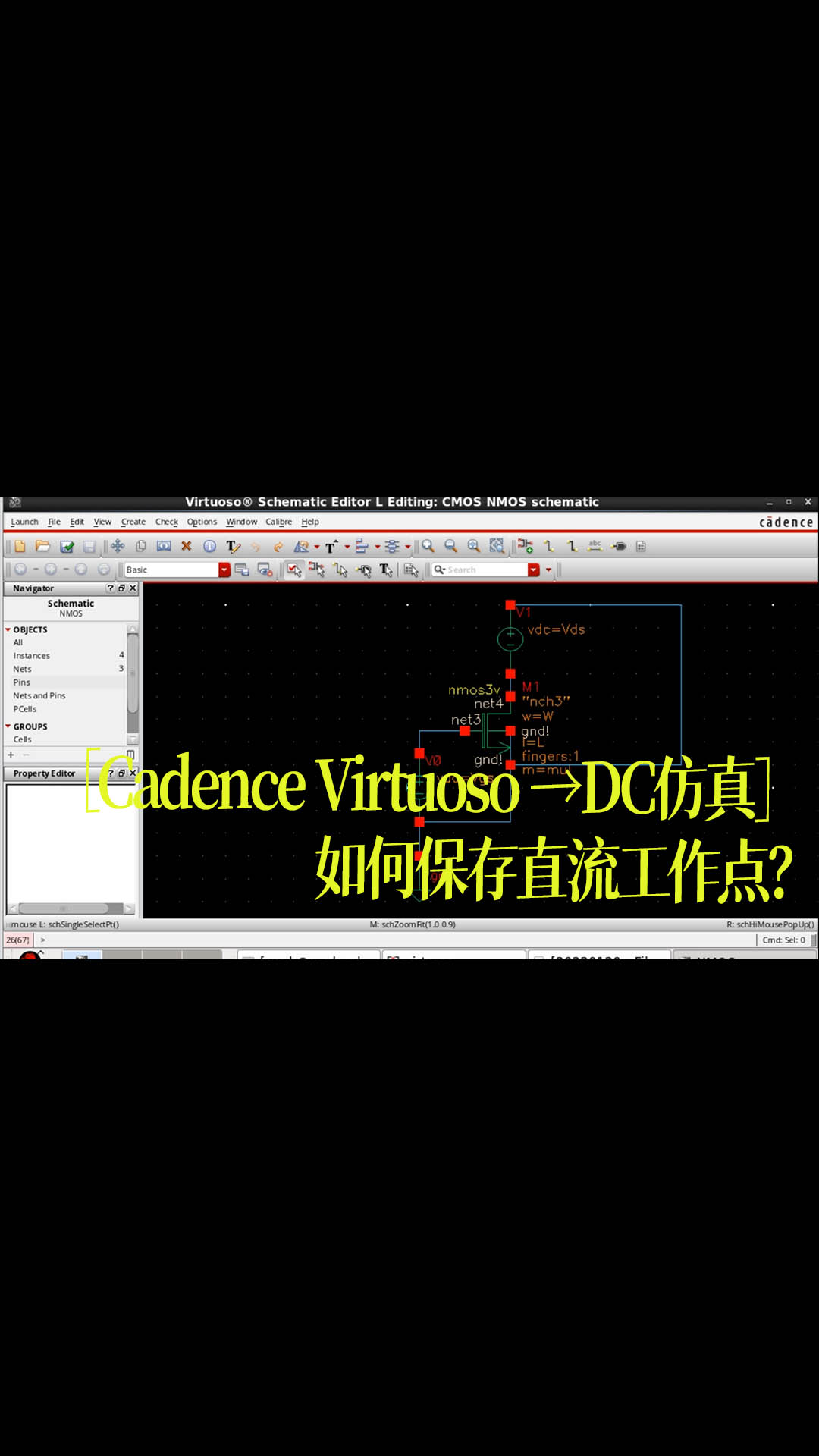

各位大佬好,我正在学习IC设计,对于Cadence Virtuoso这个软件有一些入门级的小问题:我从AnaglogLib拷贝NMOS管和PMOS管到自己的library下面,打开他们的CDF参数看

2017-10-16 00:26:33

Cadence设计系统公司发布了Cadence Allegro系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和技术增强。改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2018-11-23 17:02:55

业界首个用于多芯片设计和高级封装的综合性的 3D-IC 设计平台,其主要亮点有: Integrity 3D-IC 将设计规划、实施和系统分析集成在一个统一的座舱中设计人员可以通过集成的散热、功率消耗

2021-10-14 11:19:57

:“我们选择Cadence作为我们RFSiP技术的合作伙伴,因为Cadence有相应的技术和能力,能够和我们共同制定一套在FREESCALE能被广泛采用的解决方案,从而显著提升我们的RFSiP技术

2008-06-27 10:24:12

Cadence设计系统公司发布Cadence®Allegro®系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和技术增强.改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2018-08-28 15:28:45

Cadence设计系统公司发布Cadence?Allegro?系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和技术增强.改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2008-06-19 09:36:24

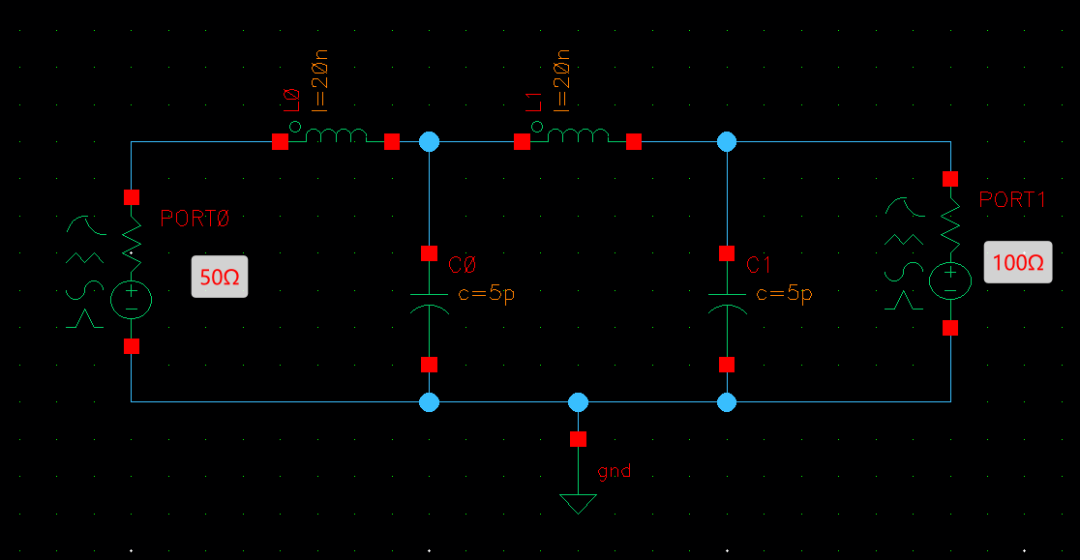

电路工作到了后期需要汇报或者写文章需要设计原图 ,这里整理一下Cadence设计原理图常用导出方案。 前期工具用的好,后期处理没烦恼,Cadence自带工具其实很强大,只是你没尝试用。 仿真环境:虚拟机Linux下Cadence617 原理图绘制工具:virtuoso

2021-01-15 07:48:05

cadence virtuoso教程 1990-2006 Cadence Design Systems, Inc. All rights reserved.Printed

2012-08-10 18:37:59

由于skill 语言提供编程接口甚至与<br/>C 语言的接口所以可以以Cadence 为平台进行扩展用户还可以开发自己的<br/>

2008-07-12 23:11:21

cadence讲义_IC设计_清华微电子所

2012-08-12 17:30:13

or subcircuit, `nmos_6p0'. Either include the。。。。仿真前需要设置model libraries,这个怎么设置啊。我用的是virtuoso 6.1.7

2018-07-19 20:16:30

大家好,本人刚入ic行,这几天用virtuoso画版图在LVS检测过程中出现了如图所示的报错,有没有哪位大神知道怎么改,麻烦赐教,很急谢谢!

2017-07-25 17:17:22

自动白平衡的FPGA实现采用FPGA对自动白平衡进行运算有什么优点?

2021-04-13 06:20:46

加密芯片的特点,区分位两大方案,即单片机与加密IC固定算法认证的模式和单片机中的部分代码移植到加密IC中的模式。从目前的加密效果看,采用智能卡平台的加密芯片,使用客户自定义算法移植的加密模式,被证明

2011-04-08 14:31:03

LED实现白光有哪几种方式?采用荧光粉来制作彩色LED有什么优点?

2021-06-01 06:18:35

组件架构的一个优点就是应用可以随时间的流逝而发展进化。除此之外,使用组件还有一些可以使对以有应用的升级更加 方便和灵活的优点,如应用的定制,组件库以及分布式组件等。

2020-03-11 09:01:29

本帖仅致那些跟我一样奋斗在安装路上的小白们,过程很辛苦,所以写下来,让之后安装的人有个参考,节省点时间为了安装cadence ic5141 ,可谓是呕心沥血,历经万难前后十天,除了每天睡觉,重要的课

2013-05-28 23:43:37

的迭代方法大大提升。 完全集成于Cadence Virtuoso® 平台,提供统一的设计流程,提升了设计人员在模拟和定制模块进行EMIR签收的工作效率。 利用了Cadence Quantus QRC寄生

2018-09-30 16:11:32

深圳WINCE专业平台开发团队,我们致力提供WINCE平台的硬件定制,内核驱动定制一条龙服务:********三星平台************ARM9(S3C2440,S3C2416,S3C2451

2010-04-12 09:46:25

请问给位大佬,我这有一款1621(lcd驱动)的原理,我需要仿真芯片功能,对于ic需要的读写时序怎么提供?我实在cadence virtuoso上操作。谢谢

2018-07-16 13:51:50

二极管的主要参数有哪些?单相电风扇采用电子式调速器有何优点?

2021-09-27 08:39:55

基于Cadence virtuoso与Mentor Calibre的CMOS模拟集成电路版图该如何去设计?怎样去验证一种基于Cadence virtuoso与Mentor Calibre的CMOS模拟集成电路版图?

2021-06-22 06:12:49

基于Cadence的IC设计

2012-08-16 16:51:16

的设计平台。在综合比较后,本文选定了CadenceVirtuoso全定制IC设计工具。VirtUOSO是Cadence公司推出的用于模拟/数字混合电路仿真和射频电路仿真的专业软件。基于此平台

2018-11-26 10:56:11

您是否正在使用Cadence Virtuoso进行功率放大器设计?您想运行信封跟踪模拟吗?包络跟踪是一种响应于调制的RF输入信号的功率电平来调整功率放大器的偏置电压以获得更高效率的方法。已在

2019-02-21 16:18:37

布局结构,最后根据芯片内各个信号的关系来进行电路布线的操作。以上的操作都可以在Cadence的IC 5.1集成设计环境下的Virtuoso中完成,当完成布局布线后全定制Asic的版图基本就确定了,然后

2013-01-07 17:10:35

打开virtuoso的一些功能一、Connectivity --> Mark net 如图所示,此功能就是可以选中相关连的层(通常大家会采用skill 来达到这一功能),这里讲的是调用tech

2018-11-26 16:20:19

招兼职Cadence,IC设计等各类相关讲师,要求有一定项目经历,表达能力强,待遇高,可周末,有意者请与我联系。地点北京, QQ:1489302364,邮件:hailang869@163.com,罗先生

2012-03-30 10:44:10

ACS712是什么?线性电流传感器IC ACS712的特色和优点有哪些?

2021-09-30 09:10:50

Cadence Virtuoso与PCB设计软件,如Altium Designer等; 4.对天线、基带均有一定了解,具备系统级分析能力,能就实际产品性能问题优化射频电路的设计,提供解决方案; 5.熟练掌握

2015-07-03 18:01:37

本文介绍了一种MEMS 器件设计,及在Cadence Virtuoso 设计环境与集成电子产品一起仿真的新方法。采用德州仪器的数字微反射镜器件(DMD)的例子,我们展示新的MEMS - IC 设计方法如何可

2010-09-23 11:42:15 0

0 Cadence Allegro SiP and IC Packaging 16.3版推出

Cadence设计系统公司宣布,利用最新的系统封装(SiP)和IC封装软件,封装设计者将在芯片封装协同设计过程中和整个半导体设计链中

2009-11-04 08:52:51 1826

1826 芯邦采用Cadence Incisive Xtreme III系统提升SoC验证实效

全球电子设计创新领先企业Cadence设计系统公司今天宣布,位于中国深圳的、无晶圆厂集成电路设计领先企业芯邦科

2010-03-02 10:32:47 573

573 意法推出新评估平台Cadence OrCAD PSpice

意法半导体宣布成功开发一个新的评估平台,客户可以仿真意法半导体先进的模拟和功率芯片。Cadence® OrCAD®, PSpice®是一项稳健

2010-04-13 10:53:50 970

970 电子设计创新企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,中国科学院计算技术研究所(简称计算所)采用了Cadence? Incisive?Xtreme Ⅲ? 系统,来加速其下一代6400万门以上龙芯3号高级多

2011-05-27 10:49:34 646

646 Giantec最近采用Cadence软件设计并成功流片了一款用于低功耗微控制器的存储器产品,这款低功耗微控制器应用于智能卡、智能电表和消费电子产品。

2011-09-22 18:08:05 896

896 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),宣布Giantec Semiconductor Corp.已采用Cadence® Virtuoso®统一定制/模拟(IC6.1)以及Encounter®统一数字流程生产其混合信号芯片。

2011-09-27 11:06:26 1483

1483 本章是Cadence IC 5.1.41 是设计 的简明入门教程,目的是让读者在刚接触该软件的时候对它的基本功能有一个总体的了解。本章主要内容如下:[1] 启动Cadence IC 前的准备;[2]Command Interpret

2011-12-02 16:56:58 158

158 全球EDA领导厂商SpringSoft今天宣布,现即提供Laker3™定制IC设计平台与模拟原型(Analog Prototyping)工具。

2012-04-25 14:46:43 2346

2346

Cadence 设计系统公司日前宣布,汽车零部件生产商Denso公司在改用了Cadence定制/模拟与数字流程之后,在低功耗混合信号IC设计方面实现了质量与效率的大幅提升。将Cadence Encounter RTL-to-G

2012-09-04 09:31:59 811

811 全球电子设计创新领先企业Cadence设计系统公司日前宣布TSMC已选择Cadence解决方案作为其20纳米的设计架构。Cadence解决方案包括Virtuoso定制/模拟以及Encounter RTL-to-Signoff平台。

2012-10-22 16:48:03 909

909 Cadence教程:基于Cadence的IC设计

2013-04-07 15:46:14 0

0 为专注于解决先进节点设计的日益复杂性,全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布,台积电已与Cadence在Virtuoso定制和模拟设计平台扩大合作以设计和验证其尖端IP。

2013-07-10 13:07:23 842

842 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布推出用于实现电学感知设计的Virtuoso®版图套件,它是一种开创性的定制设计方法,能提高设计团队的设计生产力和定制IC的电路性能。

2013-07-15 17:13:14 2080

2080 基于Wide I/O接口的3D堆叠,在逻辑搭载存储器设计上进行了验证 ,可实现多块模的整合。它将台积电的3D堆叠技术和Cadence®3D-IC解决方案相结合,包括了集成的设计工具、灵活的实现平台,以及最终的时序物理签收和电流/热分析。

2013-09-26 09:49:20 1346

1346 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,海思半导体(HiSilicon Semi)进一步扩大采用Cadence® Palladium® XP 验证运算平台作为其仿真方案,运用于移动和数字媒体System-on-Chip (SoC) 与 ASIC开发。

2014-05-13 16:19:03 2137

2137 美国加州圣何塞,2014年9月30日 ─ 全球知名的电子设计创新领导者Cadence设计系统公司(NASDAQ: CDNS)今日宣布其丰富的IP组合与数字和定制/模拟设计工具可支持台积电全新的超低功耗(ULP)技术平台。

2014-10-08 19:24:35 907

907 基于cadence IC5141差分放大器的设计spectre仿真与layout绘制1

2016-02-19 16:43:05 175

175 IC design 集成电路的设计流程以及cadence的简介,使用方法和入门须知。

2016-03-14 14:11:33 25

25 4月15日,中国上海—楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日宣布Cadence® Virtuoso® 版图依赖效应(Layout-Dependent Effects

2016-04-15 10:09:07 1939

1939 2017年1月5日,中国上海 —— 楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日与国家集成电路设计北京产业化基地—中关村芯园(北京)有限公司联合宣布,双方将签订平台合作协议,将Cadence最前沿的设计工具平台和创新技术注入到中关村芯园的集成电路公共服务平台之中。

2017-01-05 15:06:07 1252

1252 2017年4月18日,中国上海 – 楷登电子(美国Cadence公司,NASDAQ: CDNS)今日正式发布针对7nm工艺的全新Virtuoso® 先进工艺节点平台。通过与采用7nm FinFET

2017-04-18 11:09:49 1165

1165 (Virtuoso系统设计平台),结合Cadence Virtuoso平台与Allegro® 及Sigrity™技术,打造一个正式的、优化的自动协同设计与验证流程。

2017-06-13 14:26:28 2937

2937 电路、对基带低频大信号有高线性度要求的模块、发射端大电流的PA 模块、锁相环频率综合器中的数字块,以及非线性特性的VCO等各具特点的电路。众多的电路单元及其丰富的特点必然要求在这种系统的设计过程中有一个功能丰富且强大的设计平台。在综合比较后,本文选定了Cadence Virtuoso 全定制IC 设计工具。

2018-06-06 09:37:00 10797

10797

选项、Spectre电路模拟器、Voltus-Fi客制电源完整性解决方案、Pegasus验证系统以及VirtuosoR客制IC设计平台,其中包括Virtuoso布局套装EXL、Virtuoso原理图编辑器及Virtuoso ADE产品套装。

2019-05-07 16:29:20 2491

2491 加利福尼亚州圣何塞 , Dec。 1,2015 /PRNewswire/- 凯德斯设计系统公司(纳斯达克股票代码:CDNS)今天宣布推出新的Virtuoso®Advanced-Node平台,该平台

2019-08-08 15:40:13 982

982 cadence 公司 IC5141 工具主要包括集成平台 design frame work II、原理图编辑工具 virtuoso schematic editor、仿真工具、版图编辑工具

2020-07-21 08:00:00 3

3 安装Cadence IC617+MMSIM151+Calibre的IC设计环境

2021-04-07 09:08:10 9

9 Cadence 3D-IC Integrity 平台在统一的环境中提供 3D 芯片和封装规划、实现和系统分析。

2021-10-28 14:53:35 2114

2114 这篇博客记录一下virtuoso中进行CMOS反相器和静态寄存器的电路设计以及功能仿真,适合入门。还做了版图设计,但是自己对原理不是不清楚,在此就不记录了。virtuoso电路设计环境基本教学

2021-11-07 10:21:01 36

36 创建逻辑内存器件的 3D 堆叠配置,优化 3D 堆叠设计的 PPA 结果。 客户可以放心采用 Cadence Integrity 3D-IC 平台和 Samsung Foundry 的多 Die 实现

2021-11-19 11:02:24 3347

3347 与 Cadence 资深技术专家,涵盖最完整的先进技术交流平台,从封装和板级设计,系统分析方案到定制/模拟设计,覆盖设计全流程的技术分享。您也将有机会和开发 Cadence 工具的技术专家们面对面的直接沟通。

2021-12-09 09:55:55 1599

1599 中国上海,2022年4月21日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布推出 Cadence® Fidelity™ CFD 软件平台,为多物理场仿真的性能和准确度开创新时代。

2022-04-21 11:36:50 1955

1955 基于Cadence的IC设计

2022-05-31 17:11:24 0

0 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,其数字和定制 / 模拟设计流程已获得 TSMC N3E 和 N4P 工艺认证,支持最新的设计规则手册(DRM)。

2022-06-17 17:33:05 4800

4800 设计。得益于两家企业的持续合作,使用 Cadence Integrity 3D-IC 平台的参考流程现已启用,以推进 Samsung Foundry 的 3D-IC 设计方法。使用 Cadence 平台

2022-10-25 11:05:04 621

621 联华电子(NYSE:UMC;TWSE:2303)与楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日共同宣布,采用 Integrity 3D-IC 平台的 Cadence 3D-IC 参考工作流程已通过联电的芯片堆栈技术认证,将进一步缩短产品上市时间。

2023-02-03 11:02:23 1417

1417 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,瑞萨电子(Renesas Electronics)已采用全新的人工智能(AI)驱动的 Cadence Verisium 验证

2023-03-15 09:07:00 539

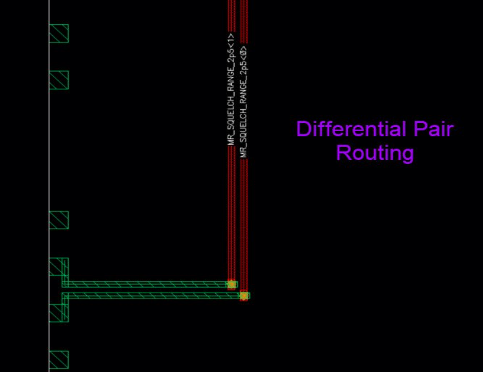

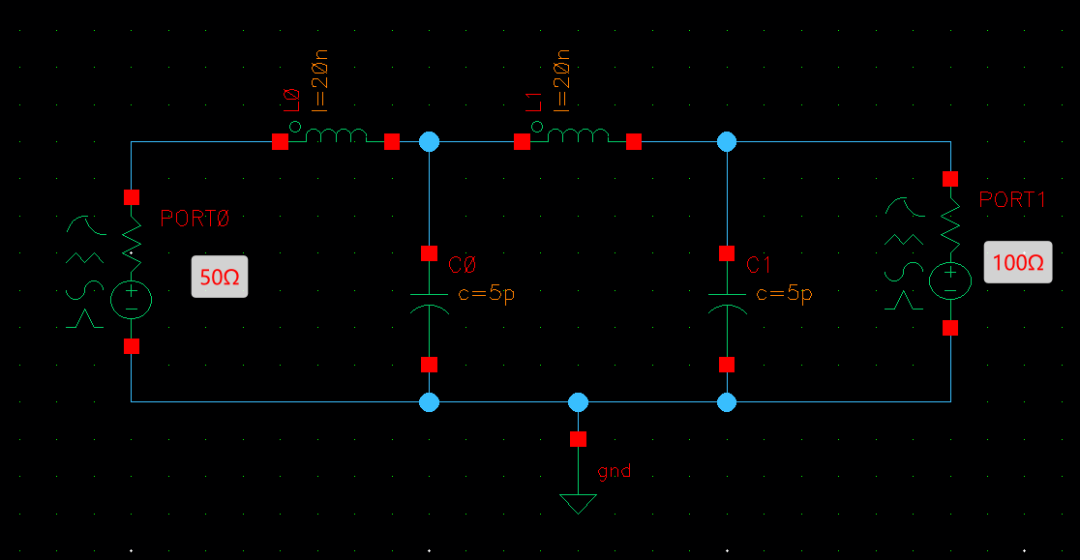

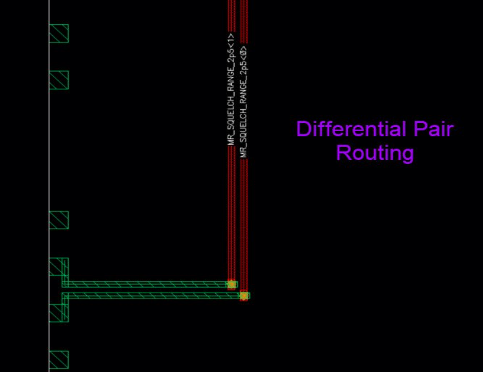

539 交互式路由允许您在自动路由之前完成关键网络,并在自动路由后完成未布线的不完整网络。Virtuoso 交互式和辅助路由功能允许您在 Virtuoso 环境中以交互方式路由连接,以满足关键的设计约束和规则。在所有工艺节点上启用交互式和自动布线功能,包括最先进的工艺技术。

2023-04-20 10:58:23 2071

2071

,包括最新的 N3E 和 N2 工艺技术。这一新的生成式设计迁移流程由 Cadence 和台积电共同开发,旨在实现定制和模拟 IC 设计在台积电工艺技术之间的自动迁移。与人工迁移相比,已使用该流程的客户成功地将迁移时间缩短了 2.5 倍。

2023-05-06 15:02:15 801

801 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Integrity 3D-IC 平台的新设计流程,以支持 TSMC 3Dblox 标准。TSMC

2023-05-09 09:42:09 615

615 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 数字和定制/模拟设计流程已通过 TSMC N3E 和 N2 先进工艺的设计规则手册(DRM)认证。两家公司还发

2023-05-09 10:09:23 708

708 了新一代定制设计平台 Cadence Virtuoso Studio ,该平台采用全新的底层架构,以独特的方法来管理设计流程,可将当今大型设计的设计同步吞吐量提升 3 倍,是面临大型复杂项目和有短时间

2023-06-13 12:15:02 557

557

● Samsung Foundry 有众多 PDK 系列,可搭配 Virtuoso Studio 用于简化模拟、定制和射频设计,最高支持 SF 2nm 技术 ● Virtuoso Studio

2023-06-30 10:08:30 681

681 内容提要 1 轻松实现节点到节点的设计和 layout 迁移 2 将定制/模拟设计迁移速度提升 2 倍 3 Cadence Virtuoso Studio 针对所有 Samsung Foundry

2023-07-04 10:10:01 471

471 已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ● Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio

2023-07-05 10:10:01 322

322 已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ●Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio,已针对

2023-07-05 10:12:14 381

381 平台支持 Samsung 新的 3D CODE 标准,助力设计人员创建多种先进的封装技术。 ❖ Cadence 和 Samsung 的技术为客户提供全面、定制化的解决方案。适用于能够缩短 3D-IC

2023-07-06 10:05:04 329

329 了新一代定制设计平台 Cadence Virtuoso Studio ,该平台采用全新的底层架构,以独特的方法来管理设计流程,可将当今大型设计的设计同步吞吐量提升 3 倍,是面临大型复杂项目和有短时间

2023-07-11 12:15:02 241

241

了新一代定制设计平台 Cadence Virtuoso Studio ,该平台采用全新的底层架构,以独特的方法来管理设计流程,可将当今大型设计的设计同步吞吐量提升 3 倍,是面临大型复杂项目和有短时间

2023-09-01 12:20:01 413

413

Cadence Virtuoso定制设计平台的一套全面的集成电流(IC)设计系统,能够在多个工艺节点上加速定制IC的精确芯片设计,其定制设计平台为模拟、射频及混合信号IC提供了极其方便、快捷而精确的设计方式。

2023-09-11 15:14:16 3199

3199

本篇文章将讲述如何在Cadence IC中使用ADE GXL对电路进行优化设计。

2023-09-11 16:07:01 1388

1388

● AI 驱动的 Cadence Virtuoso Studio 助力 IC 设计在 TSMC 的制程技术之间实现迁移时自动优化电路 ● 新的生成式设计技术可将设计迁移时间缩短

2023-09-27 10:10:04 301

301 和移动 IC 中国上海,2023 年 10 月 10 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布其数字和定制/模拟流程已通

2023-10-10 16:05:04 270

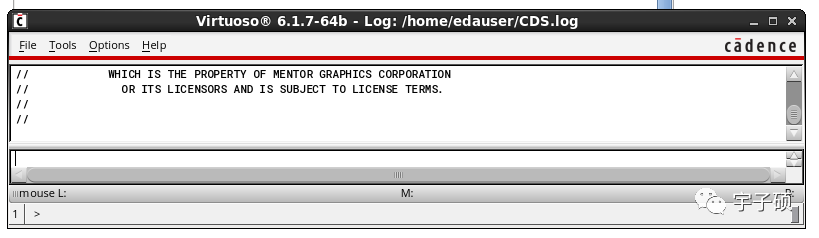

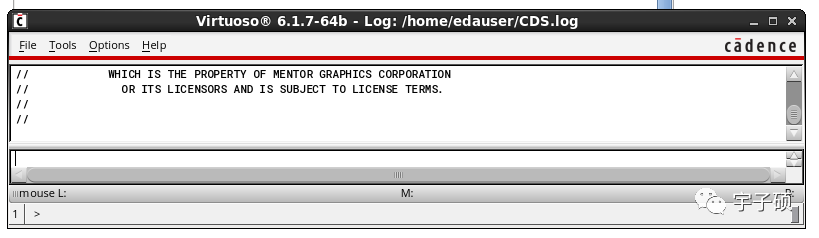

270 首先,在相应终端下键入virtuoso,启动后出现以下窗口。

2023-10-18 15:47:46 742

742

双方的共同客户可获取 Cadence 的全流程系统级设计验证和实现解决方案以及接口 IP,依托 Neoverse CSS 加速开发基于 Arm 的定制 SoC 中国上海,2023 年 10 月 25

2023-10-25 10:40:02 197

197

基于Cadence的IC设计

2022-12-30 09:21:19 6

6 基于 Cadence 30 年的行业知识和领先地位,全新人工智能定制设计解决方案 Virtuoso Studio 采用了多项创新功能和新的基础架构,实现无与伦比的生产力,以及超越经典设计界限的全新集成水平。在本文中,您将了解优异的模拟设计工具如何变得更好,并助您解决挑战性的设计问题。

2024-01-09 12:22:02 445

445

电子发烧友App

电子发烧友App

评论