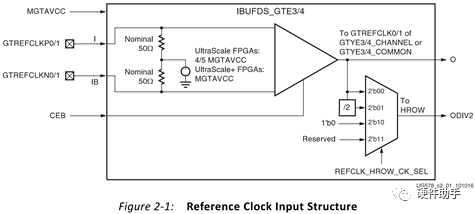

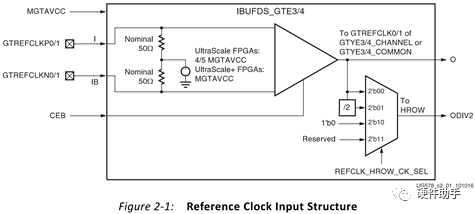

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。 参考时钟的模式 参考时钟可以配置为输入模式也可以是输出模式,但是在运行期间不能切换。作为

2020-11-14 11:39:15 17609

17609

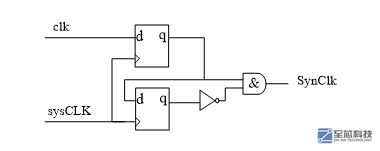

介绍3种跨时钟域处理的方法,这3种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这3招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。 本文介绍的3种方法跨时钟域处理方法如下:

2020-11-21 11:13:01 4997

4997

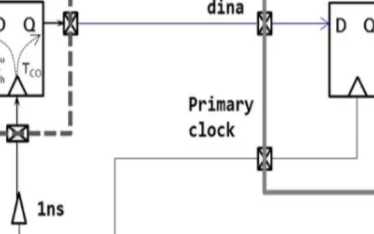

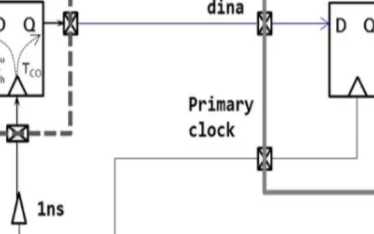

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期 T,则

2020-11-23 13:08:24 4644

4644

我在知乎看到了多bit信号跨时钟的问题,于是整理了一下自己对于跨时钟域信号的处理方法。

2022-10-09 10:44:57 8118

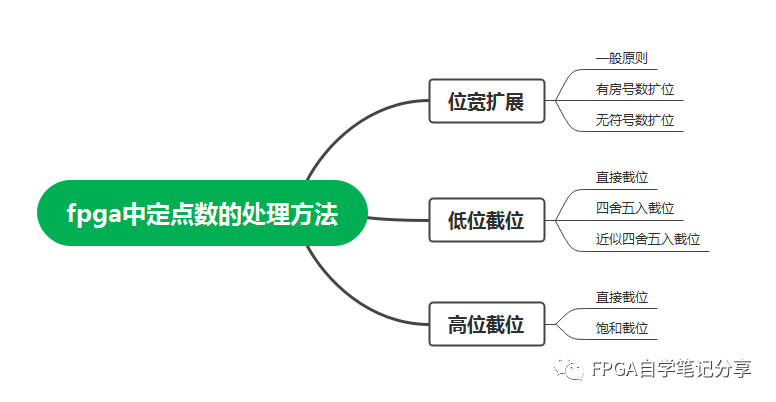

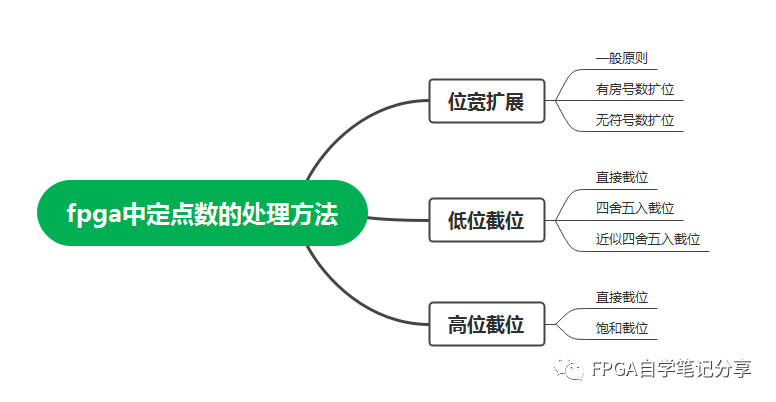

8118 FPGA中最常用的还是定点化数据处理方法,本文对定点化数据处理方法进行简要探讨,并给出必要的代码例子。

2023-05-24 15:10:05 4194

4194

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 5117

5117

篇幅,本文只给出FPCA接收TS101数据的时序图,如图3所示。LxCLKIN、LxDAT[7..0]是DSP的链路口输出时钟和数据,LxCLKOUT是FPGA的回馈准备好信号。仿真中链路口数据采用

2019-06-21 05:00:07

FPGA入门知识介绍近几年来,由于现场可编程门阵列(FPGA)的使用非常灵活,又可以无限次的编程,已受到越来越多的电子编程者的喜爱,很多朋友都想学习一些FPGA入门知识准备进行这个行业,现在关于

2014-08-16 10:32:45

处理的方法,这三种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这三招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。这里介绍的三种方法跨

2021-03-04 09:22:51

FPGA实现高速FFT处理器的设计介绍了采用Xilinx公司的Virtex - II系列FPGA设计高速FFT处理器的实现方法及技巧。充分利用Virtex - II芯片的硬件资源,减少复杂逻辑,采用

2012-08-12 11:49:01

本文重点介绍:1、各种处理器的特点:简要对比各种处理器的特点2、图片处理算法的特点:介绍图片处理算法的特点3、FPGA加速性能的主要因素:分析FPGA能够加速图片处理的原因4、HEVC算法之FPGA

2018-08-01 09:55:53

发送方法适用于低速设备;后接DDR处理器,需要调整的,选择PLL方法;一般推荐使用锁相环(PLL)方法,在不够用的时候,可以选择DDIO方法会前大家正在进行简单的自我介绍并交流一些FPGA的现状分析万

2014-12-31 14:25:41

方法。本系统的主要工作是通过基于FPGA的嵌入式系统,实现数据采集、数据存储、LCD显示、USB数据传输和数据处理,完成光 纤微扰动传感的扰动识别和定位功能。1 系统结构和硬件设计1.1 系统结构

2020-09-04 09:56:23

FPGA设计中有多个时钟域时如何处理?跨时钟域的基本设计方法是:(1)对于单个信号,使用双D触发器在不同时钟域间同步。来源于时钟域1的信号对于时钟域2来说是一个异步信号。异步信号进入时钟域2后,首先

2012-02-24 15:47:57

事半功倍的效果。

FPGA/CPLD的设计思想与技巧是一个非常大的话题,由于篇幅所限,本文仅介绍一些常用的设计思想与技巧,包括乒乓球操作、串并转换、流水线操作和数据接口的同步

2010-11-01 13:17:36

(10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:47:50

本文采用FPGA和ARM结合设计,很好地完成了多通道高精度的数据采集与处理,并且还详细介绍了FPGA逻辑的设计方法。

2021-05-06 06:21:48

RT,求助自己做了一个PL核 获取时钟和数据 并输出 如何把数据传入DDR中,有现成的IP核还是有相关的教程吗开发工具 vivado 除了 使用Video In to AXI4-Stream 和 AXI Video Direct Memroy Access 有没有别的方法麻烦大家了

2022-07-20 09:24:20

关于FPGA芯片资源介绍不看肯定后悔

2021-09-18 08:53:05

各位大虾好,我现在正在做关于fpga的课题。想问问大家用fpga处图像,图片以怎么的方式输入fpga再进行处理。

2013-04-12 11:00:17

AD9266输出数据是在输出时钟的上升沿和下降沿处都有数据,我的电路的是二进制补码输出,10k的偏置电阻选用0.1%,电压0.5v,输出的DCS的时钟没有任何问题,频率和沿都很稳定,但是输出的数据的沿和时钟的沿是对齐的,这个和数据手册的说明不同!!!纠结了很久,跪求可能的原因!!!

2023-12-22 08:12:03

最近采用ADS58C48采集数据,ADS58C48的时钟由FPGA差分提供。上电后,FPGA首先给ADS58C48配置。ADS58C48输出时钟作为FPGA采集数据的时钟。

现在由以下几个问题

2024-12-20 06:32:12

出现毛刺,我们考虑是FPGA输出的150MHz时钟出现严重抖动导致时钟和数据的时序紧张导致,所以想改进设计,FPGA和DA芯片的时钟由高性能的时钟芯片(一个芯片同时出两路同频同相的时钟)提供,但是又碰到

2024-12-04 06:45:50

1、IC设计中的多时钟域处理方法简析我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。跨时钟域处理技术是IC设计中非常重要的一个

2022-06-24 16:54:26

方法。本系统的主要工作是通过基于FPGA的嵌入式系统,实现数据采集、数据存储、LCD显示、USB数据传输和数据处理,完成光 纤微扰动传感的扰动识别和定位功能。1 系统结构和硬件设计1.1 系统结构

2020-08-31 18:54:17

摘要:文章介绍了YCbCr色彩空间和RGB色彩空间之间的转换的方法,实现了不同规模以及不同数据结构的YCbCr到RGB的快速硬件转换。采用数据重排列和数据分离等方法,不仅支持QCIF到HDTV多种

2019-07-01 06:41:21

视频信号(包括数据与时钟,其中数据位宽16位,时钟1位,最高工作频率148.5MHZ).2.遇到的问题时钟相对于数据的延时,也就是信号的建立与保持时间在经过FPGA后出现偏移。造成后端的DA不能正确的采集到数据。

2014-02-10 16:08:02

特点,采用数据流控制的方法实现了信息的并行处理,可以更加有效的实现多通道振动信号采集;同时为了提高数据的可靠性采用时间标定的方法进行数据的存储和校验。本文第一节介绍了该系统的整体设计方案,第二节

2019-07-01 06:11:15

处理的方法,这三种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这三招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。这里介绍的三种方法跨

2021-02-21 07:00:00

时钟域处理的方法,这三种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这三招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。 这里介绍

2021-01-08 16:55:23

这是测试SHT1X温度传感器的程序,但为什么没有定义时钟引脚和数据引脚是输入还是输出?哪位大神知道的,可以解答一下吗?

2017-03-28 10:24:06

必须适当地与所有数据位的到达保持同步。如果接收器使用发射时钟,可能会要求延迟从发送端到接收端的时钟信号。 有时设计可能需要一个更高的时钟频率来运行FPGA上的逻辑。但是,只有低频率输出的时钟源可以用

2020-04-25 07:00:00

,理想的时钟模型是一个占空比为50%且周期固定的方波。为一个时钟周期,为高脉冲宽度,为低脉冲宽度,=+。一般情况下,FPGA器件内部的逻辑会在每个时钟周期的上升沿执行一次数据的输入和输出处理,而在两个

2017-10-18 21:42:45

图像处理FPGA 设计基本方法:1.阵列结构结合流水线处理设计例如RGB图像,包括三组数据,处理时需要并行三通道后,每个通道进行分别的串行流水处理。2.缓存设计帧缓存 行缓存 列对齐3.资源分辨率 处理窗口 对资源影响成倍增加

2019-01-04 13:59:26

跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨

2020-09-22 10:24:55

介绍3种跨时钟域处理的方法,这3种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这3招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。本...

2021-07-29 06:19:11

数据抓取程序。我打算用FPGA存储高速数据(6位+时钟CMOS / LVDS输出),然后通过USB接口读取数据并在matlab中进行后处理。市场上有大量的FPGA可用。但是,我真的很难选择合适的FPGA来解决这个问题。如果有人可以就这个问题向我提出建议。那将会很棒。请回复你的回复。谢谢。-Bala

2019-11-04 07:47:53

跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨

2020-10-20 09:27:37

嗨,我正在使用Kintex-7 FPGA来运行带有来自DAC的反馈差分时钟的高速DAC,我必须提供定时对齐数据,当然还有一个合适的差分输出时钟到转换器,具有精确的数据而不是生成的数据。数据和时钟信号

2020-08-17 10:25:13

设置为自己想要的延时么?但是这样设置完成以后,生成的模块仍然会有数据的输入引脚,和输出引脚,这些引脚怎么办呢?我只想要时钟延时。还有没有其他的方法来解决同步这个问题呢?

2016-08-14 16:58:50

由相同时钟驱动,即使第一级触发器的输出可用,通常还是需要用像图6中电路来将亚稳态隔离到一条短线。采用这种方法后,将不太可能出现由于电路的改变而无意地在无时钟驱动的逻辑中用到该亚稳太线。如果读数据的是一

2020-04-26 07:00:00

介绍时钟的同步处理方法

2018-02-09 11:21:12

你们好,

我们正在使用AD9779A进行设计,有如下疑问:

(1) 使用AD9779A的数据时钟信号(DATACLK)作为FPGA内部PLL的参考时钟,再用FPGA PLL产生的时钟信号把数据

2023-12-20 07:12:27

大家好,我的ADC32XX 采样率为125M,将转换后的数据发送给FPGA,请问ADC32xx的时钟由FPGA直接输出吗?FPGA IO口是3.3V的,如果是这样的话是不是得电平转换一下,速率能保证吗?是否有更好的方法给出这个时钟呢?谢谢!

2025-01-02 08:30:45

频率不可能达到100MHz以上。本文采用的方法是利用锁相环产生不同相位的时钟信号,然后再根据控制信号控制输出时钟在这些时钟之间进行切换,从而使时钟与输入数据同步。具体结构如图2所示。下面详细介绍各个模块

2009-10-24 08:38:08

在介绍了GPS 同步时钟基本原理和FPGA 特点的基础上,提出了一种基于FPGA 的GPS同步时钟装置的设计方案,实现了高精度同步时间信号和同步脉冲的输出,以及GPS 失步后秒脉冲的平

2009-07-30 11:51:45 45

45 ADN2817/ADN2818可提供下列接收器功能:量化、信号电平检测、时钟和数据恢复,适用于从10 Mbps到2.7 Gbps的连续数据速率。二者均可自动锁定至所有数据速率,而无需外部参考时钟或

2023-02-14 10:05:22

介绍了一种运用FPGA将IPV6数据包的包头和数据部分分离并重新封装的方法。利用该方法,可以使IPV6数据包的拆装处理速度达到2Gbit/s以上。

2010-06-25 17:53:59 14

14 介绍了时钟和数据恢复器件ADN2814的主要性能、内部结构和引脚功能,给出了ADN2814在信号传输中的应用电路,同时介绍了系统中时钟和数据恢复器件的选择方法及应用分析。

2010-12-14 10:21:28 23

23 大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 827

827

利用FPGA实现时分多址的方法有很多种,但大多数方法都对FPGA芯片资源的占用非常巨大。针对这一问题,提出一种改进型方法来实现时分多址。通过使用FPGA芯片内部的双口随机访问存储器(双口RAM),利用同一块RAM采用两套时钟线,地址线和数据线,例化双口RAM的

2011-01-15 15:41:26 29

29 在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 4131

4131

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数

2012-05-21 11:26:10 1591

1591

基于FPGA的小波图像实时处理方法,下来看看

2016-09-22 13:06:19 33

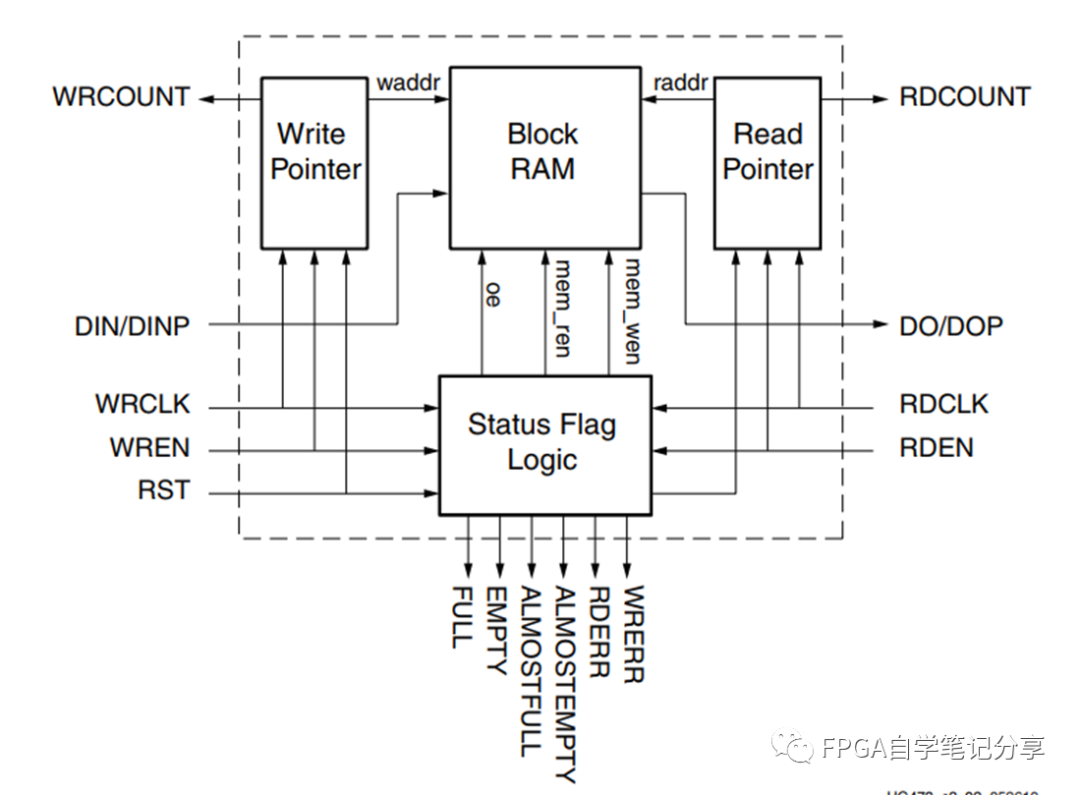

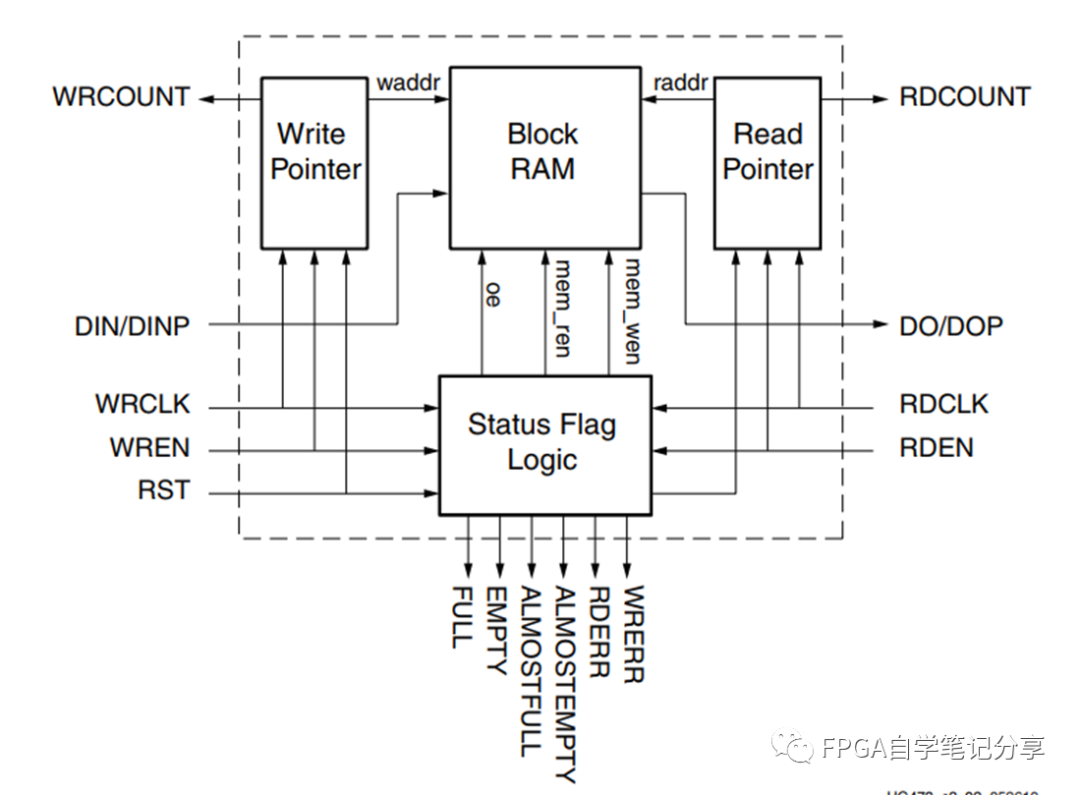

33 介绍3种跨时钟域处理的方法,这3种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这3招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。 本文介绍的3种方法跨时钟域处理方法如下:打两拍;异步双口RAM;格雷码转换。

2017-11-15 20:08:11 14725

14725 一般情况下,FPGA器件内部的逻辑会在每个时钟周期的上升沿执行一次数据的输入和输出处理,而在两个时钟上升沿的空闲时间里,则可以用于执行各种各样复杂的处理。而一个比较耗时的复杂运算过程,往往无法一个时钟周期完成,便可以切割成几个耗时较小的运算,然后在数个时钟上升沿后输出最终的运算结果。

2018-05-23 05:56:00 8320

8320

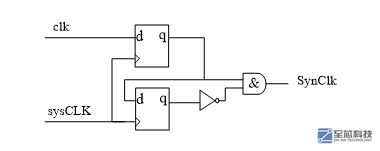

大家好,又到了每日学习的时候了。今天我们来聊一聊异步电路中的时钟同步处理方法。 既然说到了时钟的同步处理,那么什么是时钟的同步处理?那首先我们就来了解一下。 时钟是数字电路中所有信号的参考,没有时钟

2018-05-21 14:56:55 13596

13596

FPGA常见的警告以及处理方法 1.Found clock-sensitive change during active clock edge at time on register 原因

2018-05-21 14:53:16 13430

13430 。同时在许多系统中都需要实时时钟,而应用最广泛的当数的时钟芯片。摩托罗拉的系列地址线和数据线是独立的,而的时钟芯片的地址线和数据线是复用的。本文以和为例,给出接口的设计方法和电路。因为用来实现,进步增加了通用性。

2018-12-15 09:42:54 2354

2354 跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟域的数量急剧增加。通常不止数百个,而是超过一千个时钟域。

2019-08-19 14:52:58 3895

3895 跨时钟域处理的方法,这三种方法可以说是 FPGA 界最常用也最实用的方法,这三种方法包含了单 bit 和多 bit 数据的跨时钟域处理,学会这三招之后,对于 FPGA 相关的跨时钟域数据处理便可以手到擒来。 这里介绍的三种方法跨时钟域处理方法如下: 打两

2022-12-05 16:41:28 2398

2398 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

2020-12-10 15:00:29 16

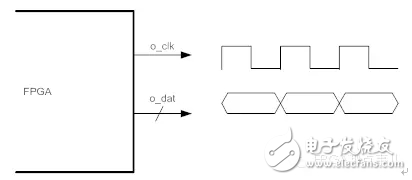

16 该设计元素是专用的输入寄存器,旨在将外部双数据速率(DDR)信号接收到Xilinx FPGA中。IDDR可用的模式可以在捕获数据的时间和时钟沿或在相同的时钟沿向FPGA架构显示数据。此功能使您可以避免其他时序复杂性和资源使用情况。

2021-03-13 09:07:33 7161

7161 引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。这些网络被设计成具有低偏移和低占空比失真、低功耗和改进的抖动容限。它们也被设计成

2021-03-22 10:09:58 14973

14973

对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。只要可能就应尽量在设计项目中采用全局时钟。FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。

2021-04-24 09:39:07 7808

7808

ADN2806:622 Mbps时钟和数据恢复IC数据表

2021-05-08 11:26:35 8

8 AD800/AD802:时钟恢复和数据重定时锁相环数据表

2021-05-18 14:11:56 9

9 ADN2805:1.25 Gbps时钟和数据恢复IC数据表

2021-05-25 10:58:12 3

3 介绍3种跨时钟域处理的方法,这3种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这3招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。 本文介绍的3种方法跨时钟域处理方法如下:

2021-09-18 11:33:49 23260

23260

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2021-09-23 16:39:54 3632

3632 在设计FPGA项目的时候,对时钟进行约束,但是因为算法或者硬件的原因,都使得时钟约束出现超差现象,接下来主要就是解决时钟超差问题,主要方法有以下几点。 第一:换一个速度更快点的芯片,altera公司

2021-10-11 14:52:00 4267

4267

说到异步时钟域的信号处理,想必是一个FPGA设计中很关键的技术,也是令很多工程师对FPGA望 而却步的原因。但是异步信号的处理真的有那么神秘吗?那么就让特权同学和你一起慢慢解开这些所谓的难点

2021-11-01 16:24:39 11

11 (10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

2022-02-16 16:21:33 4905

4905

FPGA图像处理应用详细介绍

2022-02-28 10:29:49 51

51 SWM系列关于UART/CAN/PLL等时钟相关模块,计算波特率的方法。

2022-03-18 16:52:25 9466

9466 跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。

2022-10-18 09:12:20 9685

9685 ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、时钟延迟匹配等方式对整个时钟结构进行处理,但是 FPGA设计则完全不必。

2022-11-23 16:50:49 1249

1249

由于信号在不同时钟域之间传输,容易发生亚稳态的问题导致,不同时钟域之间得到的信号不同。处理亚稳态常用打两拍的处理方法。多时钟域的处理方法很多,最有效的方法异步fifo,具体可以参考博主

2023-02-17 11:10:08 1588

1588 跨时钟域是FPGA设计中最容易出错的设计模块,而且一旦跨时钟域出现问题,定位排查会非常困难,因为跨时钟域问题一般是偶现的,而且除非是构造特殊用例一般的仿真是发现不了这类问题的。

2023-05-25 15:06:00 2919

2919

上一篇文章已经讲过了单bit跨时钟域的处理方法,这次解说一下多bit的跨时钟域方法。

2023-05-25 15:07:19 1622

1622

所谓数据流跨时钟域即:时钟不同但是时间段内的数据量一定要相同。

2023-05-25 15:19:15 2725

2725

本文主要用来随意记录一下最近在为手头的FPGA项目做约束文件时候遇到的一点关于FPGA专用时钟管脚相关的内容,意在梳理思路、保存学习结果、以供自己日后以及他人参考。

2023-08-07 09:20:25 3686

3686

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2023-08-23 16:10:01 1372

1372 时,由于时钟频率不同,所以可能会产生元件的不稳定情况,导致传输数据的错误。此时我们需要采取一些特殊的措施,来保证跨时钟域传输的正确性。 FPGA跨时钟域通信的基本实现方法是通过FPGA内部专门的逻辑元件进行数据传输。发送方用一个逻辑电路

2023-10-18 15:23:51 1901

1901 电子发烧友网站提供《基于FPGA在通讯领域和数据存储的应用.pdf》资料免费下载

2023-10-26 11:06:55 0

0 异步电路中的时钟同步处理方法 时钟同步在异步电路中是至关重要的,它确保了电路中的各个部件在正确的时间进行操作,从而使系统能够正常工作。在本文中,我将介绍一些常见的时钟同步处理方法。 1. 时钟分配

2024-01-16 14:42:44 2200

2200 FPGA(现场可编程门阵列)在处理异步信号时,需要特别关注信号的同步化、稳定性以及潜在的亚稳态问题。由于异步信号可能来自不同的时钟域或外部设备,其到达时间和频率可能不受FPGA内部时钟控制,因此处理起来相对复杂。以下是对FPGA异步信号处理方法的详细探讨。

2024-07-17 11:10:40 2415

2415 在FPGA(现场可编程门阵列)设计中,消除时钟抖动是一个关键任务,因为时钟抖动会直接影响系统的时序性能、稳定性和可靠性。以下将详细阐述FPGA中消除时钟抖动的多种方法,这些方法涵盖了从硬件设计到软件优化的各个方面。

2024-08-19 17:58:54 3753

3753 广泛应用于以太网、USB、PCI Express、SATA、HDMI等通信协议的处理。它们通过高速串行接口实现数据传输,并利用硬件加速技术进行协议解析和数据处理,从而提高系统性能。例如,在路由器、交换机等网络设备中,FPGA可以实现高速的数据包处理、转发和路

2024-10-25 09:21:49 2013

2013

电子发烧友App

电子发烧友App

评论