异步电路中的时钟同步处理方法

时钟同步在异步电路中是至关重要的,它确保了电路中的各个部件在正确的时间进行操作,从而使系统能够正常工作。在本文中,我将介绍一些常见的时钟同步处理方法。

1. 时钟分配网络

时钟分配网络是实现异步电路的一种常用方法。它将一个主时钟信号分发给整个电路,以确保电路中的所有部件都按照相同的时钟进行操作。时钟分配网络通常包含许多时钟树,每个时钟树都将时钟信号传递给一部分电路。时钟分配网络的设计需要考虑电路的延迟、功耗和抖动等因素。

2. 时钟缓冲器

时钟缓冲器用于加强时钟信号的驱动能力,并减小时钟信号在传输过程中的延迟。它可以将一个时钟信号放大并传输给下一个电路模块,以确保时钟信号的准确性和稳定性。时钟缓冲器通常由锁相环 (PLL) 或延迟锁相环 (DLL)等电路组成,这些电路可以从输入时钟生成一个更稳定的输出时钟信号。

3. 时钟域划分

在大型异步电路中,为了提高电路的性能,通常会将电路划分为多个互相独立的时钟域。每个时钟域都有自己的时钟信号,并且时钟信号之间存在着一定的相位差。时钟域划分可以减小时钟信号传输的延迟和功耗,提高系统的整体性能。

4. 时钟同步器

时钟同步器用于在两个不同的时钟域之间进行时钟信号的同步。由于不同时钟域的时钟信号存在相位差,直接将信号传递可能导致数据错误。时钟同步器可以将一个时钟域中的时钟信号转换为另一个时钟域中的时钟信号,以确保时钟信号的同步性。

5. 异步 FIFO

异步 FIFO 是一种常用的时钟同步器件,用于在两个不同的时钟域之间进行数据的传输和同步。它包含一个读指针和一个写指针,以及一些用于存储数据的存储单元。异步 FIFO 通过读写指针之间的差值来确定数据是否可以被读取或写入。读写指针之间的握手信号通过时钟同步器来同步,以保证数据的可靠传输。

6. 异步复位电路

异步复位电路用于在异步电路中进行复位操作。复位信号可以将电路中的所有部件重置到初始状态,以确保电路的正确启动。异步复位电路通常包含一个复位信号和一个时钟信号,复位信号可以在时钟信号上升沿或下降沿触发,加载初始状态。

总结:

时钟同步是异步电路设计中不可忽视的一部分。时钟分配网络、时钟缓冲器、时钟域划分、时钟同步器、异步 FIFO 和异步复位电路等方法都可以用来实现时钟同步。这些方法可以确保电路中的各个部件按照正确的时间进行操作,从而提高系统的性能和可靠性。在设计异步电路时,我们需要仔细考虑时钟同步处理方法的选择,以满足系统的需求。

-

缓冲器

+关注

关注

6文章

2236浏览量

49046 -

时钟同步

+关注

关注

0文章

141浏览量

13607 -

异步电路

+关注

关注

2文章

48浏览量

11561

发布评论请先 登录

同步复位和异步复位到底该用哪个

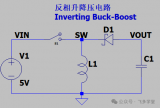

使用异步降压开关稳压芯片产生负电压的方法

如何处理电能质量在线监测装置时钟模块自动同步异常的情况?

AMD FPGA异步模式与同步模式的对比

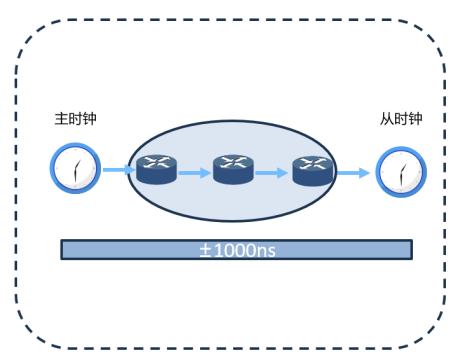

PTP 时钟:精准时钟同步的核心力量

PTP 时钟:精准时钟同步的核心力量

跨异步时钟域处理方法大全

ntp时钟同步服务器是什么?ntp时钟同步服务器介绍

电容在时钟电路中的应用有哪些

TSN时钟同步精度技术解析:TSN网络的基石与保障

异步电路中的时钟同步处理方法

异步电路中的时钟同步处理方法

评论