FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。Efinity debuger常见问题总结-v2

Efinity在Debug时会出现UUID mismatch错误。很多刚开始使用的人经常遇到。下面我们做一个总结。欢迎遇到案例时共同分享。...

2024-07-11 1152

P4 Suite for FPGA面市 P4 Suite for FPGA主要功能解析

基本简介 P4 Suite for FPGA是一款 综合性工具套件, 可在数字网络的不同领域提供广泛功能,该套件能够以高达200 Gbps甚至更高的数据传输速率支持FPGA。这一发展为虚拟蜂窝基站路由器...

2024-07-25 166

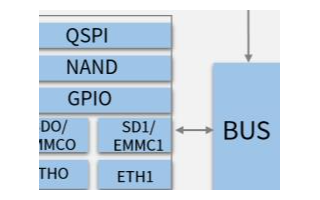

基于安路科技FPSoC器件DR1系列的视频采集/显示/处理解决方案

安路科技全新一代FPSoC器件DR1系列, 集成高性能硬核处理器双核ARM Cortex-A35或单核64位RISC-V、丰富的片上内存和高低速外设接口、FPGA可编程逻辑、NPU/JPU硬件加速单元, 内部通过高带宽总线互联...

2024-06-29 631

FPGA厂商紫光同创入选多样性算力产业及标准推进委员会黄金成员

日前,“共筑新算力,智启新未来”多样性算力产业峰会2024在北京成功举办。本次峰会由中国通信标准化协会多样性算力产业及标准推进委员会主办,来自计算产业代表近400人参加。紫光同创...

2024-06-23 926

易灵思的时钟网络问题

在T20中有16个全局时钟网络GCLK。在芯片的左右两侧各8个。全局时钟管脚或者PLL的输出时钟通过左右两个CLKMUX上全局网络。左侧的PLL(包括PLL_TL0和PLL_TL1)上左侧的CLKMUX_L;右侧的PLL(包括PLL_TR0,PL...

2024-06-20 1023

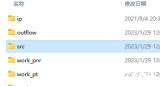

加法进位链的手动约束

在激光雷达中,使用FPGA实现TDC时需要手动约束进位链的位置。这里简单记录下。 在outflow下会生成一个.qplace文件 。用于指示布线的各个原语资源的分布位置 。 它的内容主是 是原语的单元名...

2024-05-20 966

FPGA是实现敏捷、安全的工业4.0发展的关键

到2028年,全球工业4.0市场规模预计将超过2790亿美元,复合年增长率为16.3%。虽然开发商和制造商对这种高速增长已经习以为常,但其影响才刚刚开始显现。通过结合云计算、物联网(IoT)和人...

2024-05-10 467

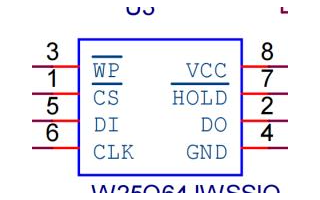

Ti60F100 内外flash操作方案

有客户认为Ti60F100内部flash容量比较小,只有16Mb,需要外挂flash.这里我们提供了内部flash和外部flash分别操作的方案。 该程序是通过SOC操作4线的外部flash和内部flash.程序先经过外部flash的擦除,写...

2024-05-20 945

时序约束实操

添加约束的目的是为了告诉FPGA你的设计指标及运行情况。在上面的生成约束之后,在Result àxx.sdc中提供约束参考(请注意该文件不能直接添加到工程中,需要热复制到别的指定目录或者新建自...

2024-04-28 1610

易灵思RAM使用--Update4

易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。 1、ram初始化文件路径是工程路径 在对ram进行初始化时需要指定文件路径,这里要注意'/'的方向。 (1)如果文件放在工程目...

2024-04-23 703

易灵思Jtag_bridge_loader生成-v2

Efinity版本:2023.1及以前版本。 易灵思器通过jtag bridge烧写flash时需要自己生成一个jtage birdge文件。jtage bridge 工程的目的是为了打通JTAG与flash的连接。 (1)打开IPM (2)选择Memory Controllers --> J...

2024-04-15 876

gtkwave界面每次都更新太麻烦?来个小技巧-v1

迄今为止,大家都在吐槽gtkwave debug每次弹窗都会覆盖上一次弹窗设置好的排序和参数。下面我们分享一个可以暂时规避该问题的方法,聊以慰藉久被摧残的心~~。 (1)添加debug ,无论手动或者自...

2024-04-15 815

国产FPGA应用专题--易灵思Efinity软件使用心得

做为FPGA的集成开发环境,不同的厂家其实大同小异。很多国产厂家,如安路,高云,会在软件上贴近Xilinx和Intel,以节省客户的软件使用成本。而国产厂商的易灵思的集成开发环境Efinity似乎并...

2024-04-23 1118

FPGA厂商安路科技荣登《2024上海硬核科技企业TOP100》榜单

3月22日,2024年上海市产业技术创新大会在沪顺利举办,现场,市产业技术创新促进会联合市科协发布《2024上海硬核科技企业TOP100榜单》。上海安路信息科技股份有限公司再次荣登榜单。 硬核...

2024-03-25 727

中端FPGA成为主战场,Altera独立后的市场格局

电子发烧友网报道(文/周凯扬)随着前几年Xilinx被AMD收购,近期Altera从英特尔独立出来,不少人都在关注FPGA市场会迎来怎样的变局。在这个AI ASIC爆火的时代,可编程的FPGA如何找到新的增长点...

2024-03-12 3446

以自适应创新为未来“嵌入”新动能

2023 年伊始,ChatGPT 以迅雷之势席卷全球,引发了生成式 AI 热潮。从大语言模型到内容生成、创作与艺术再到人机协作,令人振奋的创新层出不穷,AI 技术的应用场景不断拓展。在云端训练与推...

2024-02-18 285

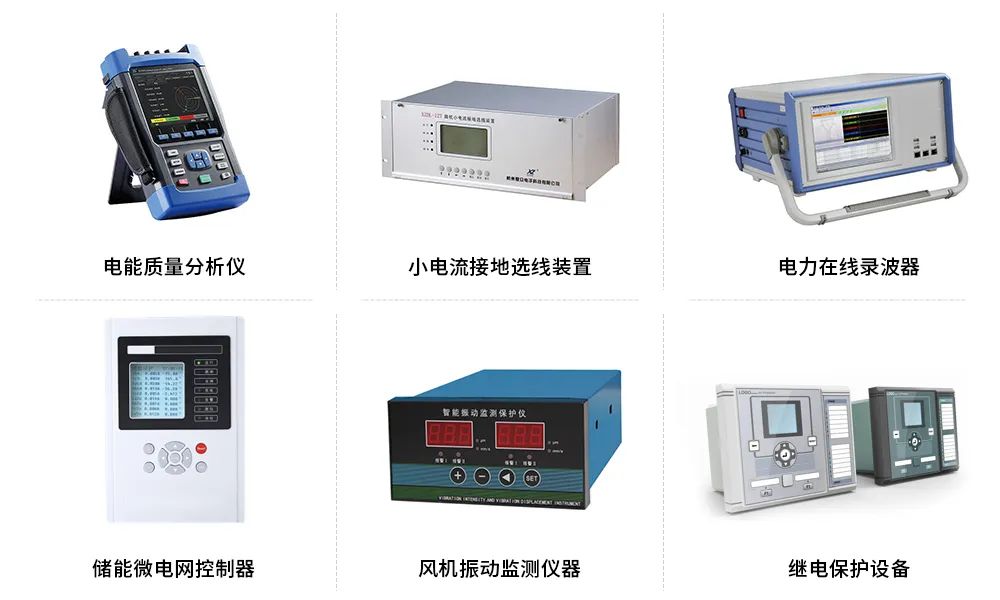

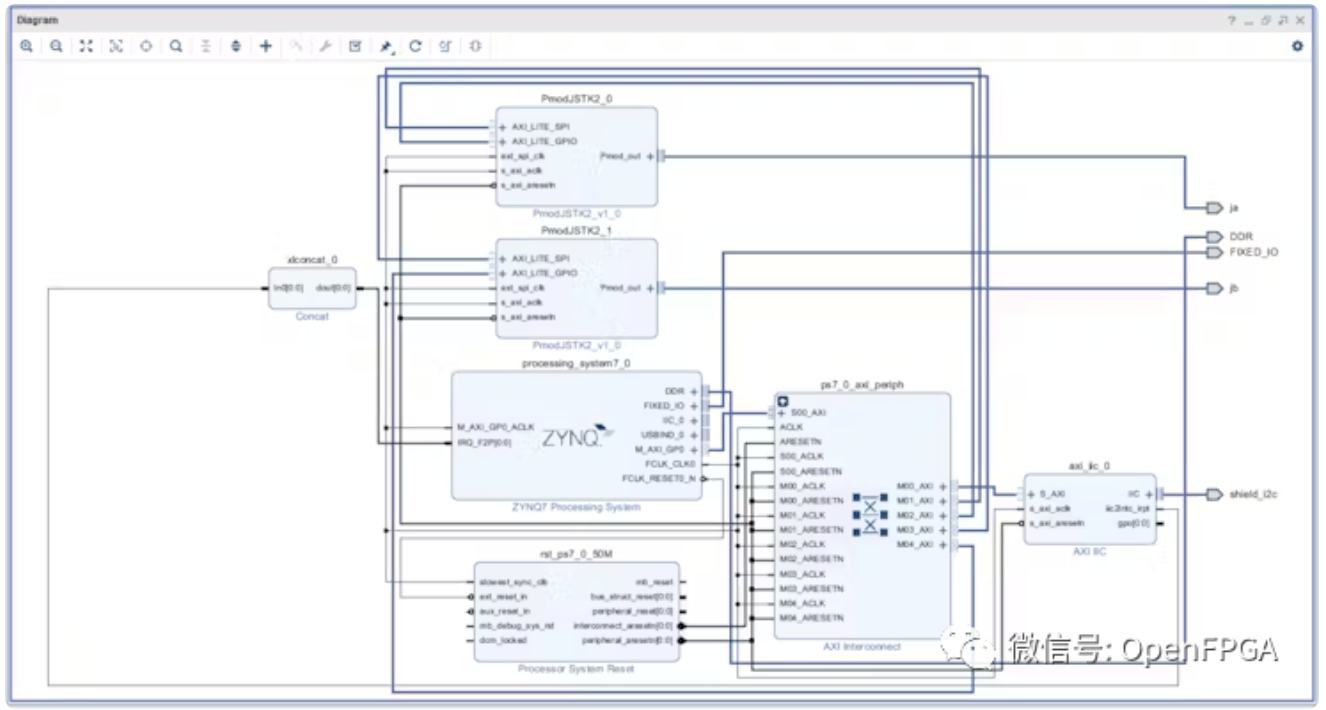

全国产T3+FPGA的SPI与I2C通信方案分享

近年来,随着中国新基建、中国制造2025规划的持续推进,单ARM处理器越来越难胜任工业现场的功能要求,特别是如今能源电力、工业控制、智慧医疗等行业,往往更需要ARM + FPGA架构的处理器平...

2024-02-06 4317

国外大学的FPGA开发项目盘点

据我了解,目前国内很多大学是没有开设FPGA相关课程的,所以很多同学都是自学,但是自学需要一定的目标和项目,今天我们就去看看常春藤盟校Cornell University 康奈尔大学开设的FPGA项目课程。...

2023-12-22 681

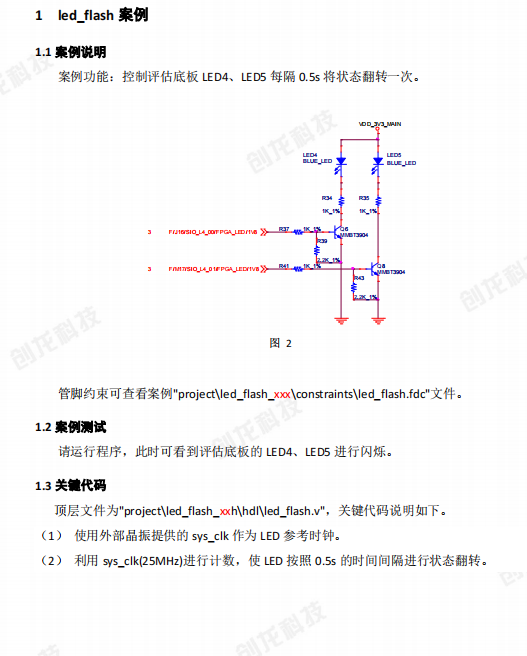

基于FPGA的UART控制器设计

串口的出现是在1980年前后,数据传输率是115kbps~230kbps。串口出现的初期是为了实现连接计算机外设的目的,初期串口一般用来连接鼠标和外置Modem以及老式摄像头和写字板等设备。串口也可以...

2023-12-04 1094

国产FPGA厂商西安智多晶微电子E轮融资获得上汽入股

9月份,西安智多晶微电子有限公司再传好消息,智多晶微电子完成了数亿人民币的E轮融资,此次智多晶微电子的E轮融资由尚颀资本(上汽集团金融平台上汽金控旗下私募股权投资机构)在管基...

2023-11-30 1183

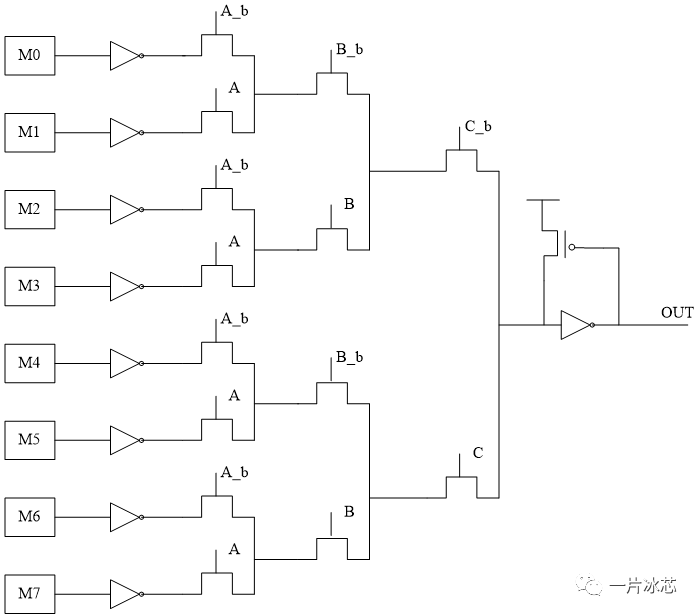

FPGA中的逻辑运算是如何实现的?

可编程逻辑功能块(Configurable Logic Blocks, CLB),顾名思义就是可编程的数字逻辑电路,可以实现各种逻辑功能。...

2023-10-31 927

FPGA加速卡的PCB设计注意事项

本应用笔记概述了PCI Express卡机电规范修订版3.0定义的加速卡外形尺寸。它解决了印刷电路板 (PCB) 设计挑战,从堆叠设计到介电材料选择,再到 PCB 设计过程中使用的 PCB 制造技术。 该图显示...

2023-10-30 9021

Xilinx FPGA芯片内部时钟和复位信号使用方法

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。...

2023-10-27 1307

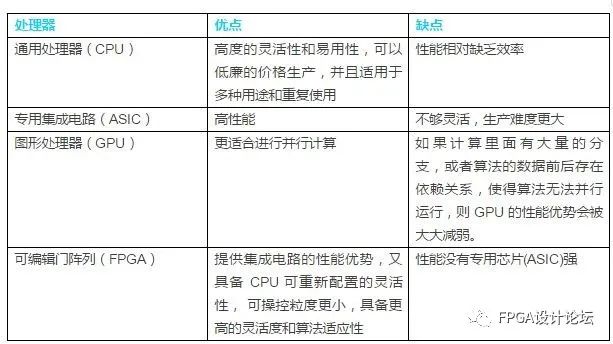

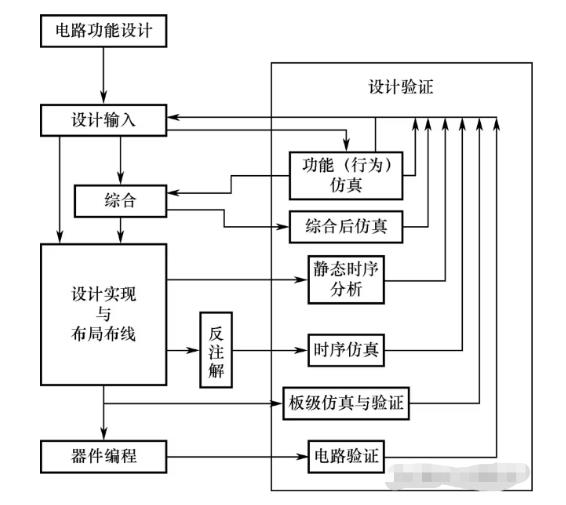

fpga的开发流程有哪些步骤?fpga和嵌入式系统的区别在哪里?

fpga和嵌入式系统的区别有哪些?小编先带大家了解一下。 FPGA和嵌入式系统在电子信息工程领域有着不同的应用和特点。 FPGA,即现场可编程门阵列,是在PAL、GAL、CPLD等可编程器件的基础上进一...

2023-10-24 1860

介绍一种具备RDMA功能的FPGA网卡实现方案—RNIC

传统TCP/IP技术处理数据包需通过操作系统和其他软件层,导致数据在系统内存、处理器缓存和网络控制器缓存间频繁复制,增加了服务器CPU和内存的负担,特别是在网络带宽、处理器速度与内存...

2023-10-22 3265

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |