在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟:

FPGA时序约束理论篇之时钟周期约束

但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

首先,虚拟时钟用于什么地方?

虚拟时钟通常用于设定输入和输出的延时,即set_input_delay和set_output_delay。可能有同学忘记这两个约束的用法了,这里我们再展示一下:

set_input_delay 0.5 -clock clkA [get_ports A] set_output_delay 1 -clock clkB [get_ports B]

其中clkA和clkB就是我们使用create_clock创建的主时钟或者虚拟时钟。

主时钟在创建的时候需要指定时钟输入端口,虚拟时钟不需要指定端口,所以称之为虚拟时钟。那什么场景下要用到虚拟时钟呢?

1. 外部IO的参考时钟并不是设计中的时钟

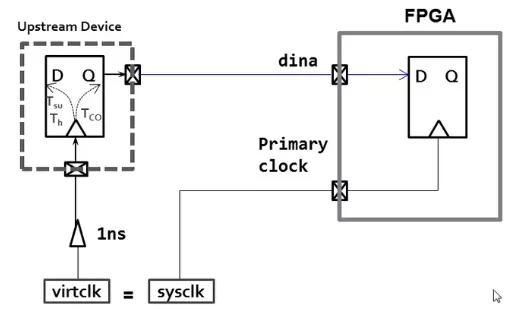

下图中,外部IO的参考时钟比设计中主时钟的路径上多了一个BUFFER,因此我们需要使用虚拟时钟来进行约束。

create_clock -name sysclk -period 10 [get_ports clkin] create_clock -name virtclk -period 10 set_clock_latency -source 1 [get_clock virtclk] set_input_delay -clock virtclk -max 4 [get_ports dina] set_input_delay -clock virtclk -min 2 [get_ports dina]

2. FPGA I/O路径参考时钟来源于内部衍生时钟,但与主时钟的频率关系并不是整数倍

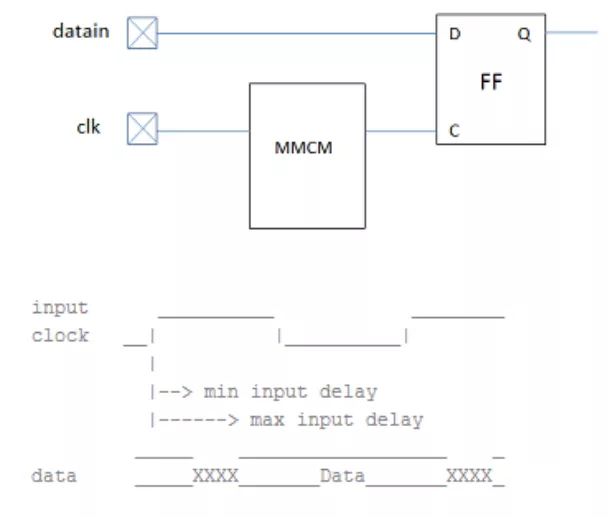

如果I/O路径参考时钟源于内部的衍生时钟,那set_input_delay和set_output_delay约束中-clock参数后的时钟不能是衍生时钟,比如下图的例子中,输入10MHz时钟经过了MMCM后去采输入的数据。

a) 如果MMCM没有负的相移而且输出的频率也是10MHz,那么直接使用主时钟来约束input delay。

create_clock -period 100.000 -name clk [get_ports clk] set_input_delay -clock clk -max 2.000 [get_ports datain] set_input_delay -clock clk -min 1.000 [get_ports datain]

b) 如果MMCM输出频率是60MHz,那么这个衍生时钟跟主时钟并不是整数倍关系,这时就需要用到虚拟时钟了

create_clock -period 100.000 -name clk [get_ports clk] create_clock -name clk_port_vclk -period 16.67 set_input_delay -clock clk_port_vclk -max 2 [get_ports datain] set_input_delay -clock clk_port_vclk -min 1 [get_ports datain]

3. 在不修改时钟特性的情况下针对I/O指定不同的jitter和latency

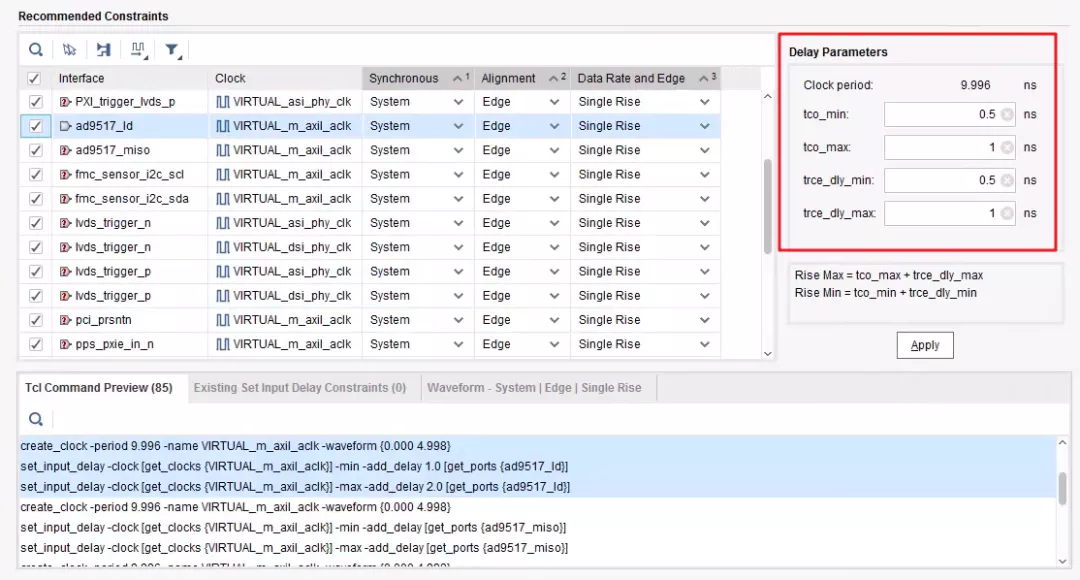

在设置完成后,可以看到Tcl Command Preview中提示的约束指令。

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22504浏览量

639318 -

端口

+关注

关注

4文章

1110浏览量

34051 -

虚拟时钟

+关注

关注

0文章

5浏览量

6710

发布评论请先 登录

Xilinx FPGA中的混合模式时钟管理器MMCME2_ADV详解

浅谈FPGA的时钟输入要求

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

ups电源的作用和使用方法详解

数字IC/FPGA设计中的时序优化方法

堆栈的定义,堆栈的使用方法

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

E203软核提高CPU时钟频率方法

锡膏的储存及使用方法详解

LCR测试仪的使用方法与注意事项

FPGA虚拟时钟的使用方法

FPGA虚拟时钟的使用方法

评论