赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。本文为您解惑......

2013-07-23 09:25:53 20763

20763

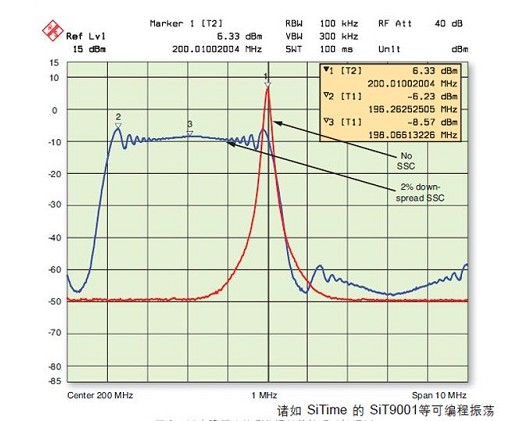

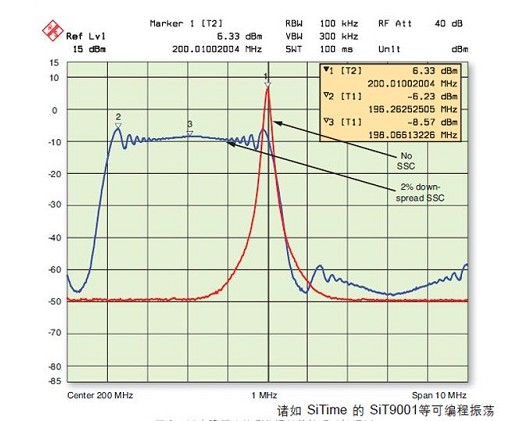

内在可编程的硅 MEMS 时钟振荡器架构能够帮助采用 FPGA 的系统设计人员解决许多难题。这种微型机电系统架构能够轻松整合一些其它功能,如:用于消减 EMI 的扩频时钟、用于消除抖动的数控振荡器以及高速应用中的失效保护功能。

2013-08-15 11:12:08 3187

3187

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。

2019-09-10 15:12:31 7150

7150

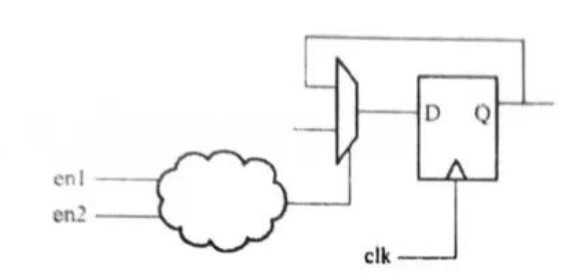

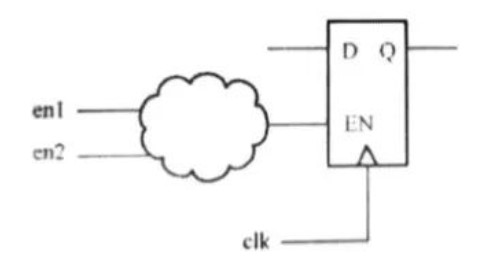

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期 T,则

2020-11-23 13:08:24 4644

4644

7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 2068

2068 当我刚开始我的FPGA设计生涯时,我对明显更小、更不灵活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常简单的时钟规则之一是尽可能只使用单个时钟。当然,这并不总是可能的,但即便如此,时钟的数量仍然有限。

2022-09-30 08:49:26 2145

2145 在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 4234

4234 “全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 1443

1443

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 4432

4432

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 5117

5117

生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成,也可以由具有分频功能的时钟缓冲器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 3808

3808

时钟设计方案 在复杂的FPGA设计中,设计时钟方案是一项具有挑战性的任务。设计者需要很好地掌握目标器件所能提供的时钟资源及它们的限制,需要了解不同设计技术之间的权衡,并且需要很好地掌握一系列

2024-01-22 09:30:50 1413

1413

作为一名FPGA工程师,经常需要在多个FPGA设备之间移植项目,核心的问题是IP的管理和移植,今天通过安装和使用 FuseSoC 在多个 AMD FPGA 之间移植一个简单的项目。从 AMD Spartan 7 更改为 AMD Artix 7 设备,然后是 AMD Kintex UltraSacle。

2024-11-20 16:12:15 2584

2584

(08)FPGA时钟概念1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟概念5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2022-02-23 07:26:05

谁有,或者知道在DE2开发板上面能用的,用FPGA移植好的ARM核吗?

2016-05-12 16:09:56

一般我们用的FPGA的时钟都是用晶振来提供的,我想请教一下大家,可以用锁相环芯片AD9518(或者其它锁相环)来生成时钟供给FPGA,作为FPGA的系统时钟

2013-08-17 11:20:41

时钟电路本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 人体拥有非常奇妙的循环系统,而心脏是这个循环系统

2019-04-12 01:15:50

你好我有一个关于时钟断言的问题基本上我的实验是JESD204B测试(KC 705带DAC37J82板)这是基本设置FPGA clk(IP内核时钟来自另一个DAC板通过FMC连接器)系统工作正常1.

2019-04-10 12:35:21

FPGA的多时钟系统设计 Multiple Clock System Design Clk1and Clk2are the clock which running at different frequency[/hide]

2009-12-17 15:46:09

1、背景最近,做移植,因此对目标平台做一些了解。STM32L051C6T6资源为32K Flash;2K EEPROM;8K RAM;37 GPIOs;1ADC(10 Channels)2、系统刚

2021-08-18 07:27:07

LTC6915的采样时钟是多少,与FPGA 系统时钟相同吗

2023-11-14 07:55:38

从ASIC到FPGA的转换系统时钟设计方案

2011-03-02 09:37:37

2.9.2 单个脉冲信号的时钟域跨越

2.9.3 多比特总线的时钟域跨越

... ...

该书籍中的大部分内容都移植到了小脚丫FPGA旗下的STEP CYC10开发板上,并将相关的技术细节在书中做了详细

2024-03-29 00:06:44

摘要:随着石油勘探的发展,在地震勘探仪器中越来越需要高精度的同步技术来支持高效采集。基于这种目的,采用FPGA技术设计了一种时钟恢复以及系统同步方案,并完成了系统的固件和嵌入式软件设计。通过室內测试

2019-06-18 08:15:35

视频过大,打包成8个压缩包基于FPGA设计的数字时钟.part01.rar (20 MB )基于FPGA设计的数字时钟.part02.rar (20 MB )基于FPGA设计的数字时钟

2019-05-14 06:35:34

我做的一个基于DSP的系统中,DSP做主处理器,控制着整个系统,包括信号处理,整体调度等;选择了一块Xilinx的FPGA做FIFO UART和系统的逻辑控制和译码。DSP的时钟输入为15MHz

2023-06-19 06:43:17

如题,请问各位大神如何将ucos ii/iii移植FPGA Nios ii。Altera的FPGA软件里可以直接例化调用一个ucos,但要如何自己移植一个原版系统呢?

2019-11-06 23:17:44

想问下有哪位大神移植过操作系统到FPGA 上的??

2019-04-02 22:28:00

解串器(sERDEs)会增加几瓦功耗,并且使电能输送策略复杂化。当FPGA功耗增加时,对敏感的模拟和混合信号子系统性能的要求也随之增加。其中最重要的是时钟子系统,它们为FPGA和其他板级元件提供低抖动

2018-09-26 14:33:58

在介绍了GPS 同步时钟基本原理和FPGA 特点的基础上,提出了一种基于FPGA 的GPS同步时钟装置的设计方案,实现了高精度同步时间信号和同步脉冲的输出,以及GPS 失步后秒脉冲的平

2009-07-30 11:51:45 45

45 影响FPGA设计中时钟因素的探讨:时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时

2009-11-01 14:58:33 26

26 DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟电路是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 采用FPGA的uClinux移植(IDE)

为什么要在CPU里运行操作系统简单的说就像PC上使用Windows操作系统一样,它负责底层的东西,如各种硬件接口,内存管理,资源分

2010-02-08 15:54:28 56

56 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 提出了一种基于FPGA的时钟跟踪环路的设计方案,该方案简化了时钟跟踪环路的结构,降低了时钟调整电路的复杂度。实际电路测试结果表明,该方案能够使接收机时钟快速准确地跟踪发

2010-11-19 14:46:54 31

31 基于FPGA的高速时钟数据恢复电路的实现

时钟数据恢复电路是高速收发器的核心模块,而高速收发器是通信系统中的关键部分。随着光纤在通信中的应用,信道可以承载

2009-10-25 10:29:45 4637

4637

大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 827

827

基于FPGA的提取位同步时钟DPLL设计

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发

2010-01-25 09:36:18 3699

3699

在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 4131

4131

在Quartus Ⅱ开发环境下,用Verilog HDL硬件描述语言设计了一个可以在FPGA芯片上实现的数字时钟. 通过将设计代码下载到FPGA的开发平台Altera DE2开发板上进行了功能验证. 由于数字时钟的通用

2011-11-29 16:51:43 184

184 FPGA 异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA 异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的

2011-12-20 17:08:35 63

63 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数

2012-05-21 11:26:10 1591

1591

DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 FPGA MC8051移植 100M频率计设计详细步骤

2015-11-05 16:17:15 24

24 低功耗时钟门控算术逻辑单元在不同FPGA中的时钟能量分析

2015-11-19 14:50:20 0

0 系统移植,最近搞这个相关的,所以收集了挂上来分享一下

2016-05-11 17:30:15 0

0 基于FPGA的数字时钟设计,可实现闹钟的功能,可校时。

2016-06-23 17:15:59 71

71 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-02-11 11:34:11 5427

5427 介绍一种采用FPGA(现场可编程门阵列电路)实现SDH(同步数字体系)设备时钟芯片设计技术,硬件主要由1 个FPGA 和1 个高精度温补时钟组成.通过该技术,可以在FPGA 中实现需要专用芯片才能实现的时钟芯片各种功能,而且输入时钟数量对比专用芯片更加灵活,实现该功能的成本降低三分之一.

2017-11-21 09:59:00 2653

2653

介绍了精密时钟同步协议(PTP)的原理。本文精简了该协议,设计并实现了一种低成本、高精度的时钟同步系统方案。该方案中,本地时钟单元、时钟协议模块、发送缓冲、接收缓冲以及系统打时标等功能都在FPGA中

2017-11-17 15:57:18 8779

8779

很大。 在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。

2017-11-25 09:16:01 5020

5020

一般情况下,FPGA器件内部的逻辑会在每个时钟周期的上升沿执行一次数据的输入和输出处理,而在两个时钟上升沿的空闲时间里,则可以用于执行各种各样复杂的处理。而一个比较耗时的复杂运算过程,往往无法一个时钟周期完成,便可以切割成几个耗时较小的运算,然后在数个时钟上升沿后输出最终的运算结果。

2018-05-23 05:56:00 8320

8320

基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟域

2018-09-01 08:29:21 6010

6010

跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟域的数量急剧增加。通常不止数百个,而是超过一千个时钟域。

2019-08-19 14:52:58 3895

3895 时钟是FPGA设计中最重要的信号,FPGA系统内大部分器件的动作都是在时钟的上升沿或者下降沿进行。

2019-09-20 15:10:18 6055

6055

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 3695

3695 。 不要随意将内部信号作为时钟,如门控时钟和分频时钟,而要使用CLKDLL或者DCM产生的时钟,或者可以通过建立时钟使能或者DCM产生不同的时钟信号。 FPGA尽量采取同步设计,也就是所有时钟都是同一个源头,如果使用两个没有相位关系的异步时钟,必须

2020-12-11 10:26:44 2426

2426 对于 FPGA 来说,要尽可能避免异步设计,尽可能采用同步设计。 同步设计的第一个关键,也是关键中的关键,就是时钟树。 一个糟糕的时钟树,对 FPGA 设计来说,是一场无法弥补的灾难,是一个没有打好地基的楼,崩溃是必然的。

2020-11-11 09:45:54 4571

4571 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA中

2020-12-09 14:49:03 21

21 FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

2020-12-09 18:14:00 13

13 本文档的主要内容详细介绍的是FPGA硬件基础之理解FPGA时钟资源的工程文件免费下载。

2020-12-10 14:20:11 6

6 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

2020-12-10 15:00:29 16

16 利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线,本文将对这些设计策略深入阐述。

2021-01-15 15:57:00 14

14 引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。这些网络被设计成具有低偏移和低占空比失真、低功耗和改进的抖动容限。它们也被设计成

2021-03-22 10:09:58 14973

14973

引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源

2021-03-22 10:16:18 6115

6115

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 6070

6070 基于FPGA的数字时钟设计毕业设计论文免费下载。

2021-05-28 10:49:19 75

75 减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2021-09-23 16:39:54 3632

3632 在设计FPGA项目的时候,对时钟进行约束,但是因为算法或者硬件的原因,都使得时钟约束出现超差现象,接下来主要就是解决时钟超差问题,主要方法有以下几点。 第一:换一个速度更快点的芯片,altera公司

2021-10-11 14:52:00 4267

4267

1. 前言作者之前用过GD32芯片,也成功移植过STM32代码到GD32芯片,但最近移植一份STM32代码到GD32后运行的时候发现一个问题:使用内部时钟时一切正常,一旦切换为使用外部12M时钟

2021-12-02 15:36:10 17

17 (10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 (08)FPGA时钟概念1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟概念5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (12)FPGA时钟设计原则1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟设计原则5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 (29)FPGA原语设计(差分时钟转单端时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(差分时钟转单端时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:48 10

10 将ASIC设计移植到FPGA芯片中,对于大部分设计团队来讲都是巨大的挑战。主要体现在:ASIC的设计一般都非常大,往往需要做多FPGA芯片划分;需要支持足够的处理性能;需要保证其功能的正确性;需要保证移植前后的功能具有等价性。

2022-04-14 15:01:08 2806

2806 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 4699

4699 在完成EDA作业后,抽空分享一下如何移植FPGA的例程。我EDA作业用的板子型号是Zybo-Z7,然后移植的是原子哥的HDMI实现方块移动例程。

2022-09-05 15:12:02 2608

2608 电子发烧友网站提供《使用FPGA的数字时钟(计时表).zip》资料免费下载

2022-11-23 10:38:36 7

7 如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-04-07 09:42:57 1705

1705 如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-05-23 15:46:24 1420

1420

时钟是每个 FPGA 设计的核心。如果我们正确地设计时钟架构、没有 CDC 问题并正确进行约束设计,就可以减少与工具斗争的时间。

2023-07-12 11:17:42 1817

1817

基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42:47 1

1 减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2023-08-23 16:10:01 1372

1372 确定算法:首先,你需要确保要移植的C语言算法是合适的。FPGA适合并行计算和高度可定制的应用。因此,你需要选择一个适合FPGA实现的算法。

2023-09-12 17:20:58 3156

3156 fpga跨时钟域通信时,慢时钟如何读取快时钟发送过来的数据? 在FPGA设计中,通常需要跨时钟域进行数据通信。跨时钟域通信就是在不同的时钟域之间传输数据。 当从一个时钟域传输数据到另一个时钟域

2023-10-18 15:23:51 1901

1901 fpga与dsp通讯怎样同步时钟频率?dsp和fpga通信如何测试? 在FPGA与DSP通讯时,同步时钟频率非常重要,因为不同的设备有不同的时钟频率,如果两者的时钟频率不同步,会导致通讯数据的错误或

2023-10-18 15:28:13 2793

2793 FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢? FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据不同需要编程,实现不同的功能。在FPGA中

2023-10-25 15:14:20 2400

2400 如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 3484

3484

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。

2023-10-30 11:47:55 2892

2892

FPGA输入的时钟信号必须是方波么?正弦波会有影响么? FPGA是一种可编程逻辑器件,通常用于实现数字电路。输入时钟信号是FPGA中非常重要的时序信号,对整个系统的稳定性和性能都有很大影响。在

2024-01-31 11:31:42 5410

5410 FPGA 中包含一些全局时钟资源。以AMD公司近年的主流FPGA为例,这些时钟资源由CMT(时钟管理器)产生,包括DCM、PLL和MMCM等。

2024-04-25 12:58:30 3304

3304

在FPGA(现场可编程门阵列)设计中,消除时钟抖动是一个关键任务,因为时钟抖动会直接影响系统的时序性能、稳定性和可靠性。以下将详细阐述FPGA中消除时钟抖动的多种方法,这些方法涵盖了从硬件设计到软件优化的各个方面。

2024-08-19 17:58:54 3753

3753

电子发烧友App

电子发烧友App

评论