fpga跨时钟域通信时,慢时钟如何读取快时钟发送过来的数据?

在FPGA设计中,通常需要跨时钟域进行数据通信。跨时钟域通信就是在不同的时钟域之间传输数据。

当从一个时钟域传输数据到另一个时钟域时,由于时钟频率不同,所以可能会产生元件的不稳定情况,导致传输数据的错误。此时我们需要采取一些特殊的措施,来保证跨时钟域传输的正确性。

FPGA跨时钟域通信的基本实现方法是通过FPGA内部专门的逻辑元件进行数据传输。发送方用一个逻辑电路将数据从发送时钟域转换到接收时钟域的信号,接收方再用另一个逻辑电路将数据从接收时钟域转换到发送时钟域的信号,以保证数据的正确性。

对于慢时钟如何读取快时钟发送过来的数据,通常可以采用一下两种方式:

(1) 阻塞方式

在这种方式下,慢时钟需要等待快时钟传输完数据后才能进行读取。此时,发送方等待接收方读取完数据后再向输出端发送下一批数据,保证在不同时钟域之间数据传输的正确性。

(2) FIFO缓存方式

在这种方式下,我们使用一个先进先出(FIFO)缓存器来存储从快时钟产生的数据。FIFO缓存器可以用来解决发送方和接收方在时钟频率不等的情况下进行数据传输的问题。

FIFO缓存器有一个读指针和一个写指针,读指针和写指针都在接收时钟域。当发送方向FIFO缓存器写入新数据时,写指针会指向新的写入数据的位置。当接收方需要读取数据时,读指针会指向最早写入的数据位置。这个FIFO缓存器会将发送的数据存储在缓存器中,然后在接收方时钟域内读出。

为了保证FIFO缓存器能在不同时钟域下进行正常的数据传输,我们可以采用异步双字节读取和写入技术。即在写入或读取数据时,每一次传输需要在发送方和接收方时钟域中各进行一次同步和异步操作。

总之,正确地实现FPGA跨时钟域通信是非常重要的,在实际设计中,需要结合实际情况,选择合适的方案来处理跨时钟域通信。

-

FPGA设计

+关注

关注

9文章

431浏览量

28214 -

fifo

+关注

关注

3文章

407浏览量

45909 -

缓存器

+关注

关注

0文章

63浏览量

12088

发布评论请先 登录

浅谈FPGA的时钟输入要求

LMK04000 系列时钟抖动清理器:高精度时钟解决方案深度剖析

时钟设计优化实战

精准时钟,驱动未来 ----澜起科技发布多款高性能时钟芯片

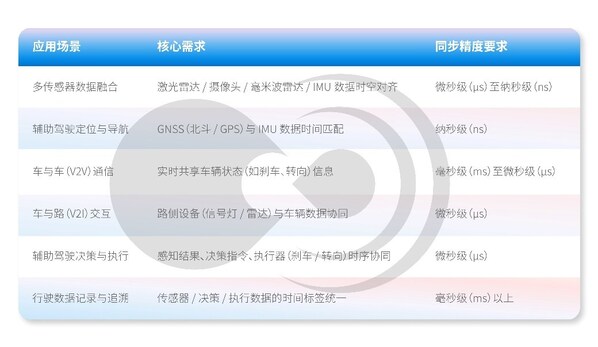

黑芝麻智能跨域时间同步技术:消除多域计算单元的时钟信任鸿沟

跨异步时钟域处理方法大全

fpga跨时钟域通信时,慢时钟如何读取快时钟发送过来的数据?

fpga跨时钟域通信时,慢时钟如何读取快时钟发送过来的数据?

评论