1 IDDR

Primitive: Input Dual Data-Rate Register

1.1 介绍

该设计元素是专用的输入寄存器,旨在将外部双数据速率(DDR)信号接收到Xilinx FPGA中。IDDR可用的模式可以在捕获数据的时间和时钟沿或在相同的时钟沿向FPGA架构显示数据。此功能使您可以避免其他时序复杂性和资源使用情况。

1)OPPOSITE_EDGE模式-以传统的DDR方法恢复数据。给定分别在引脚D和C上的DDR数据和时钟,在时钟C的每个上升沿之后Q1发生变化,在时钟C的每个下降沿之后Q2发生变化。

2)SAME_EDGE模式-时钟C的相对边沿仍然恢复数据。但是,在负边沿数据寄存器后面放置了一个额外的寄存器。这个额外的寄存器由时钟信号C的正时钟沿提供时钟。结果,现在DDR数据在相同的时钟沿提供给FPGA架构。但是,由于此功能,数据对似乎是“分离的”。Q1和Q2不再具有对1和2。相反,出现的第一个对是对1和DONT_CARE,在下一个时钟周期之后是对2和3。

3)SAME_EDGE_PIPELINED模式-以与SAME_EDGE模式类似的方式恢复数据。为了避免SAME_EDGE模式的“分离”效应,在上升沿数据寄存器的前面放置了一个额外的寄存器。现在,数据对同时出现在Q1和Q2引脚上。但是,使用此模式将使Q1和Q2信号更改的延迟时间增加一个额外的周期。

1.2 Verilog Instantiation Template

// IDDR: Input Double Data Rate Input Register with Set, Reset

// and Clock Enable.

// 7 Series

// Xilinx HDL Libraries Guide, version 14.7

IDDR #(

.DDR_CLK_EDGE(“OPPOSITE_EDGE”), // “OPPOSITE_EDGE”, “SAME_EDGE”

// or “SAME_EDGE_PIPELINED”

.INIT_Q1(1‘b0), // Initial value of Q1: 1’b0 or 1‘b1

.INIT_Q2(1’b0), // Initial value of Q2: 1‘b0 or 1’b1

.SRTYPE(“SYNC”) // Set/Reset type: “SYNC” or “ASYNC”

) IDDR_inst (

.Q1(Q1), // 1-bit output for positive edge of clock

.Q2(Q2), // 1-bit output for negative edge of clock

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D(D), // 1-bit DDR data input

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

// End of IDDR_inst instantiation

1.3端口描述

1.4 可用属性

编辑:lyn

-

寄存器

+关注

关注

31文章

5619浏览量

130397 -

DDR

+关注

关注

11文章

761浏览量

69543 -

Xilinx FPGA

+关注

关注

1文章

29浏览量

7388

原文标题:xilinx源语 IDDR和ODDR

文章出处:【微信号:leezym0317,微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

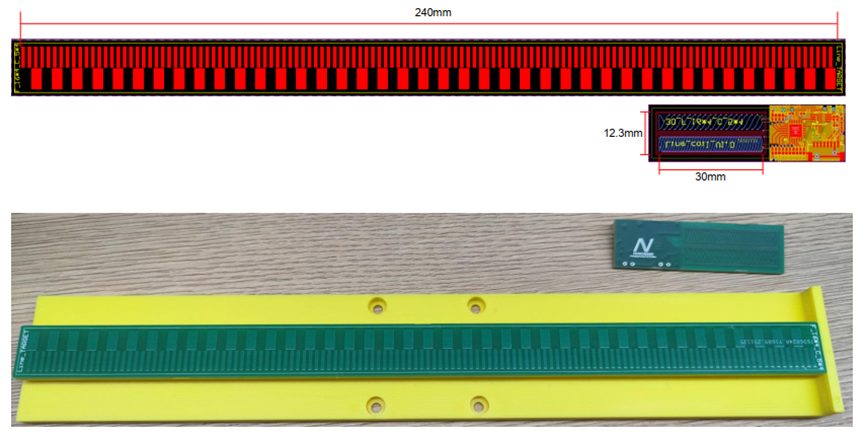

Azukar-FPGA开源FPGA教育开发板介绍

Xilinx FPGA串行通信协议介绍

关于系统链接脚本的介绍

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

基于FPGA开发板TSP的串口通信设计

AI狂飙, FPGA会掉队吗? (中)

西门子桌面级原型验证系统Veloce proFPGA介绍

同步电机失步浅析

智多晶FPGA设计工具HqFpga接入DeepSeek大模型

Altera Agilex 3 FPGA和SoC产品介绍

关于IDDR与FPGA的介绍与浅析

关于IDDR与FPGA的介绍与浅析

评论