上一篇文章已经讲过了单bit跨时钟域的处理方法,这次解说一下多bit的跨时钟域方法:

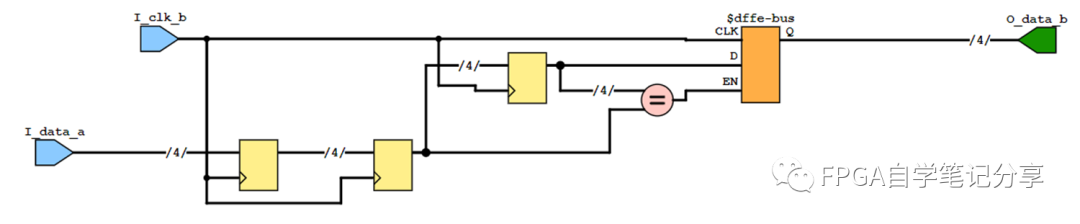

1、打两拍,比较,具体代码如下所示。

// ============================================================

// File Name: cm_cdc_4bit

// VERSION : V1.0

// DATA : 2022/9/28

// Author : FPGA干货分享

// ============================================================

// 功能:4bit慢变信号跨时钟域模块

// ============================================================

`timescale 1ns/1ps

module cm_cdc_4bit (

input wire I_clk_a , ///输入时钟a

input wire I_clk_b , ///输入时钟b

input wire [3:0] I_data_a , ///a时钟输入信号

output reg [3:0] O_data_b ///b时钟输出信号

);

// ============================================================

// wire reg

// ============================================================

reg [3:0] S_data_b_d0 ;

reg [3:0] S_data_b_d1 ;

reg [3:0] S_data_b_d2 ;

// ============================================================

// a时钟域

// ============================================================

// ============================================================

// b时钟域

// ============================================================

///使用第二个时钟进行打拍

always @(posedge I_clk_b)

begin

S_data_b_d0 <= I_data_a ;

S_data_b_d1 <= S_data_b_d0 ;

S_data_b_d2 <= S_data_b_d1 ;

end

//打两拍之后的信号进行处理

always @(posedge I_clk_b)

if(S_data_b_d2 == S_data_b_d1)

O_data_b <= S_data_b_d2;

else

O_data_b <= O_data_b ;

endmodule

第二种方法就是计数器转gray码。

下一篇将为大家讲解格雷码与二进制码的转换代码及仿真。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1655文章

22281浏览量

630051 -

信号

+关注

关注

11文章

2901浏览量

79652 -

计数器

+关注

关注

32文章

2306浏览量

97554 -

bit

+关注

关注

0文章

48浏览量

32744 -

时钟域

+关注

关注

0文章

53浏览量

9986

发布评论请先 登录

相关推荐

热点推荐

FPGA跨时钟域处理方法(二)

FPGA跨时钟域处理方法(二)

评论