全球电子设计创新企业Cadence设计系统公司日前宣布其与TSMC在3D IC设计基础架构开发方面的合作。

2012-06-11 09:47:43 1071

1071 Cadence设计系统公司,在TSMC最近举办的Open Innovation Platform Ecosystem Forum上因DRAM接口IP和技术方面的相关论文而获得“客户首选奖”

2013-01-30 09:08:27 842

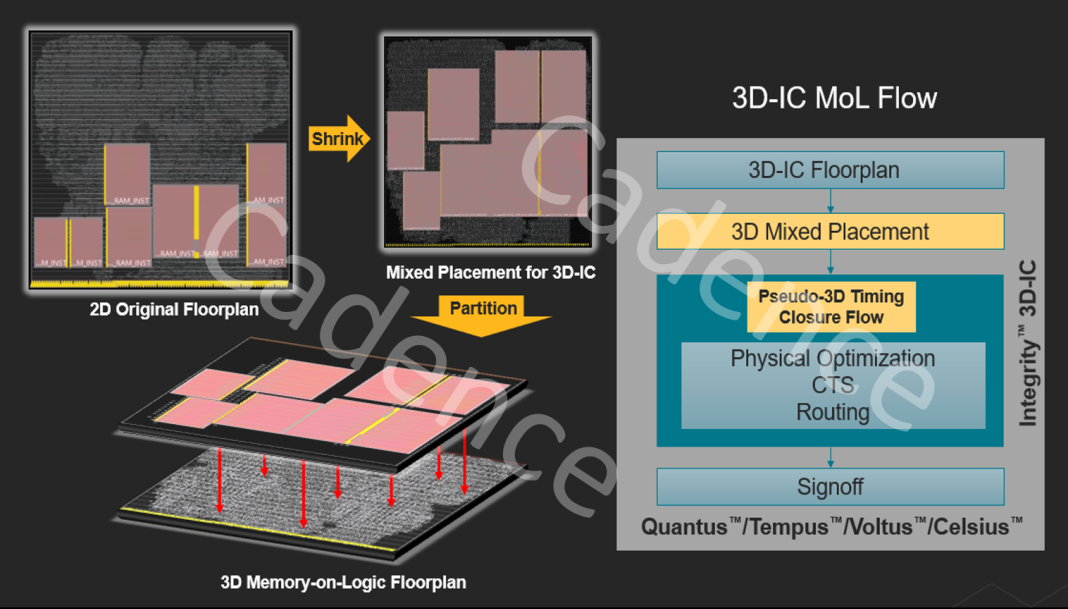

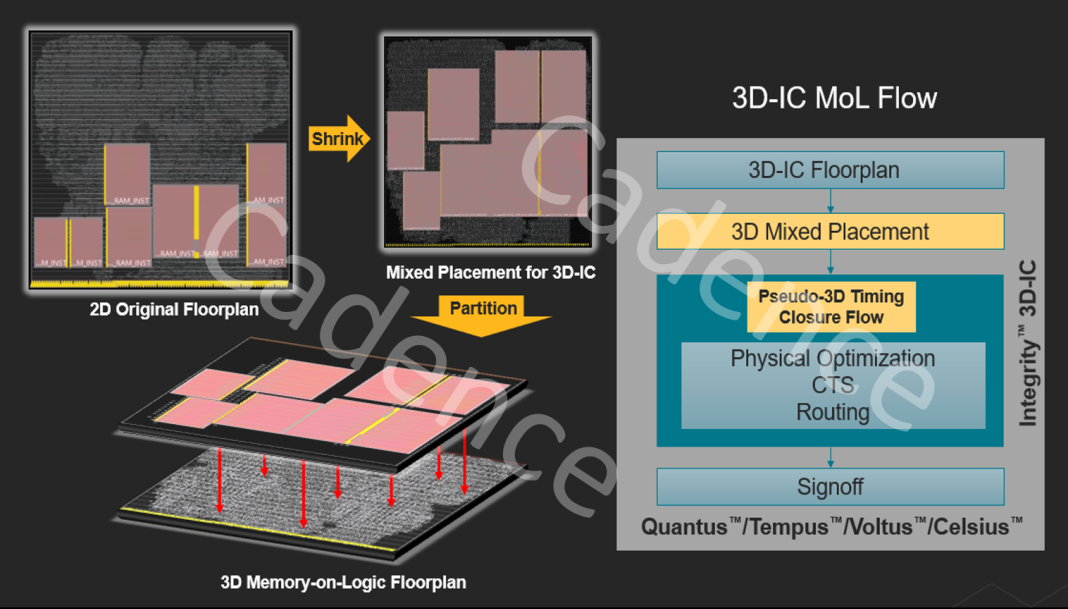

842 Cadence Integrity 3D-IC 平台是业界首个全面的整体 3D-IC 设计规划、实现和分析平台,以全系统的视角,对芯片的性能、功耗和面积 (PPA) 进行系统驱动的优化,并对 3D-IC 应用的中介层、封装和印刷电路板进行协同设计。

2022-05-23 17:13:53 4218

4218 Integrity 3D-IC 平台具有强大的数据管理功能,能够实现跨团队的一键数据同步与更新。同时,Integrity 3D-IC 支持灵活的 3D-IC 实现流程,配合其高效的数据管理机制,可以让用户在流程中的多个关键阶段接入内嵌的分析平台,进而实现整个系统的快速迭代和 ECO。

2022-07-19 09:34:44 1442

1442

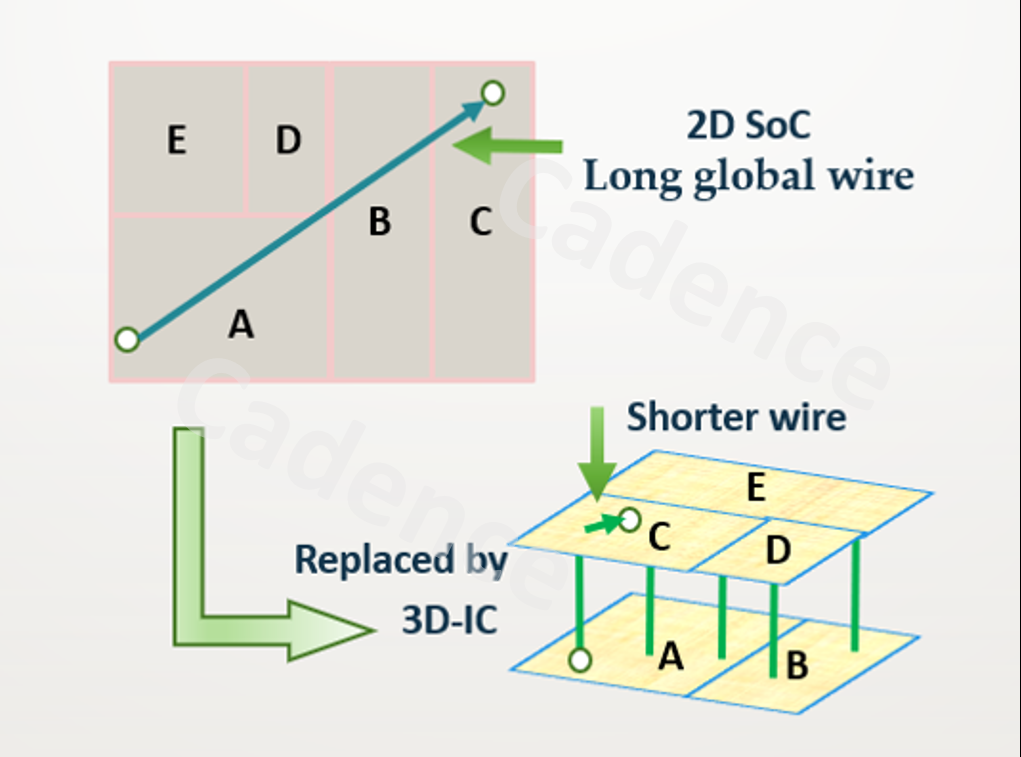

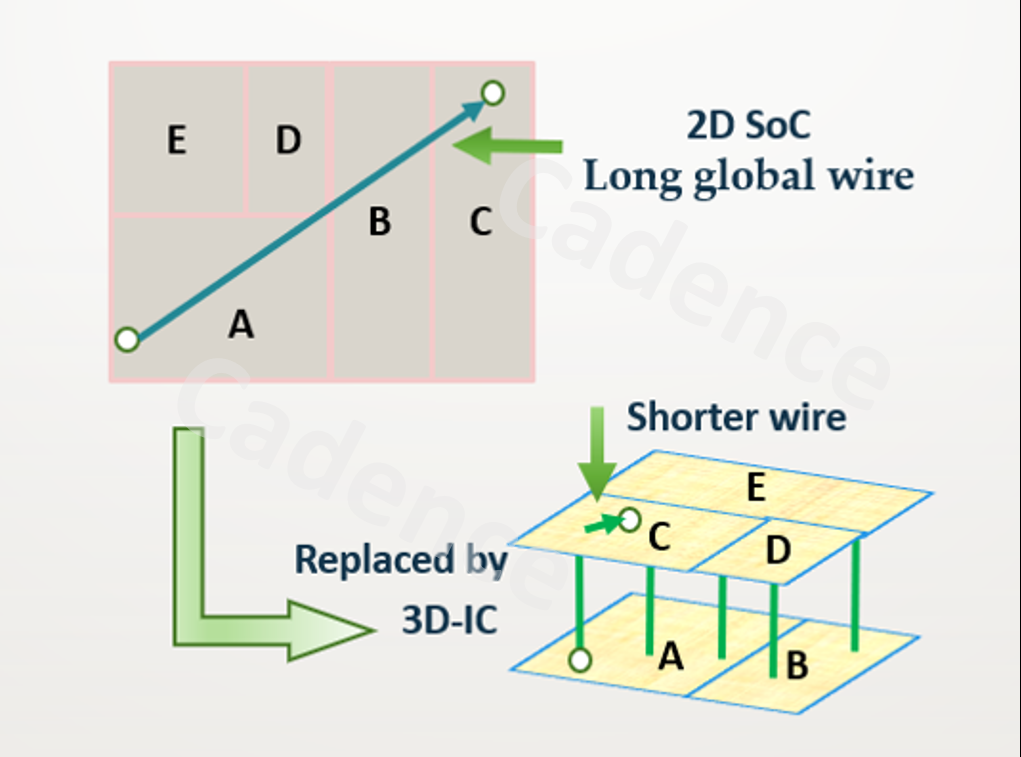

随着芯片工艺尺寸的缩小趋于饱和或停滞,设计师们现在专注于通过 3D-IC 异构封装,在芯片所在平面之外的三维空间中构建系统。3D-IC 异构封装结构可能包括多个芯片,它们被放置在一个通用的中介层上,或者通过芯片内部的高级互连来集成内存单元、处理器和其他功能模块。

2022-12-09 11:02:18 3231

3231 这是一个业界用于打造差异化定制芯片的领先平台,可借助生成式 AI 技术显著提升设计生产力; Virtuoso Studio 与 Cadence 最前沿的技术和最新的底层架构集成,助力设计工

2023-04-20 15:52:13 508

508

3nm 时代来临了!Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示,这是

2023-05-19 16:25:12 784

784

、无废弃副产品等特性在汽车某些关键精巧零部件的制造方面更加方便、快速和高效。而这一技术在汽车行业的应用,机遇远大于挑战。为顺应市场需求,在各主管部门的支持下,2020中国(北京)国际3D打印与汽车智造

2019-12-20 16:11:32

3D Experience — 产品协同研发平台

2021-01-08 07:30:52

`2D工程图纸,难以高效转化成3D模型数据?多CAD格式混合设计,难以进行标准化?大量旧版本图纸堆积,难以实现数据重用?浩辰3D制图软件不仅具备支持主流3D原生和通用文件的导入,对数据进行直接编辑

2021-02-24 17:22:41

3D显示技术的原理是什么?3D显示技术有哪些应用?3D拍好了到底怎么样传输?

2021-05-31 06:53:03

各类显示和消费电子产品提供具有业界领先水平的视频技术及方案。易维视拥有长期的3D技术算法积累,在动态背光、超解析、频率转换和超多试点方面有技术领先。其中多视点转换是裸眼3D平板的关键技术。多视点

2020-11-27 16:17:14

Cadence设计系统公司发布了Cadence Allegro系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和技术增强。改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2018-11-23 17:02:55

设计,并与封装设计团队和使用Cadence Allegro® 封装技术的外包半导体组装和测试 (OSAT) 公司进行无缝协同设计。 使用 Integrity 3D-IC 平台的客户可以获得以下功能和优势

2021-10-14 11:19:57

具包与CadenceRFSiPMethodologyKit整合,Jazz在优化RFSiP设计周期方面为Cadence提供支持,从而为我们共同的客户提供更好的性能和技术,以及更快的产品上市周期。 CadenceSiP解决方案也

2008-06-27 10:24:12

Cadence设计系统公司发布Cadence®Allegro®系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和技术增强.改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2018-08-28 15:28:45

Cadence设计系统公司发布Cadence?Allegro?系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和技术增强.改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2008-06-19 09:36:24

IC设计Cadence 2018设计笔试题Choice Questions1. What is theminimum number of flip flops to implement a

2018-12-28 10:20:26

多视角裸眼3D显示器技术发展和市场动态

2012-08-17 13:48:00

`FTDI发布支持Android平台的 USB Host/slave IC--UART GPIO SPI I2C先进的单片USB主控桥接器并支持各种标准接口英商飞特蒂亚公司(FTDI)继续推进安卓

2013-01-10 17:32:34

`FTDI发布支持Android平台的 USB Host/slave IC--UART GPIO SPI I2C先进的单片USB主控桥接器并支持各种标准接口英商飞特蒂亚公司(FTDI)继续推进安卓

2013-01-10 17:43:45

赫、RF与SiP/3D-IC流程。Allegro产品提供了一个可升级的PCB与IC封装设计解决方案,利用一种约束与规则驱动型方法学,从逻辑设计授权到物理实现再到信号与功率的完整性分析。 最新系统级

2020-07-06 17:50:50

`FTDI发布支持Android平台的 USB Host/slave IC先进的单片USB主控桥接器并支持各种标准接口英商飞特蒂亚公司(FTDI)继续推进安卓开源配件的创新,推出FT311D。这款

2013-04-01 18:00:31

`FTDI发布支持Android平台的 USB Host/slave IC--UART GPIO SPI I2C先进的单片USB主控桥接器并支持各种标准接口英商飞特蒂亚公司(FTDI)继续推进安卓

2013-03-08 17:18:20

`FTDI发布支持Android平台的 USB Host/slave IC--UART GPIO SPI I2C先进的单片USB主控桥接器并支持各种标准接口英商飞特蒂亚公司(FTDI)继续推进安卓

2013-03-08 17:28:32

我用的是cadence 16.3的版本,用Model Integrity这个软件模块进行IBIS转DML时总是报错,提示无法打开“ibis2signoise”;还有就是查看IBIS文件的曲线时,软件出错,然后就自动关闭了。求哪位大神指点迷津。

2011-12-24 13:34:57

://t.elecfans.com/live/1043.html 各位小伙伴大家好,Cadence Allegro 软件一直以来,都能够支持3D PCB的模型制作和预览功能,但是一直以来立体感和视角的效果都不

2019-11-22 13:45:11

本文是电子发烧友学院讲师李增老师(@wareleo)经验分享,希望能与工程师一起交流探讨各位小伙伴大家好,Cadence Allegro 软件一直以来,都能够支持3D PCB的模型制作和预览功能

2019-11-22 13:49:25

的错误日志 1. iMX8QM安卓平台支持3D游戏吗?2. 如果是,是否需要额外添加一些东西才能启用 3D 游戏?

2023-04-04 07:42:57

当3D电影已成为影院观影的首选,当3D打印已普及到双耳无线蓝牙耳机,一种叫“3D微波”的技术也悄然而生。初次听到“3D微波”,你可能会一脸茫然,这个3D微波是应用在哪个场景?是不是用这种技术的微波炉1秒钟就能把饭煮熟?O M G!我觉得很有必要给大家科普一下!

2019-07-02 06:30:41

(INT8)稠密算力。启明930可独立用于AI加速卡,亦可通过D2D扩展多种功能型Side Die进行集成,具备多种产品形态。北极雄芯由清华大学姚期智院士创建的交叉信息核心技术研究院自2018年起孵化

2023-02-21 13:58:08

从最近很多新闻上可以看到,3D打印与医疗和生物行业的结合越来越紧密。医疗行业也在不断加紧引入全新的3D打印技术来辅助完成各种手术和一些高难度医学工作。最近,华森科技研发了一款专业适用于医疗行业的3D打印机,谁知道这款医疗3D打印机到底有多厉害吗?

2019-08-02 07:04:30

本帖最后由 gk320830 于 2015-3-4 19:06 编辑

在cadence ic版图设计中tsmc.18,宽长比4/0.18的mosfet怎么画?有多少层?每一层什么意义?

2014-10-06 08:07:57

,降低武器装备成本,提高维修保障时效性与精度。在世界各国的广泛关注与大力推进下,近年来3D打印技术的发展与应用不断取得突破,显示了良好的军事应用前景,将对武器装备的发展产生深远影响。

2019-07-16 07:06:28

3D 音频。 OpenSL ES 可在从智能手机和先进移劢设备到上代低端移劢硬件设计中应用。无关于其所部署的平台,OpenSL ES 提供普适的通用接口 API,从而使任何设备均可达到其硬件支持的最优

2011-03-08 21:41:21

怎么实现基于SL3IC3001芯片的UHF频段RFID多应用天线的设计?

2021-05-26 06:39:31

本文是电子发烧友学院讲师李增老师(@wareleo)经验分享,希望能与工程师一起交流探讨各位小伙伴大家好,Cadence Allegro 软件一直以来,都能够支持3D PCB的模型制作和预览功能

2019-11-21 17:31:52

3D视觉技术有何作用?常见的3D视觉方案主要有哪些?

2021-11-09 07:46:56

3D打印技术是综合了三维数字技术、控制技术、信息技术众多技术的创新研发技术,具有设计样式多元化、试制成本低、制作材料丰富等特点。通过数字化设计工具+3D打印技术相结的模式,可以帮助企业高效实现创新

2021-05-27 19:05:15

的节点。3D封装引发新的竞争 除了晶体管结构走向了3D以外,封装技术也在向3D方向发展。有报道指出,用先进封装技术提供的高密度互联将多颗Chiplet包在同一个封装体内,将是未来的发展趋势。而在这其中

2020-03-19 14:04:57

请问怎样理解3D ICs技术之变?

2021-06-18 07:20:20

众所周知,Cadence allegro 16.x 版本已经拥有3D view,虽然比较简单,但是总之还不错,近年以来Cadence公司在不断的加强 PCB Editor三维的显示能力,可以帮助

2019-06-07 08:00:00

`FTDI发布支持Android平台的 USB Host/slave IC-UART/I2C/GPIO/SPI先进的单片USB主控桥接器并支持各种标准接口英商飞特蒂亚公司(FTDI)继续推进安卓开源

2013-06-18 16:52:36

商迪3D

2021-11-22 09:26:58

普密斯3D轮廓测量仪方案 3D GMS Pro,拥有高速移动测量平台,兼容多类型传感器,为客户需求提供快速、强力的技术支持! 产品特点—— 高速移动测量平台龙门架

2023-07-28 15:42:53

SpringSoft Laker定制版图系统支持TSMC跨平台制程设计套件

IC设计软件全球供货商SpringSoft, Inc.近日宣布,Laker定制版图自动化系统(Custom Layout Automation Syste

2009-07-30 08:11:20 1005

1005 本章是Cadence IC 5.1.41 是设计 的简明入门教程,目的是让读者在刚接触该软件的时候对它的基本功能有一个总体的了解。本章主要内容如下:[1] 启动Cadence IC 前的准备;[2]Command Interpret

2011-12-02 16:56:58 158

158 新思科技 (Synopsys)今日宣布利用3D-IC整合技术加速多晶片堆叠系统 (stackedmultiple-die silicon system)的设计

2012-03-28 08:57:44 719

719 全球电子设计创新领先企业Cadence设计系统公司日前宣布TSMC已选择Cadence解决方案作为其20纳米的设计架构。Cadence解决方案包括Virtuoso定制/模拟以及Encounter RTL-to-Signoff平台。

2012-10-22 16:48:03 909

909 电子发烧友网讯: TSMC授予Cadence两项年度合作伙伴奖项,两项大奖表彰Cadence在帮助客户加快设计的3D-IC CoWoS技术与20纳米参考流程方面的重要贡献。 TSMC授予全球电子设计创新领先企业

2012-11-07 11:48:07 928

928 Cadence教程:基于Cadence的IC设计

2013-04-07 15:46:14 0

0 为专注于解决先进节点设计的日益复杂性,全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布,台积电已与Cadence在Virtuoso定制和模拟设计平台扩大合作以设计和验证其尖端IP。

2013-07-10 13:07:23 842

842 基于Wide I/O接口的3D堆叠,在逻辑搭载存储器设计上进行了验证 ,可实现多块模的整合。它将台积电的3D堆叠技术和Cadence®3D-IC解决方案相结合,包括了集成的设计工具、灵活的实现平台,以及最终的时序物理签收和电流/热分析。

2013-09-26 09:49:20 1346

1346 Integrity Solution),提供卓越性能的电源分析以满足下一代芯片设计的需要。Voltus™ IC电源完整性解决方案利用独特的新技术并结合Cadence® IC、Package、PCB和系统工具使设计团队在整个产品开发周期更好地管理芯片设计的电源问题,以取得更快的设计收敛。

2013-11-13 16:13:50 1323

1323 7-nm FinFET Plus工艺的极紫外光刻技术,IC Compiler II 进行了专门的优化,进一步节省芯片面积。 采用TSMC的Wafer-on-Wafer(WoW)技术,平台内全面支持

2018-05-17 06:59:00 4461

4461 关键词:CoWoS , WoW , 先进封装 新思科技(Synopsys)宣布,新思科技Design Platform全面支持TSMC WoW直接堆叠和 CoWoS先进封装技术。Design

2018-10-27 22:14:01 346

346 对全新芯片堆叠技术的全面支持确保实现最高性能的3D-IC解决方案

2019-05-18 11:28:01 3642

3642 近日,芯原股份在接受机构调研时表示,Chiplet 带来很多新的市场机遇,公司作为具有平台化芯片设计能力的 IP 供应商,已经开始推进对Chiplet的布局,开始与全球领先的晶圆厂展开基于5nm

2021-01-08 12:57:56 2579

2579 业界首款应用于多个小芯片(multi-chiplet)设计和先进封装的完整 3D-IC平台。

2021-10-08 10:29:05 970

970 )宣布,其数字和定制/模拟流程已获得 TSMC N3 和 N4 工艺技术认证,支持最新的设计规则手册(DRM)。通过持续合作,Cadence 和 TSMC 发布了 TSMC N3 和 N

2021-10-26 15:10:58 1928

1928 新思科技3DIC Compiler是统一的多裸晶芯片设计实现平台,无缝集成了基于台积公司3DFabric技术的设计方法,提供完整的“探索到签核”的设计平台

2021-11-01 16:29:14 371

371 双方合作涵盖新思科技的Interface IP、基于TSMC 3DFabric™的设计解决方案以及针对台积公司N4制程技术的PPA优化。

2021-11-08 11:54:45 445

445 创建逻辑内存器件的 3D 堆叠配置,优化 3D 堆叠设计的 PPA 结果。 客户可以放心采用 Cadence Integrity 3D-IC 平台和 Samsung Foundry 的多 Die 实现

2021-11-19 11:02:24 3347

3347 研讨会”。作为 2022 年第一场线下研讨会,Cadence将集聚相关软件开发者与资深技术专家,与各位客户朋友们分享关于 Cadence 3D-IC Integrity 平台在统一环境中提供 3D

2022-01-04 08:56:51 1420

1420 电子设计自动化领域领先的供应商 Cadence,诚邀您参加将于2022 年 1 月 20 日于上海浦东嘉里酒店举办的“2022 CadenceCONNECT: 3D-IC 设计与全系统解决方案-上海研讨会”。

2022-01-20 11:11:42 1533

1533 Chiplet Interconnect Express)产业联盟。作为中国大陆首批加入该组织的企业,芯原将与UCIe产业联盟其他成员共同致力于UCIe 1.0版本规范和新一代UCIe技术标准的研究与应用,为芯原Chiplet技术和产品的发展进一步夯实基础。

2022-04-02 11:47:55 1251

1251 Cadence Integrity 3D-IC 平台是业界首个全面的整体 3D-IC 设计规划、实现和分析平台,以全系统的视角,对芯片的性能、功耗和面积 (PPA) 进行系统驱动的优化,并对 3D-IC 应用的中介层、封装和印刷电路板进行协同设计。

2022-05-23 16:52:50 1594

1594

基于Cadence的IC设计

2022-05-31 17:11:24 0

0 2.5D/3D-IC 目前常见的实现是基于中介层的 HBM-CPU/SOC 设计,Integrity 3D-IC 将以日和周为单位的手动绕线加速到秒级和分钟级,轻松满足性能、信号电源完整性与设计迭代的多重要求,为高带宽高数据吞吐量的机器学习、超算、高性能移动设备、端计算等应用提供最佳设计支持。

2022-06-13 14:14:54 2037

2037 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence® 射频集成电路解决方案支持 TSMC 的 N6RF 设计参考流程和制程设计套件(PDK),加速推进移动、5G 及无线应用创新。

2022-06-22 16:34:01 1774

1774 设计。得益于两家企业的持续合作,使用 Cadence Integrity 3D-IC 平台的参考流程现已启用,以推进 Samsung Foundry 的 3D-IC 设计方法。使用 Cadence 平台

2022-10-25 11:05:04 621

621 包含在台积电3Dblox Reference Flow中的RedHawk-SC和RedHawk-SC Electrothermal,能够使用台积电3DFabric技术实现电源完整性和热可靠性设计签核

2022-11-02 14:19:48 461

461 随着 N3E、N4P 和 3DFabric 工艺的发布,新的独特设计要求要求进行新的认证,以确保同时满足设计人员的系统要求和 TSMC 的工艺要求,从而缩短上市时间。

2022-11-07 14:17:59 1080

1080 此次获奖的 Integrity 3D-IC 平台是 Cadence 于 2021 年 10 月推出的突破性产品,它是业界首款完整的高容量 3D-IC 平台,可将设计规划、物理实现和系统分析统一集成于单个管理界面中。在面向日益复杂的超大规模计算、消费电子、5G 通信、移动和汽车应用设计时

2022-11-11 10:19:49 549

549 、基于云的生产力解决方案和 DSP IP 方面取得的出色成果。此外,Cadence 也被认定为 TSMC 3DFabric 联盟的创始成员之一。

2022-12-14 11:42:34 1152

1152 不知不觉间,行业文章和会议开始言必称chiplet —— 就像曾经的言必称AI一样。这种热度对于3D-IC的从业人员,无论是3D-IC制造、EDA、还是3D-IC设计,都是好事。但在我们相信3D-IC之路是Do Right Things的同时,如何Do Things Right也愈发重要。

2022-12-16 10:31:00 808

808 半导体行业中的第一个联盟,它与合作伙伴联手加速3D IC生态系统的创新和准备,为半导体设计、内存模块、衬底技术、测试、制造和封装提供全方位的最佳解决方案和服务。这一联盟将帮助客户快速实现硅和系统级的创新,并利用台积电的3DFabric技术(一个全面的3D硅堆叠

2022-12-19 17:57:02 662

662 联华电子(NYSE:UMC;TWSE:2303)与楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日共同宣布,采用 Integrity 3D-IC 平台的 Cadence 3D-IC 参考工作流程已通过联电的芯片堆栈技术认证,将进一步缩短产品上市时间。

2023-02-03 11:02:23 1417

1417 Cadence 的低功耗、3D-IC 和人工智能 / 机器学习(AI / ML)技术可支持超大规模计算的数据之旅 —— 从存储和传输,到传感器和设备的数据处理要求;从近 / 远边缘处理,到本地云数据中心的工作负载优化计算。

2023-02-21 18:16:42 618

618 台积电 3DFabric™ CoWoS-S 硅中介层技术实现,可提供超高的带宽密度、高效的低功耗性能和卓越的低延迟,非常适合需要极高算力的应用。Cadence UCIe IP 为Chiplet裸片到裸片通信

2023-04-27 16:35:40 453

453

该 IP 采用台积电 3DFabric™ CoWoS-S 硅中介层技术实现,可提供超高的带宽密度、高效的低功耗性能和卓越的低延迟

2023-04-28 15:14:12 811

811 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Integrity 3D-IC 平台的新设计流程,以支持 TSMC 3Dblox 标准。TSMC

2023-05-09 09:42:09 615

615 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 数字和定制/模拟设计流程已通过 TSMC N3E 和 N2 先进工艺的设计规则手册(DRM)认证。两家公司还发

2023-05-09 10:09:23 708

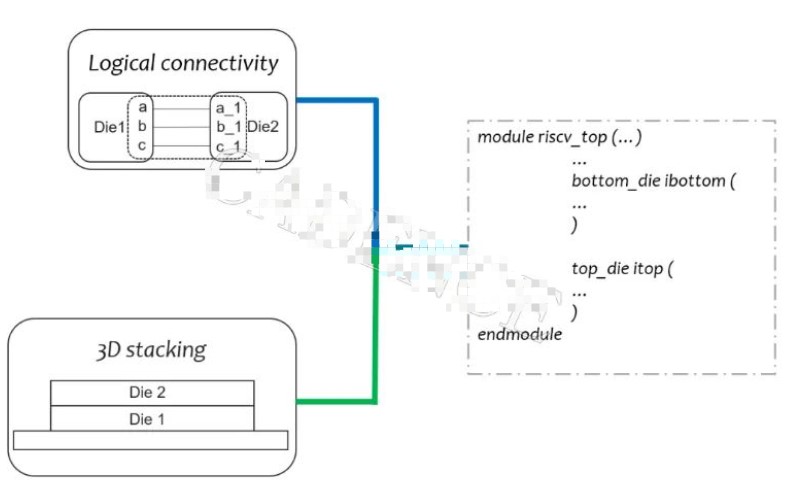

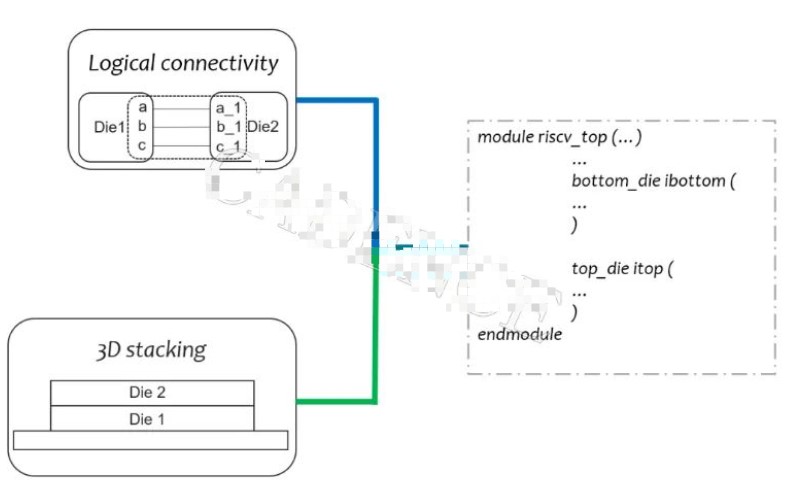

708 随着业界对增加晶体管密度、增加带宽和降低功耗的需求越来越迫切,许多IC设计和封装团队都在深入研究如何增加垂直堆叠多个芯片裸片(die)和小芯片(chiplet)的方案。这种被称为3D-IC的技术有望

2022-01-06 14:05:18 249

249

本文作者:许立新Cadence公司DSGProductValidationGroup随着3D-IC的制造工艺的不断发展,3D-IC的堆叠方式愈发灵活,从需要基板作为两个芯片互联的桥梁,发展到如今可以

2022-07-24 16:25:41 491

491

平台支持 Samsung 新的 3D CODE 标准,助力设计人员创建多种先进的封装技术。 ❖ Cadence 和 Samsung 的技术为客户提供全面、定制化的解决方案。适用于能够缩短 3D-IC

2023-07-06 10:05:04 329

329 ● AI 驱动的 Cadence Virtuoso Studio 助力 IC 设计在 TSMC 的制程技术之间实现迁移时自动优化电路 ● 新的生成式设计技术可将设计迁移时间缩短

2023-09-27 10:10:04 301

301 内容提要 ● Cadence Integrity 3D-IC 平台现已全面支持最新版 3Dblox 2.0 标准,涵盖 TSMC 的 3DFabric 产品 ● Integrity 3D-IC

2023-10-08 15:55:01 249

249 基于Cadence的IC设计

2022-12-30 09:21:19 6

6 3D-IC 中 硅通孔TSV 的设计与制造

2023-11-30 15:27:28 212

212

3D-IC 设计之 Memory-on-Logic 堆叠实现流程

2023-12-01 16:53:37 255

255

3D-IC 设计之早期三维布图综合以及层次化设计方法

2023-12-04 16:53:58 200

200

Chiplet,又称芯片堆叠,是一种模块化的半导体设计和制造方法。由于集成电路(IC)设计的复杂性不断增加、摩尔定律的挑战以及多样化的应用需求,Chiplet技术应运而生。

2024-01-23 10:49:37 351

351

Cadence Allegro® X APD(用以实现元件布局、信号/电源/接地布线、设计同步电气分析、DFM/DFA及最后制造输出)、Integrity™ 3D-IC Platform 及其对应的Integrity System Planner(负责系统级设计聚合、规划和优化)

2024-03-13 10:05:40 130

130 本文要点缩小集成电路的总面积是3D-IC技术的主要目标。开发3D-IC的传热模型,有助于在设计和开发的早期阶段应对热管理方面的挑战。开发3D-IC传热模型主要采用两种技术:分析法和数值计算法。传统

2024-03-16 08:11:28 52

52

电子发烧友App

电子发烧友App

评论