我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。

跨时钟域处理技术是IC设计中非常重要的一个部分,我们需要学习并应用一些常用的处理方法,从而提高电路运行的稳定性,使得整个系统更鲁棒。

下面考虑ASIC设计场景,为了满足系统功能需求,整个系统由不同的功能块构成,例如:

存储器

浮点引擎

存储控制器

总线接口

高速接口

假如考虑处理器和存储器的工作频率为500MHz,带有存储器控制器的浮点引擎的工作频率为666.66MHz,总线接口和高速接口工作频率为250MHz,则该设计具有多个时钟,被视为多个时钟域的设计。

1、多时钟域设计常用方法

如前所述,多个时钟域的处理问题是在传输数据和控制信号时,它对数据完整性有影响。下面的策略在ASIC设计阶段是有用的。

尝试为数据和控制路径优化制定策略。

尝试创建多个时钟域组来定义策略。

在多个时钟域之间传递控制信号时,尝试使用同步器的策略。

尝试使用FIFO和缓存的数据路径同步器来提高数据完整性。

现在讨论重要的跨时钟处理问题与策略及其在多时钟域设计中的使用。

2、多时钟域设计有哪些问题

如果我们考虑适度的门数设计或使用单时钟工作的处理器核心和设计,它可能在布局阶段由于额外的互连延迟而产生时序违例。但是这种设计可能会通过架构、RTL、综合和基于工具的优化调整来满足时序和性能。

现在考虑图中所示的需要多个时钟的设计,让我们试着理解设计中的问题。

1.由于多个时钟域,数据完整性是主要问题,设计需要通过数据完整性检查。

2.没有使用同步器的时钟域边界上的触发器将由于建立和保持违例而存在亚稳态问题。

3.该设计将存在时序违例,并且很难强制时序电路输出进入有效的合法状态。

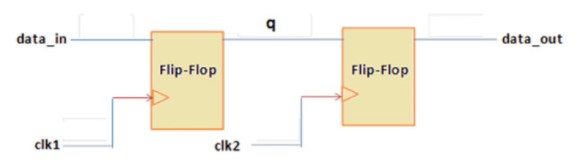

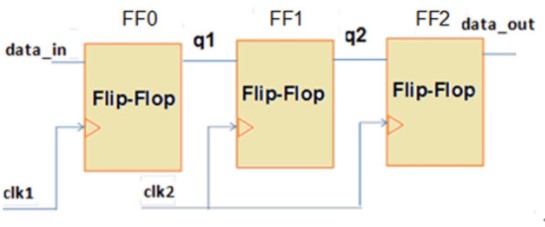

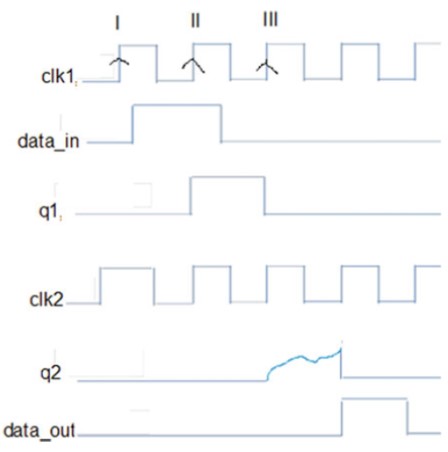

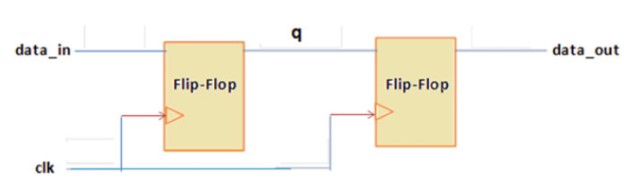

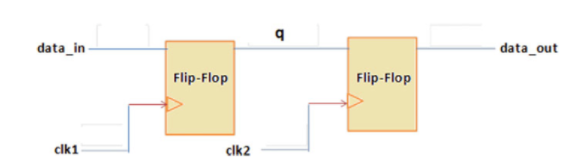

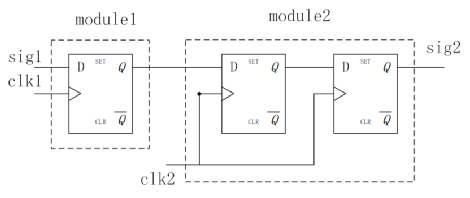

让我们用具有多个时钟域的时序电路来理解上面的内容。由于到达clk1和clk2之间的相差,第二个时钟域的触发器将有建立和保持违例,即触发器输出data_out将是亚稳态的。原因是时钟域1的q输出在clk2活动边的建立和保持窗口期间可能会改变,因此data_out将被迫进入非法状态,即亚稳态。如图1所示。

图1 多时钟域概念

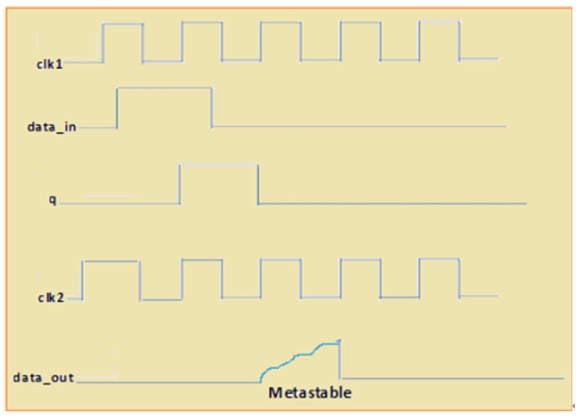

时序如图2所示。

图2 亚稳态输出

3、架构设计策略

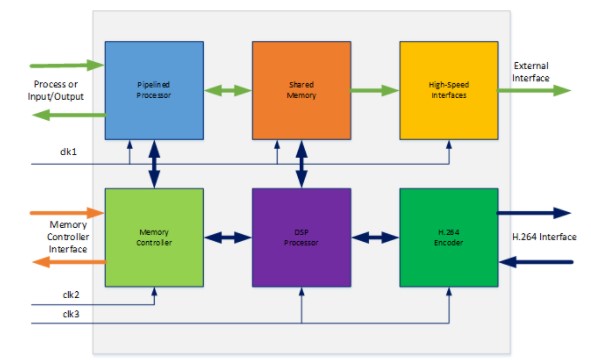

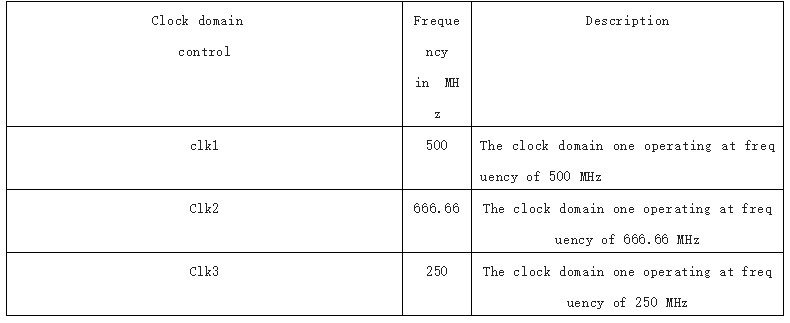

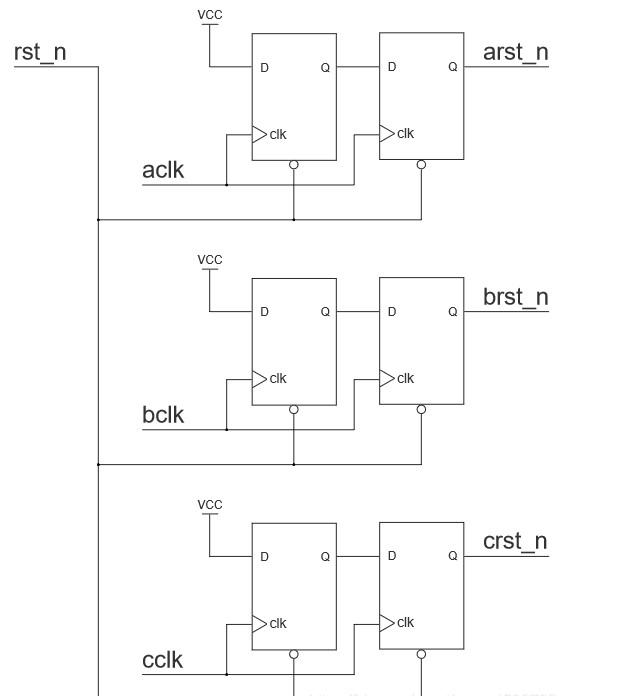

考虑图3中有三个时钟域的设计,表1描述了不同时钟频率下的时钟域信息。

图3 多时钟域架构

表1 多时钟域时钟组

作为一名IC设计人员或架构师,我们需要考虑多个时钟域设计的整体数据完整性检查,并需要为数据路径和控制路径提供干净的时序。

考虑到这一点,我们需要设计同步器来在多个时钟域设计之间传输数据。当在多个时钟域设计之间传递控制信号时,电平、多路复用器和脉冲等同步器是有用的。异步FIFO可以用作同步器,在时钟域和数据路径之间传输数据。

以下是我们在进行多时钟域设计时应该使用的一些准则,以消除CDC错误。

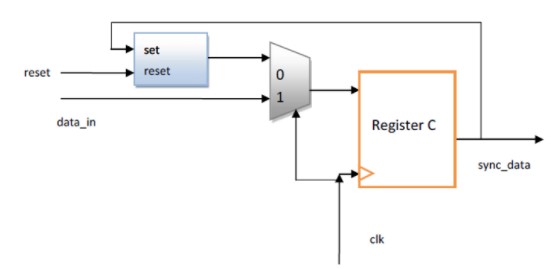

避免亚稳态:在传递控制信号信息时,使用寄存器输出,因为这有助于避免毛刺和冒险。通过在传递控制信号时使用寄存的输出逻辑,可以避免单时钟周期内的多次转换。亚稳态阻塞逻辑如图4所示。

图4 亚稳态阻塞逻辑

使用MCP:强烈推荐多周期路径策略,以避免在多个时钟域之间传递数据和控制信号信息时的亚稳态问题。在MCP中,采用的策略是建立控制和数据对,将具有单比特控制信号的多比特数据从发送时钟域传递到接收时钟域。利用脉冲同步器可以在接收时钟域对控制信息进行采样,并在有或没有同步器的情况下将数据传递到接收时钟域。该技术可以在多个周期内保持数据的稳定值,并且可以利用脉冲同步器产生的同步信号在接收时钟域中采样。跨越时钟域的边界,以下是需要考虑的关键点。

(a)控制信号必须使用多级同步器进行同步。

(b)控制信号应无冒险和毛刺。

(c)应该有跨越时钟边界的过渡。

(d)控制信号应至少稳定一个时钟周期。

MCP策略如图5所示。

图5 MCP策略

采用FIFO:异步FIFO是传递多位控制信号或数据信息的有效技术。在这种技术中,发送时钟域在FIFO未满时将数据写入FIFO内存缓冲区,接收时钟域在FIFO未空时从FIFO缓冲区读取数据。

使用格雷码计数器:在大多数具有跨时钟域(CDC)的ASIC设计中,跨时钟域传递计数器值是至关重要的。如果二进制计数器用于在时钟域边界交换数据,那么由于一个或多个比特的转换,数据转换很容易出错。在这种情况下,建议使用格雷码计数器在跨时钟边界传递数据。在接收端时钟域,采用格雷码到二进制码的转换,将原始数据恢复。

设计分区:在为多个时钟域设计逻辑时,通过使用时钟组对设计进行分区。

时钟命名约定:为了更好地识别时钟源,建议使用时钟命名约定。时钟的命名约定应该由有意义的前缀/后缀支持。例如,发送时钟域使用clk_s,接收时钟域使用clk_r。

同步复位:对于ASIC设计,强烈建议使用同步复位器。

避免保持时间违例:为了避免保持时间违例,建议仔细查看体系结构,并制定在多个时钟周期之间传递稳定数据的策略。

避免丢失相关性:在时钟域边界上,有几种可能导致丢失相关性的方式。比如有:

(a)总线上的多个比特

(b)多个握手信号

(c)不相关的信号

为了避免这种情况,使用时钟意图验证技术,因为这些技术将确保在时钟边界上传递多位信号。

4、控制路径与同步

本节讨论ASIC设计中使用的各种同步器和策略。

电平或多触发同步器

在多个时钟域之间传递的控制信号主要由快时钟域向慢时钟域传递,会出现时序错误,设计中会出现时序违例。因此,在体系结构设计期间,更好的策略是确定多个时钟域设计的接口边界,然后在RTL设计中使用同步器的策略。

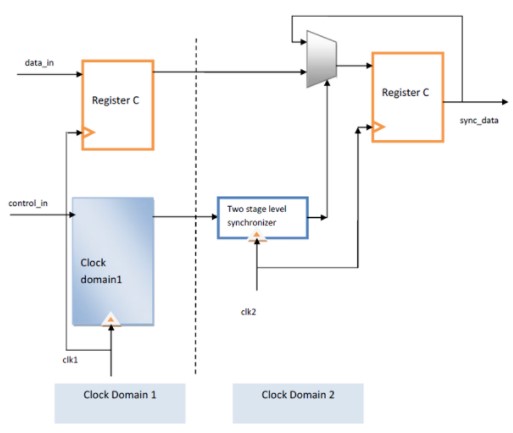

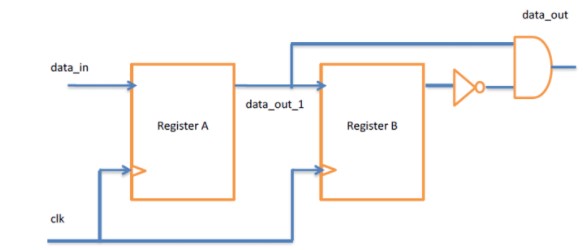

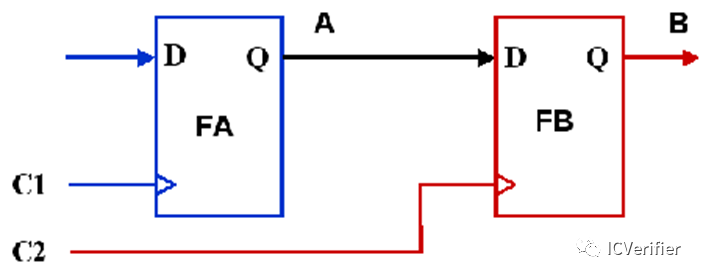

当在多个时钟域之间传递控制信号时,可以通过设计电平同步器(可能使用两个或三个触发器)来解决亚稳态问题。图6使用了两级电平同步器逻辑。

图6 控制路径中有二级电平同步器

如图6所示,利用电平同步器将控制信号q1从时钟域1传递到时钟域2。主要的设计策略是将有效的输出q1传递到第二个时钟域。电平同步器在第二个时钟域,对输出q1进行采样。由于违反了设置或保持时间,第二个时钟域的输入触发器将是亚稳态的,这应该通过设置EDA工具属性来忽略。输出的data_out是有效的数据,由于使用了同步器,本设计有两个时钟的延迟。

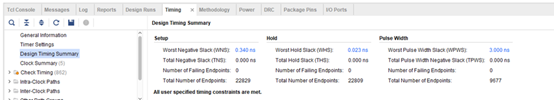

图6所示的设计时序描述如下(图7所示)。

图7 使用两级同步器的时序

如图7所示,q1由第一个时钟域输出。在clk2的上升沿上,触发器FF1的输出q2将由于建立或保持时间违例而进入亚稳态。但是触发器FF2输出在接下来的时钟边是data_out是有效的输出。使用该命令设置false path:

set_false_path –from FF0/q –to FF1/q

使用这两个触发器的电平同步器如图8所示,可以在设计中采用。更好的策略是在RTL设计期间将电平同步器的RTL描述作为单独的模块。引入的延迟取决于将输出驱动到有效合法状态所需的触发器数。

图8 电平同步器

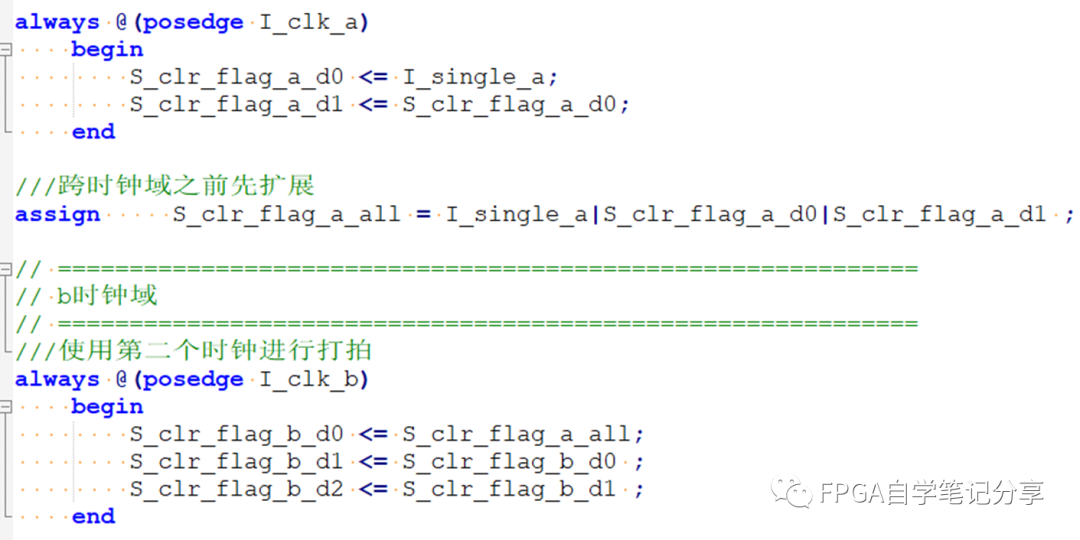

下面将对RTL描述部分进行描述:

always @ (posedge clk)

在ASIC设计中,当控制信息需要从快时钟域传递到慢时钟域时,就会出现数据完整性问题。该问题是由于在将控制信号从时钟域1传递到时钟域2时触发器输出的合法状态不收敛造成的。

利用脉冲展宽器可以解决从快时钟域到慢时钟域的采样问题。工作在正时钟边缘的电平脉冲发生器如图9所示。

图9 电平到脉冲转换

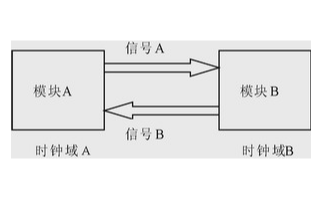

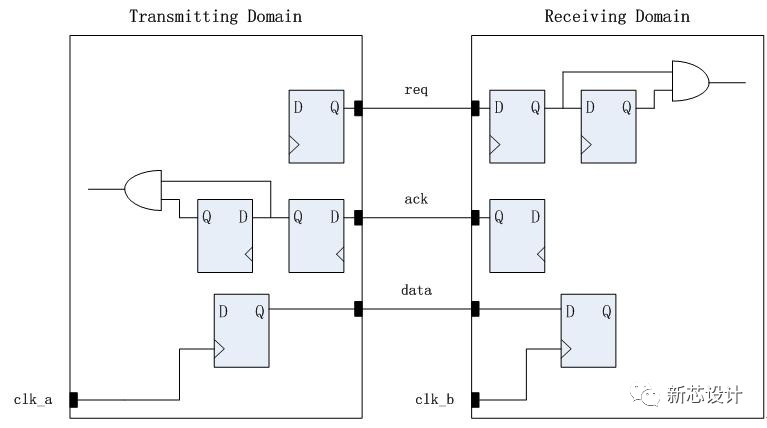

另一种机制是信号的握手,可以用来实现数据的收敛。

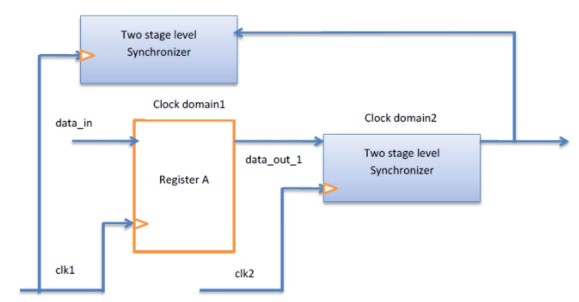

如图10所示,将时钟域2的采样信号作为握手信号反馈到时钟域1。这种握手机制类似于对较快时钟域1的确认或通知,较快时钟域传递的控制信号被较慢时钟域成功采样。在实际的大多数场景中,都采用了这种机制,即使较快的时钟域在收到较慢时钟域的有效通知或确认信号后,也可以发送另一个控制信号。

图10 控制信号的握手机制

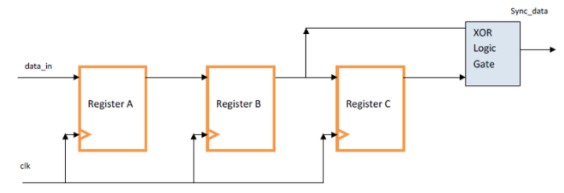

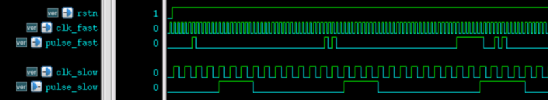

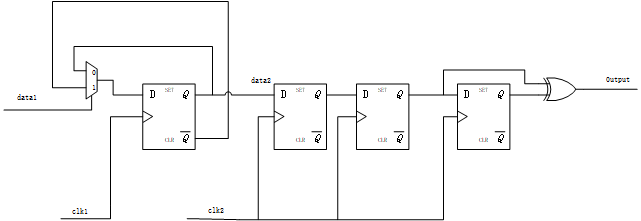

脉冲同步器

这种类型的同步器使用多级电平同步器,其中两级电平同步器的输出由输出触发器采样。这种同步器也称为切换同步器,用于将发送时钟域产生的脉冲同步到目标时钟域。当将数据从较快的时钟域传递到较慢的时钟域时,如果使用两级电平同步器,脉冲可能跳过。在这种情况下,脉冲同步器是有效和有用的。脉冲同步器图如图11所示。

图11 脉冲同步器

Mux同步器

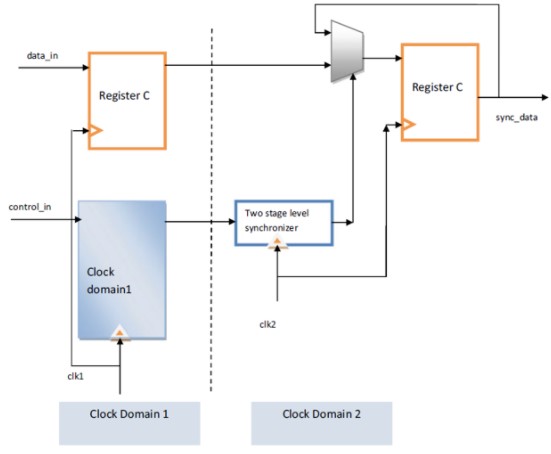

将时钟域1的信息发送到时钟域2时,使用这对数据和控制信号。使用多bit数据和使用单bit控制信号。在接收端,根据发送时钟和接收时钟的比值,使用电平或脉冲同步器为多路复用器产生控制信号。这种技术类似于MCP,并且如果数据在跨越时钟边界的多个时钟周期中是稳定的,则这种技术是有效的。如图12所示。

图12 Mux同步器

5、多bit数据传输的挑战

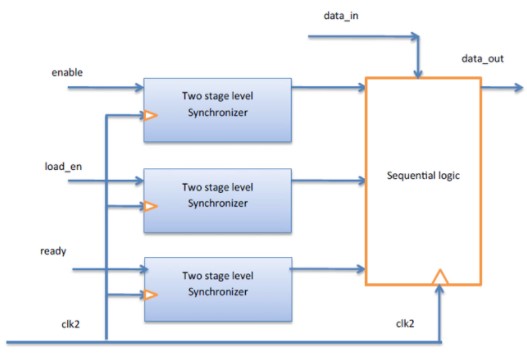

在多个时钟域之间传递多个控制信号是一个重要的挑战。问题是这些控制信号到达的时间不同。如果这些控制信号的到达没有得到正确的管理,那么真正的问题是由于倾斜。考虑图13所示的场景,其中“enable ” “load_en ”和“ready ”需要从一个时钟域传递到另一个时钟域。在这种情况下,如果使用独立的电平同步器,则接收端可能会因为信号的歪斜(信号到达时间不同)而出现同步失败。

图13 对接收端时钟域内的多个信号进行采样

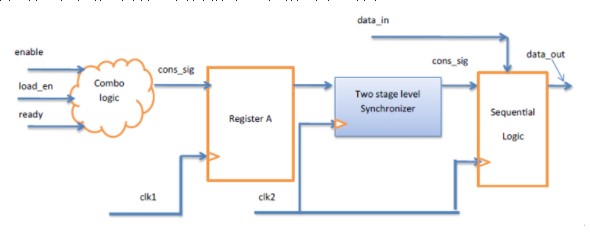

考虑其中一个控制信号,例如enable到达较晚,则控制路径中可能存在同步失败,为了避免这组3个控制信号,尝试在时钟域之间传递共同信号。策略如图14所示。

图14 固定在多时钟域内传递的控制信号

6、数据路径同步

用于在时钟域之间传递多个数据bit的技术是:

握手机制

异步FIFO缓存

格雷编码

握手机制

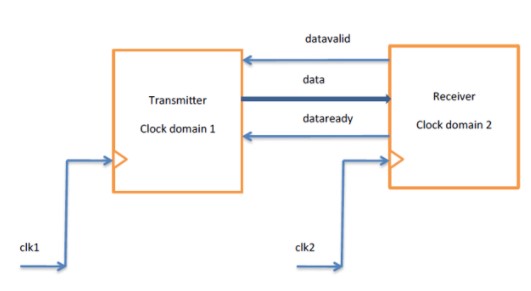

在时钟域之间传递多比特信号时,握手机制的使用是一种有用的技术。如图15所示,发射机工作在clk1,接收机工作在clk2。数据可以从发射机传送到接收机。这里要注意,该握手与AXI总线的握手略有不同。

接收端时钟域可以产生数据有效(data valid)和设备就绪(ready)等握手信号。因此,目的是通知发送器总线上还存在有效数据可用,设备还没有准备好接收新数据。

图15 握手机制框图

握手信号datavalid它是来自时钟域2的主动高电平握手信号,表示传输的数据是有效数据,接收端只需要很少的时钟就可以对该数据进行采样。传输数据时的时钟延迟取决于同步器中使用的触发器的数量,而延迟是握手机制的最大缺点之一。

握手信号deviceready它表明当数据有效的时候,接收端已经准备好接收新数据,并且设备ready好了可以拉高通知发送端将新数据放到数据总线上。

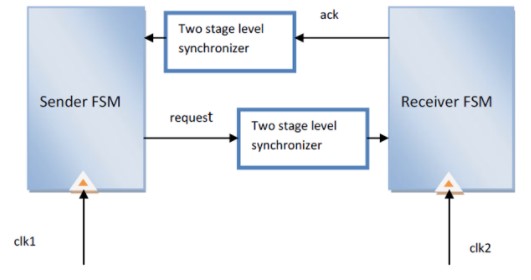

如果我们有多个时钟域的FSM控制器,那么设计架构来通过使用请求(request)和确认(ack)信号建立同步。FSM控制的握手机制如图16所示。

图16 FSM握手机制

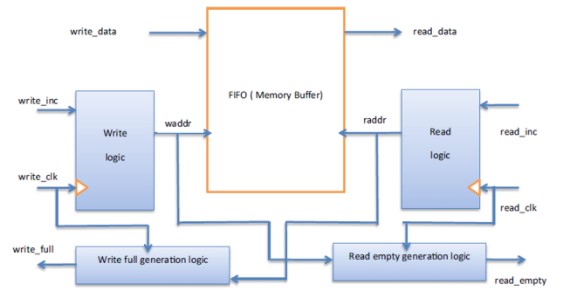

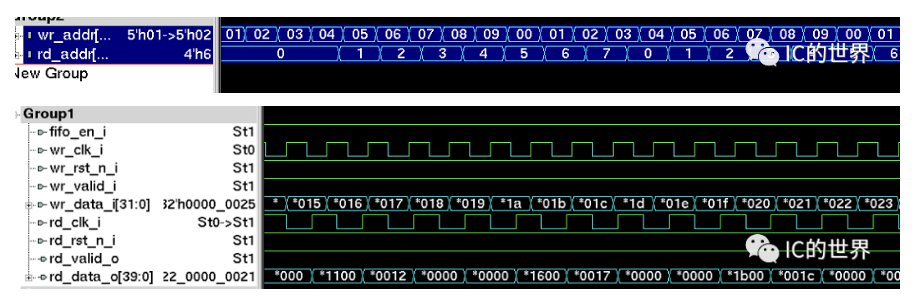

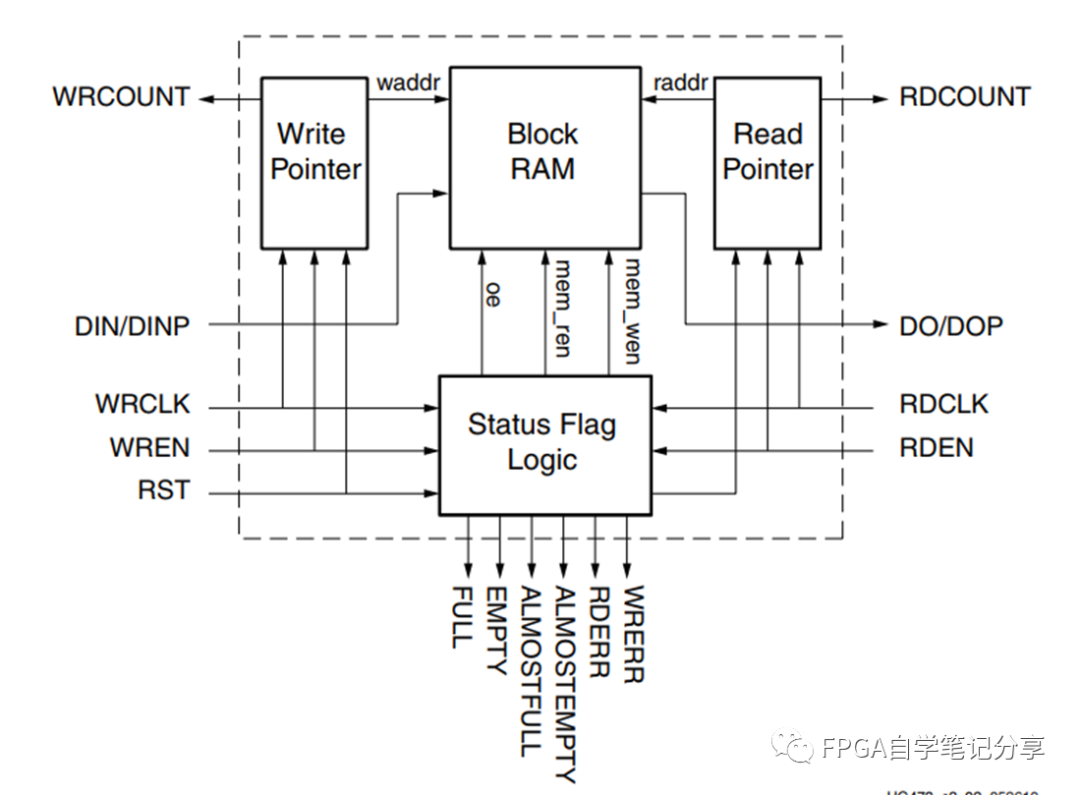

异步FIFO同步器

异步FIFO是有用的,因为数据路径同步器是用来交换多个时钟域之间的数据。如果FIFO内存缓冲区没有满,发送端时钟域或发送端时钟域可以使用write_clk将数据写入FIFO内存缓冲区,如果FIFO内存缓冲区没有空,接收端时钟域可以使用read_clk读取数据(图17)。

FIFO由以下几个块组成:

Memory:内存缓冲区

Write Clock Domain:在write_clk上工作的写时钟域逻辑。

Read clock Domain:读时钟域逻辑,它正在read_clk上工作。

Flag Logic:生成标志逻辑empty和full。

FIFO和相关的逻辑块如图17所示。

图17 FIFO框图

如何得到FIFO的深度?

考虑写时钟域的工作频率为250 MHz,读时钟域的工作频率为100 MHz,没有延迟,然后传输50字节的突发长度,可以使用以下计算:

Write clock time: T1 = 1/250 MHz = 4 ns.

如果指定了读和写延迟,那么尝试修改上面的步骤来获得FIFO的深度。

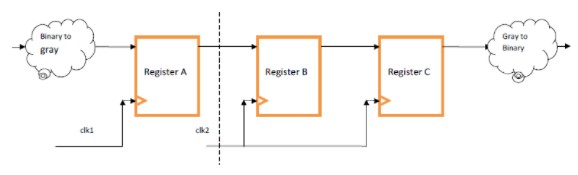

格雷编码

在传递多个位的数据或控制信号时,必须使用格雷编码技术,因为这种技术保证了两个连续的数字只有一bit的变化。例如,如果4bit二进制数据需要在多个时钟域之间传递,那么一个或多个bit转换,因此需要更多的功率和出错的机会。因此,为了避免这种情况,提高性能,在发送端或发送端时钟域采用二进制到格雷码转换逻辑。这保证了在时钟边界上只有一bit变化。为了得到接收端时钟域的原始二进制数据,采用格雷码到二进制码的转换。该技术如图18所示。

图18 格雷编码技术

7、总结

总结几个要点:

在多个时钟域之间传递数据时,设计数据路径同步器。

在多个时钟域之间传递控制信号时,需要设计控制路径同步器。

在通过时钟域传递数据和控制信号信息时,强烈建议使用多周期路径来避免亚稳态问题。

传递多bit控制或数据信息的常用而有效的技术是使用异步FIFO。

对于在多个时钟域之间传递的多位控制信号,采用分组技术来避免由于到达时间不同而产生的歪斜。

审核编辑:刘清

电子发烧友App

电子发烧友App

评论