为什么异步fifo中读地址同步在写时钟域时序分析不通过?

异步FIFO中读地址同步在写时钟域时序分析不通过的原因可能有以下几个方面:

1. 读地址同步在写时钟域时序分析未覆盖完全

在时序分析时,可能只考虑了读地址的同步,而未考虑其他相关的电路。例如,当读地址同步到写时钟域时,需要同时将写指针和读指针的值传递到读时钟域,以便于正确读出数据。如果没有同时同步指针的值,会导致读指针滞后于写指针,出现数据丢失的情况。

2. 时序分析中未考虑时钟插入等问题

在时序分析中,应该考虑到时钟插入等问题。在大多数异步FIFO中,读写指针的传递是通过一系列异步传输门实现的。这可能导致无序的时钟插入,从而使时序分析更加困难。如果未考虑时钟插入等问题,时序分析可能会出现错误。

3. 读时钟域的时钟缓冲问题

在异步FIFO的读时钟域中,由于读地址是同步到写时钟域的,因此需要一个时钟缓冲器将读时钟域的时钟延迟一定时间,以避免读操作在写操作之前发生。如果时钟缓冲器的延迟时间不足,则读操作会滞后于写操作,导致数据丢失。

4. 读写指针的同步问题

在异步FIFO中,读写指针的同步问题是一个关键的问题。由于读地址和写地址是在不同的时钟域中,读操作需要将读指针同步到写时钟域,以便读出正确的数据。如果同步电路设计不当,可能会导致读指针与写指针不同步,从而导致数据丢失或重复读取。

综上所述,异步FIFO中读地址同步在写时钟域时序分析不通过的原因可能是多种多样的,需要从多个方面进行分析和优化。在设计异步FIFO时,应该充分考虑时序问题,同时加强模拟和验证,确保FIFO的正确性和可靠性。

-

时钟缓冲器

+关注

关注

2文章

273浏览量

51956 -

fifo

+关注

关注

3文章

407浏览量

45907

发布评论请先 登录

vivado时序分析相关经验

rt-thread stm32 BSP编译不通过,缺乏HAL库怎么处理?

rt-thread stm32 BSP编译不通过怎么解决?

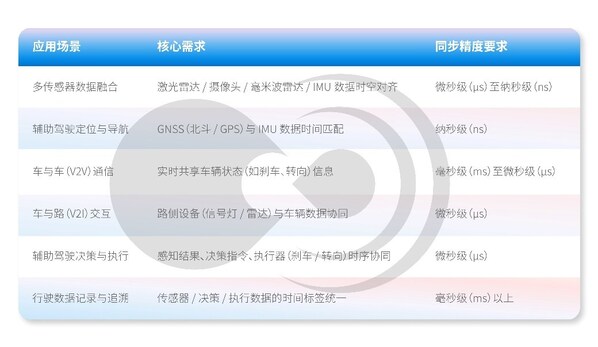

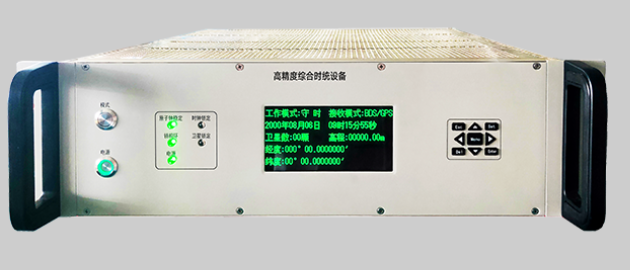

黑芝麻智能跨域时间同步技术:消除多域计算单元的时钟信任鸿沟

【RK3568+PG2L50H开发板实验例程】FPGA部分 | ROM、RAM、FIFO 的使用

cy7c68013a异步slave fifo模式,外部mcu无法读写fifo怎么解决?

跨异步时钟域处理方法大全

为什么异步fifo中读地址同步在写时钟域时序分析不通过?

为什么异步fifo中读地址同步在写时钟域时序分析不通过?

评论