在FPGA设计中,PLL(锁相环)模块作为核心时钟管理单元,通过灵活的倍频、分频和相位调整功能,为系统提供多路高精度时钟信号。它不仅解决了时序同步问题,还能有效消除时钟偏移,提升系统稳定性。本文将深入探讨智多晶PLL在实际应用中的关键注意事项,帮助工程师规避常见设计风险。

2025-06-13 16:37:44 1354

1354

最近是IC相关专业学生找工作的高峰期,大家可以在文章末尾或者知识星球留言讨论笔试或者面试题哦。跨时钟域的处理在面试中常常被问到,今天IC君就来聊一聊这个话题。

2018-09-25 09:39:09 8323

8323 跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。 在本篇文章中,主要

2020-11-21 11:13:01 4997

4997

跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。

2020-11-27 11:11:39 6743

6743

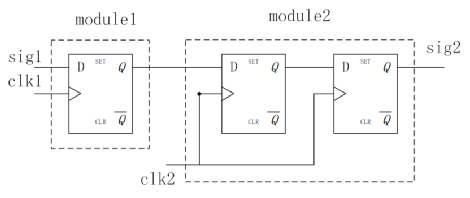

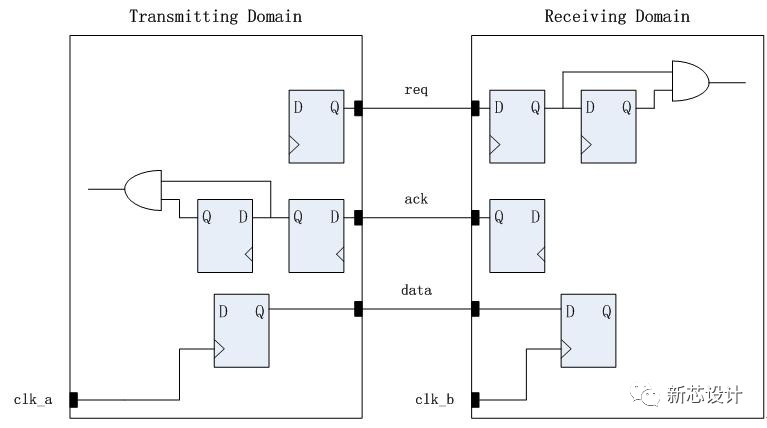

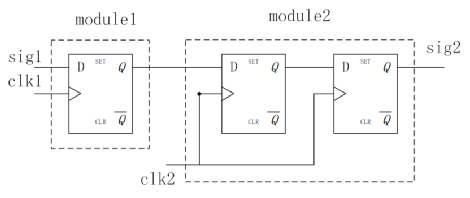

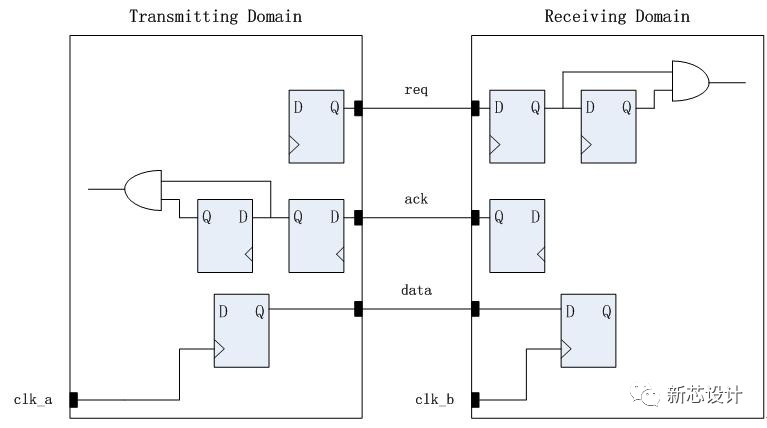

1、跨时钟域与亚稳态 跨时钟域通俗地讲,就是模块之间有数据交互,但是模块用的不是同一个时钟进行驱动,如下图所示: 左边的模块1由clk1驱动,属于clk1的时钟域;右边的模块2由clk2驱动,属于

2020-10-16 15:47:45 1451

1451

我在知乎看到了多bit信号跨时钟的问题,于是整理了一下自己对于跨时钟域信号的处理方法。

2022-10-09 10:44:57 8118

8118 (10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:47:50

FPGA仿真的方法有哪几种FPGA仿真程序的设计方法FPGA仿真的注意事项

2021-04-29 06:15:24

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨时钟域

2021-03-04 09:22:51

请教各位,FPGA在逻辑设计中有哪些注意事项?

2021-05-07 07:21:53

想要做一名做FPGA的工程师 ,请问 FPGA学习及设计中需要注意事项有哪些?

2021-04-02 06:48:15

FPGA的高速接口应用注意事项主要包括以下几个方面:

信号完整性与电磁兼容性(EMC) :

在设计FPGA高速接口时,必须充分考虑信号完整性和电磁兼容性。这要求合理的PCB布局、走线策略和屏蔽技术

2024-05-27 16:02:50

FPGA设计中有多个时钟域时如何处理?跨时钟域的基本设计方法是:(1)对于单个信号,使用双D触发器在不同时钟域间同步。来源于时钟域1的信号对于时钟域2来说是一个异步信号。异步信号进入时钟域2后,首先

2012-02-24 15:47:57

FPGA设计中的时序分析及异步设计注意事项建立时间(setup time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持

2009-12-07 10:14:33

D类放大器散热注意事项PCB的散热注意事项

2021-04-07 07:01:44

Java变量的作用/使用及注意事项Java标识符的作用/使用及注意事项

2020-11-04 06:29:44

PCB设计中有哪些注意事项?

2021-04-25 08:54:19

PLL的好处是什么PLL是什么工作原理PLL的使用技巧?有什么注意事项?

2021-04-23 06:54:07

Pcb抄板的注意事项是什么?

2021-04-26 06:35:49

STM32L151的ADC时钟配置有哪些注意事项?

2022-02-21 07:41:12

TouchGFX怎么使用?有哪些注意事项?

2021-10-14 06:47:30

Vitis准备工程及注意事项

2021-01-25 06:26:20

跨越时钟域FPGA设计中可以使用多个时钟。每个时钟形成一个FPGA内部时钟域“,如果需要在另一个时钟域的时钟域产生一个信号,需要特别小心。隧道四部分第1部分:过路处。第2部分:道口标志第3部分:穿越

2012-03-19 15:16:20

本视频是MiniStar FPGA开发板的配套视频课程,本章节课程根据我们的设计经验,通过三款高云FPGA开发板讲解在使用高云FPGA器件时硬件设计的注意事项。具体内容包括DDR3、HDMI

2021-04-16 17:55:29

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨时钟域

2021-02-21 07:00:00

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。 这里主要介绍三种跨

2021-01-08 16:55:23

异步bus交互(一)— 两级DFF同步器跨时钟域处理 & 亚稳态处理1.问题产生现在的芯片(比如SOC,片上系统)集成度和复杂度越来越高,通常一颗芯片上会有许多不同的信号工作在不同的时钟频率

2022-02-17 06:34:09

如何用Python写Verilog?使用Python MyHDL有哪些注意事项?

2021-06-23 14:10:58

关于cdc跨时钟域处理的知识点,不看肯定后悔

2021-06-21 07:44:12

本期讲解的是PCB设计中处理关键信号的注意事项。一、关键信号的识别关键信号通常包括以下信号:时钟信号(*CLK*),复位信号(*rest*,*rst*), JTAG信号(*TCK*)二、处理关键信号

2017-11-01 17:06:26

变频串联谐振耐压试验装置操作注意事项及接线注意事项有哪些?

2021-10-26 06:38:31

跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨

2020-09-22 10:24:55

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。在本篇文章中,主要

2021-07-29 06:19:11

跨时钟域处理是什么意思?如何处理好跨时钟域间的数据呢?有哪几种跨时钟域处理的方法呢?

2021-11-01 07:44:59

如何升级Recovery?有哪些注意事项?

2022-03-09 06:39:15

如何获取当前RSSI?有什么注意事项?

2021-10-09 09:11:55

如何选择合适的芯片?如何选择蓝牙?有哪些注意事项?

2021-09-27 07:39:51

跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨

2020-10-20 09:27:37

混合信号PCB设计注意事项是什么

2021-04-26 06:24:39

电容降压的原理及注意事项有哪些

2021-03-11 08:19:44

电调驱动原理是什么?有哪些注意事项?

2021-09-24 06:54:01

电路PCB布局注意事项电路PCB布线注意事项

2021-03-01 08:22:41

。StreamCCByToggleWithoutBuffer除了StreamCCByToggle,另一个握手处理跨时钟域的例子便是StreamCCByToggleWithoutBuffer了:粗略一看,切莫以为只是少了一个

2022-07-07 17:25:02

硬件开发流程及注意事项是什么

2021-04-27 06:15:50

示波器探头使用时的注意事项有哪些?

2021-05-08 06:38:39

自制YS13-3荧光管时钟有何注意事项呢?

2022-03-01 07:03:03

芯片热设计有什么注意事项?

2021-04-23 06:25:11

GPIO使用注意事项

2023-06-21 06:03:22

ram使用的注意事项有哪些?

2021-06-23 09:29:50

在中断处理程序中操作寄存器时的注意事项

2020-11-23 14:17:15

购买内存时有哪些注意事项?

2021-06-15 08:42:29

超级电容应用的注意事项看了就明白

2021-03-29 08:17:24

全新一代农药残留检测仪操作的注意事项有哪些【云唐厂·YT-NY24

2021-03-23 10:53:19

胆机使用的注意事项:胆机使用的注意事项

我是初哥, 现在对胆机感兴趣, 但听说胆机使用麻烦, 请问有什么需要注意的?湖南吉首火车站 范增不必担心, 胆机的使用方法

2009-11-29 17:09:11 46

46 PCB激光打标机不宜在哪些场合使用及其操作注意事项随着激光科技的快速发展激光打标机也获得了快速的发展。激光设备标刻技术在各行各业深受追捧,随着市场需求的不断扩大,市场竞争也增强,各行业

2023-08-18 10:00:39

使用方法和注意事项,对于保障工程质量和提高工作效率具有重要意义。下面我们就介绍倾角仪使用的5大注意事项。 1、安装位置:保证倾角仪的安装面与被测物体的安装面

2024-03-28 15:24:56

FPGA设计的注意事项

不管你是一名逻辑设计师、硬件工程师或系统工程师,甚或拥有所有这些头衔,只要你在任何一种高速和多协议的复杂系统中使

2010-04-10 08:34:43 1122

1122 学习FPGA的注意事项,FPGA的基础就是数字电路和HDL语言,想学好FPGA的人,建议床头都有一本数字电路的书,不管是哪个版本的,这个是基础,多了解也有助于形成硬件设计的思想

2011-09-08 17:29:50 1044

1044 跨时钟域信号的同步方法应根据源时钟与目标时钟的相位关系、该信号的时间宽度和多个跨时钟域信号之间的时序关系来选择。如果两时钟有确定的相位关系,可由目标时钟直接采集跨

2012-05-09 15:21:18 63

63 LPC1200系列ARM高频时钟配置注意事项手册下载

2022-03-30 14:46:45 6

6 跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校的本科生,跨时钟域处理也是面试中经常常被问到的一个问题。 在本篇文章中,主要

2017-11-15 20:08:11 14725

14725 这一章介绍一下CDC也就是跨时钟域可能存在的一些问题以及基本的跨时钟域处理方法。跨时钟域的问题主要存在于异步

2017-11-30 06:29:00 8600

8600

基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟域

2018-09-01 08:29:21 6010

6010

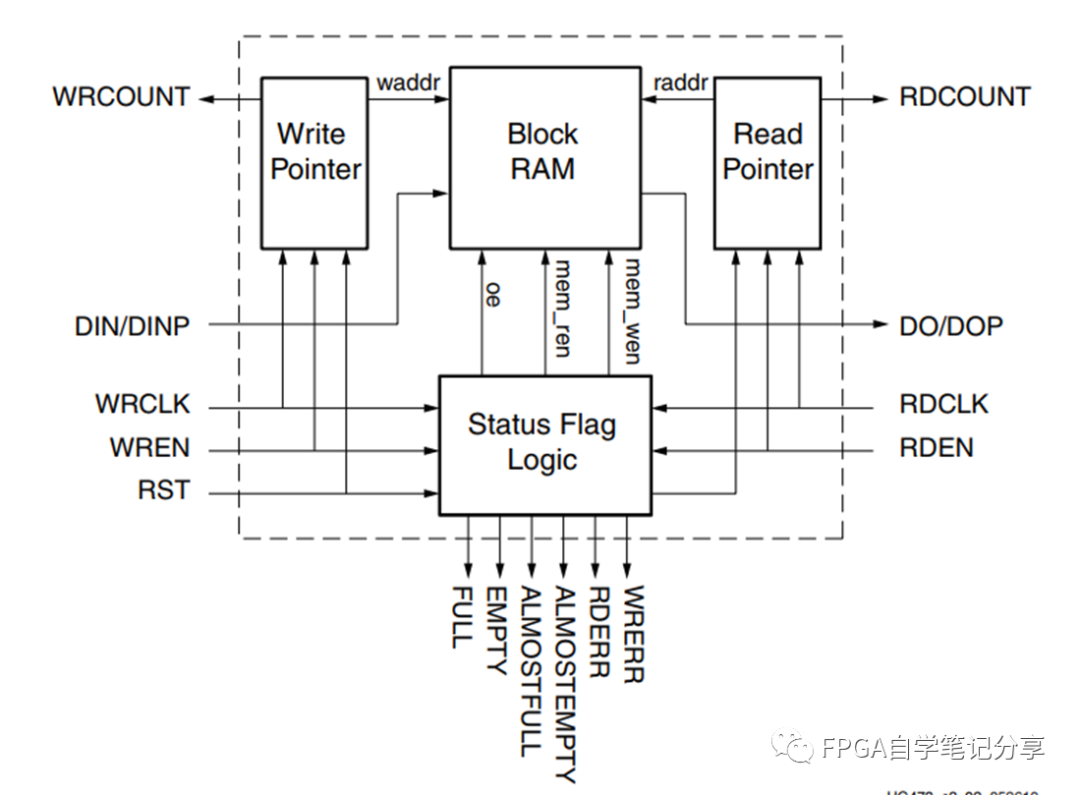

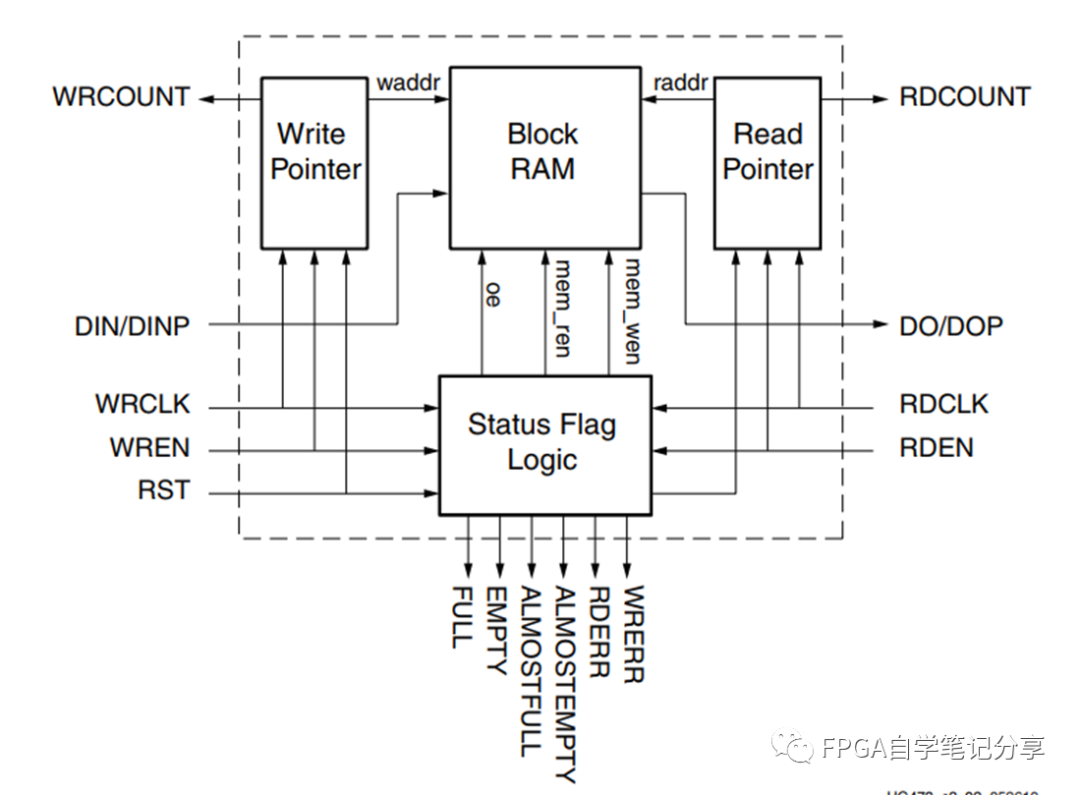

跨时钟域的问题:前一篇已经提到要通过比较读写指针来判断产生读空和写满信号,但是读指针是属于读时钟域的,写指针是属于写时钟域的,而异步FIFO的读写时钟域不同,是异步的,要是将读时钟域的读指针与写时钟域的写指针不做任何处理直接比较肯定是错误的,因此我们需要进行同步处理以后进行比较。

2018-09-05 14:29:36 6636

6636 跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟域的数量急剧增加。通常不止数百个,而是超过一千个时钟域。

2019-08-19 14:52:58 3895

3895 跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。 这里主要介绍三种

2022-12-05 16:41:28 2398

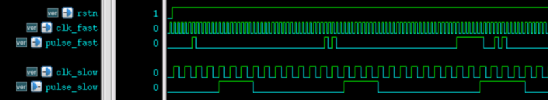

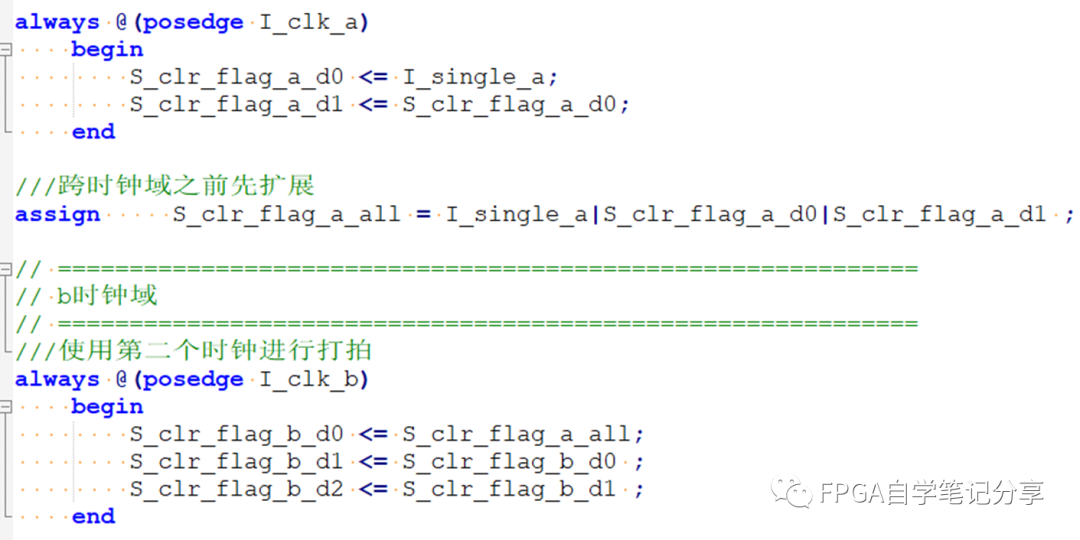

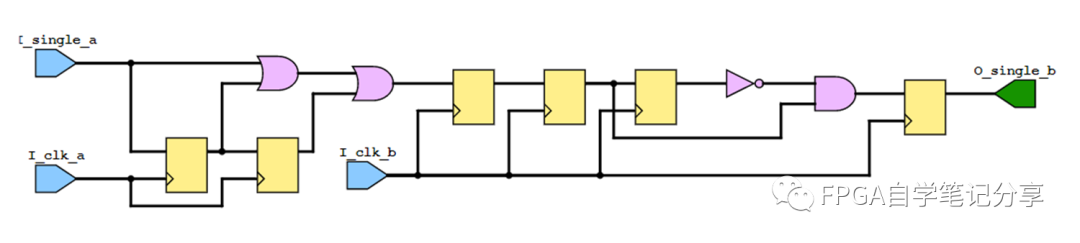

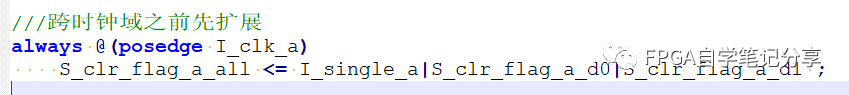

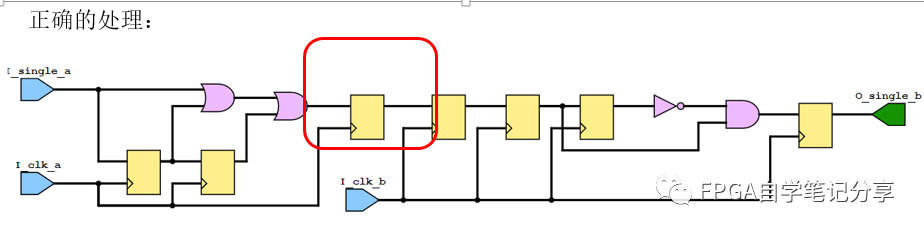

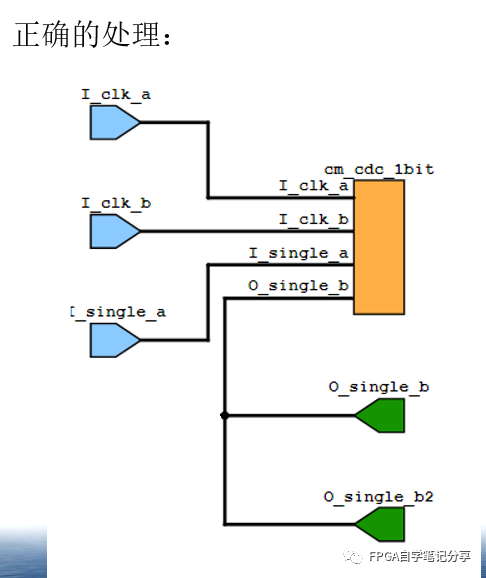

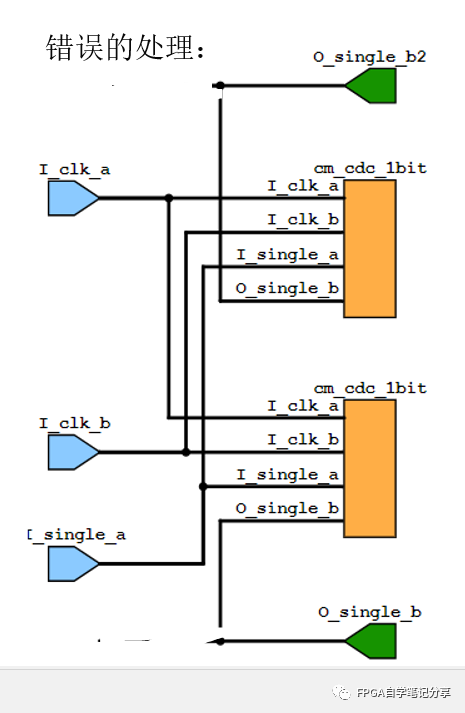

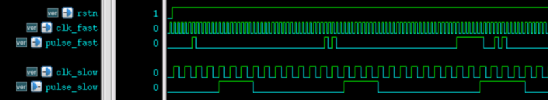

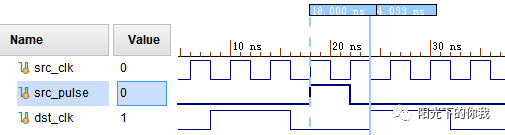

2398 单bit 脉冲跨时钟域处理 简要概述: 在上一篇讲了总线全握手跨时钟处理,本文讲述单bit脉冲跨时钟域的处理为下一篇总线单向握手跨时钟域处理做准备。脉冲同步器其实就是带边沿检测的单bit同步器

2021-03-22 09:54:50 4212

4212 时钟处理两大类,本文以一个总线全握手跨时钟域处理为例解析,单bit和多bit跨时钟处理。这里需要注意是多bit含义比较广泛和总线不是一个概念,如果多个bit之间互相没有任何关系,其实,也就是位宽大于1的单bit跨时钟处理问题,如果多个bit之间

2021-03-22 10:28:12 7550

7550 总线半握手跨时钟域处理 简要概述: 在上一篇讲了单bit脉冲同步器跨时钟处理,本文讲述控制信号基于脉冲同步机制的总线单向握手跨时钟域处理。由于是单向握手,所以比全握手同步效率高一些。 总线半握手

2021-04-04 12:32:00 3675

3675

EE-276:Blackfin®处理器上图像处理的视频框架注意事项

2021-04-13 17:28:26 0

0 每一个做数字逻辑的都绕不开跨时钟域处理,谈一谈SpinalHDL里用于跨时钟域处理的一些手段方法。

2021-04-27 10:52:30 4985

4985

媒体处理器的视频过滤注意事项

2021-05-17 19:06:25 4

4 跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。 在本篇文章中,主要

2021-09-18 11:33:49 23260

23260

问题,不过请注意,今后的这些关于异步信号处理的文 章里将会重点从工程实践的角度出发,以一些特权同学遇到过的典型案例的设计为依托,从代码的角度来剖析一些特权同学认为经典的跨时钟域信号处理的方式。这 些文章都是即兴...

2021-11-01 16:24:39 11

11 (10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 每一个做数字逻辑的都绕不开跨时钟域处理,谈一谈SpinalHDL里用于跨时钟域处理的一些手段方法。

2022-07-11 10:51:44 2797

2797 跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。

2022-10-18 09:12:20 9685

9685 使用注意事项

2023-03-17 20:14:54 1

1 理论上讲,快时钟域的信号总会采集到慢时钟域传输来的信号,如果存在异步可能会导致出现时序问题,所以需要进行同步处理。此类同步处理相对简单,一般采用为延迟打拍法,或延迟采样法。

2023-03-28 13:50:29 2888

2888

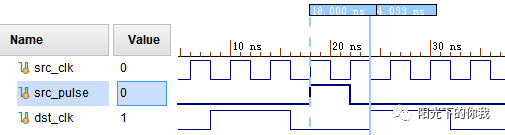

慢时钟域采集从快时钟域传输来的信号时,需要根据信号的特点来进行同步处理。对于单 bit 信号,一般可根据电平信号和脉冲信号来区分。

2023-03-28 13:52:43 1589

1589

单板上时钟的注意事项,主要有以下几个方面可以考虑。

2023-05-09 10:09:15 1907

1907

跨时钟域操作包括同步跨时钟域操作和异步跨时钟域操作。

2023-05-18 09:18:19 1349

1349

跨时钟域是FPGA设计中最容易出错的设计模块,而且一旦跨时钟域出现问题,定位排查会非常困难,因为跨时钟域问题一般是偶现的,而且除非是构造特殊用例一般的仿真是发现不了这类问题的。

2023-05-25 15:06:00 2919

2919

上一篇文章已经讲过了单bit跨时钟域的处理方法,这次解说一下多bit的跨时钟域方法。

2023-05-25 15:07:19 1622

1622

所谓数据流跨时钟域即:时钟不同但是时间段内的数据量一定要相同。

2023-05-25 15:19:15 2725

2725

FPGA多bit跨时钟域适合将计数器信号转换为格雷码。

2023-05-25 15:21:31 3677

3677

编程来校正信号的通信就可以了。在调整FPGA管脚之前必须熟悉几点注意事项。 FPGA管脚调整的注意事项 (1)如图12-1所示,当存在VRN/VRP管脚连接上/下拉电阻时,不可以调,VRN/VRP管脚提供一个参考电压供DCI内部电路使用,DCI内部电路依据此参考

2023-06-20 11:20:01 1626

1626 类似于电源域(电源规划与时钟规划亦是对应的),假如设计中所有的 D 触发器都使用一个全局网络 GCLK ,比如 FPGA 的主时钟输入,那么我们说这个设计只有一个时钟域。假如设计有两个输入时钟,分别给不同的接口使用,那么我们说这个设计中有两个时钟域,不同的时钟域,有着不同的时钟频率和时钟相位。

2023-06-21 11:53:22 4098

4098

CDC(Clock Domain Conversion)跨时钟域分单bit和多bit传输

2023-06-21 14:59:32 3055

3055 在数字电路中,跨时钟域处理是个很庞大的问题,因此将会作为一个专题来陆续分享。今天先来从处理单bit跨时钟域信号同步问题来入手。

2023-06-27 11:25:03 2623

2623

使用注意事项

2023-07-07 19:04:51 0

0 电子发烧友网站提供《FPGA的有源电容器放电电路注意事项.pdf》资料免费下载

2023-07-25 15:06:26 0

0 fpga跨时钟域通信时,慢时钟如何读取快时钟发送过来的数据? 在FPGA设计中,通常需要跨时钟域进行数据通信。跨时钟域通信就是在不同的时钟域之间传输数据。 当从一个时钟域传输数据到另一个时钟域

2023-10-18 15:23:51 1901

1901 对于数字设计人员来讲,只要信号从一个时钟域跨越到另一个时钟域,那么就可能发生亚稳态。我们称为“跨时钟域”即“Clock Domain Crossing”,或CDC。

2024-01-08 09:39:56 1344

1344

电子发烧友网站提供《先进FPGA的电源设计注意事项(电源设计器121).pdf》资料免费下载

2024-08-26 09:27:44 0

0 电子发烧友网站提供《LMK时钟family LVDS输出交流耦合设计注意事项.pdf》资料免费下载

2024-09-27 09:42:08 5

5

电子发烧友App

电子发烧友App

评论